Over-all wiring method for standard units based on optimized time delay and key network techniques

A technology of overall wiring and network technology, which is applied in the field of overall wiring of standard cells, and can solve problems such as inability to reflect circuit overtime, strict constraints on intermediate wiring results, and inability to realize active control, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

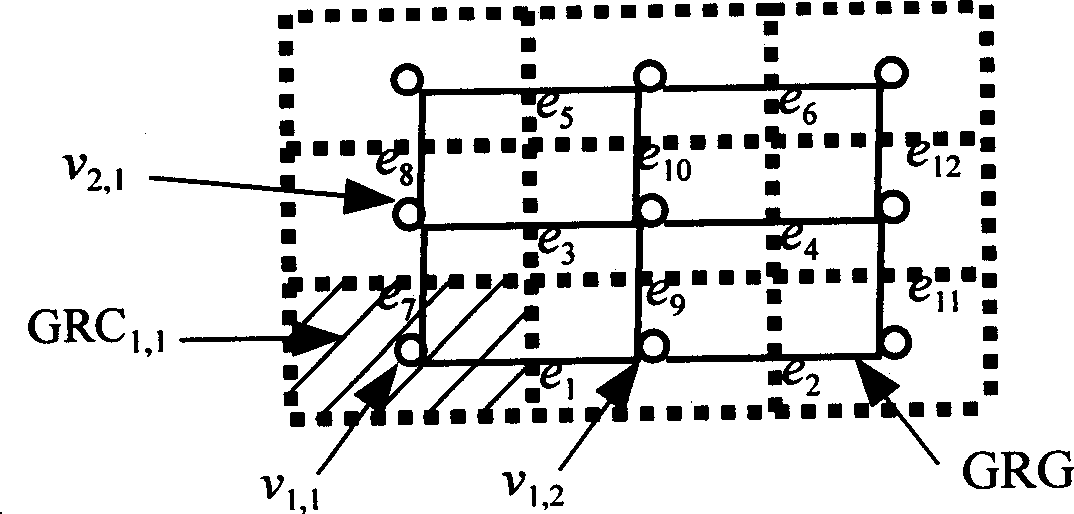

[0062] For the current multi-layer wiring technology in VLSI design, the routing area is no longer a wiring channel between units, but a complete chip plane. The grid method can be used to divide the entire chip plane into several regions called the overall wiring unit GRC according to rows and columns, and then generate the dual graph of the GRC, that is, as figure 1 Shown in the general wiring diagram GRG. GRG by N nr ×N nc nodes and the edges connecting these nodes. with GRC nr,nc The corresponding node v nr,nc The coordinates are GRC nr,nc the center point of . connect two nodes v nr1,nc1 and v nr2,nc2 The edge of is called e k ; l k represents two nodes v nr1,nc1 and v nr2,nc2 The distance between, called e k length; C k represents two nodes v nr1,nc1 and v nr2,nc2 The number of connections of the line network that can pass through the adjacent sides of the corresponding two GRCs is called e k capacity. Therefore, the pin point Pin to be connected in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More