Low power consumption analogue signal sample retaining circuit and its application method

A sample-and-hold circuit and analog signal technology, which is applied to electrical components, electronic switches, biological neural network models, etc., can solve the problem of large circuit power consumption and achieve the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

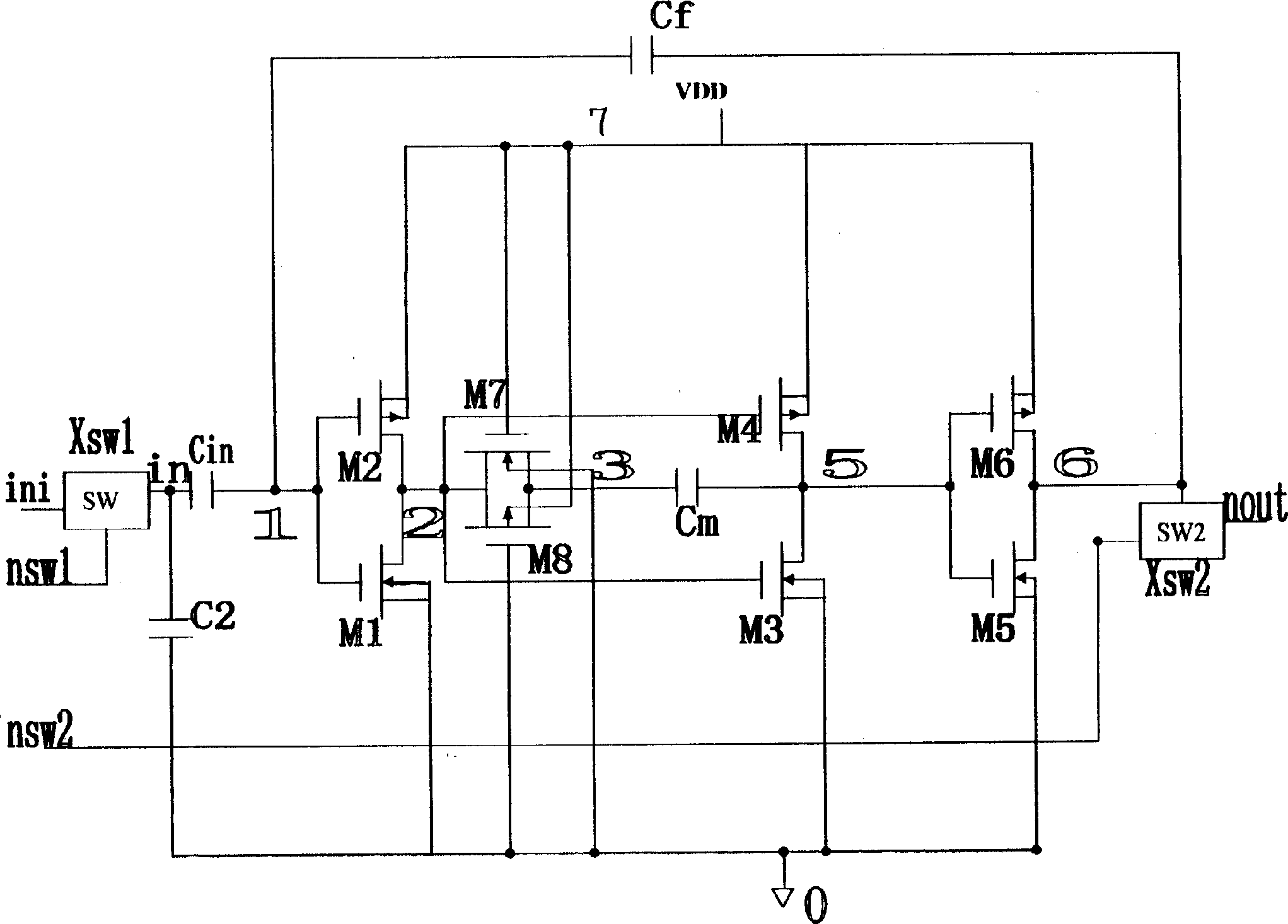

[0019] figure 1 Among them, it is an ordinary three-stage amplified analog signal sampling and holding circuit, Cin is the input terminal capacitance, M1 and M2 form the first-stage amplifying circuit, M3 and M4 form the second-stage amplifying circuit, and M5 and M6 form the third-stage amplifying circuit circuit, Cf is the feedback capacitor.

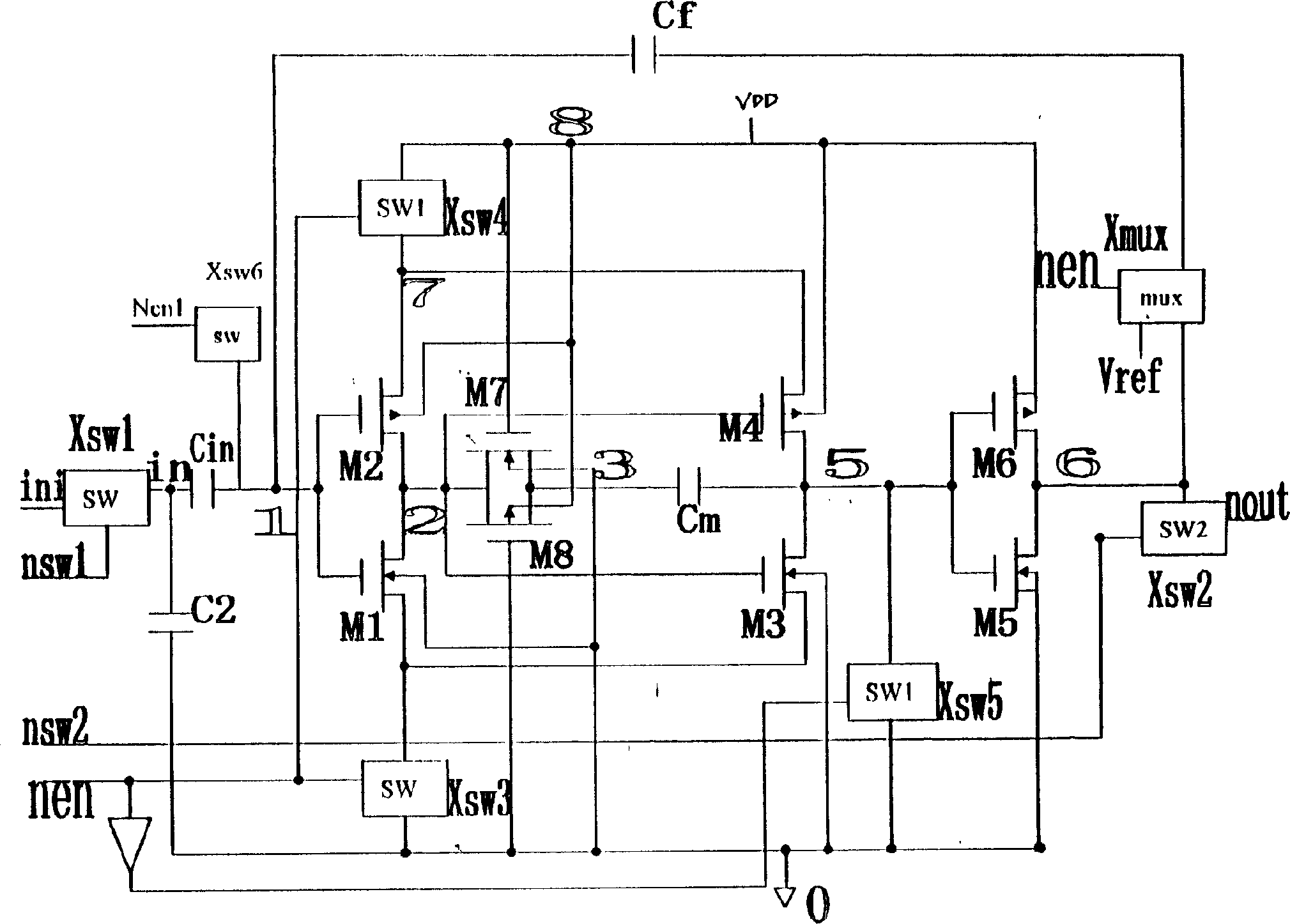

[0020] figure 2 Among them, a low-power analog signal sample-and-hold circuit includes a three-stage amplifier circuit, a sample-and-hold circuit, and three control switches Xsw3, Xsw4, and Xsw5 are added. Xsw4 is connected between the source of the PMOS transistor connected to the power supply and the power supply in each stage of the amplifier circuit before the final stage amplifier circuit, to control the connection and disconnection of the PMOS transistor and the power supply, and Xsw3 is connected to the final stage amplifier circuit. Between the source and the ground of the NMOS transistor connected to the ground in each sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More