Shift register device and display device

A shift register, phase technology, applied in static memory, digital memory information, instruments, etc., can solve problems such as shift register malfunction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0028] Refer to the following Figure 1 to Figure 3 Example 1 of the present invention will be described.

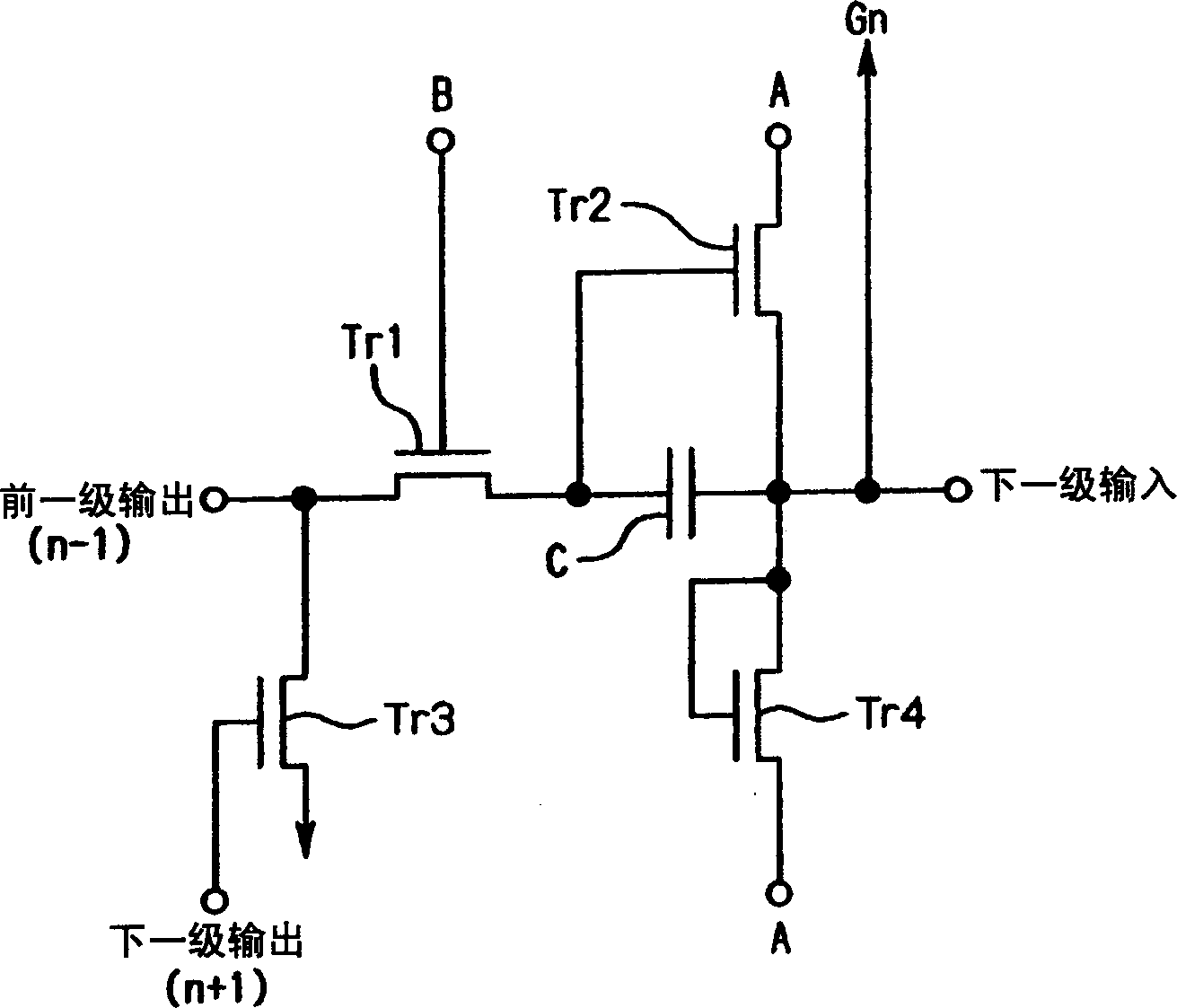

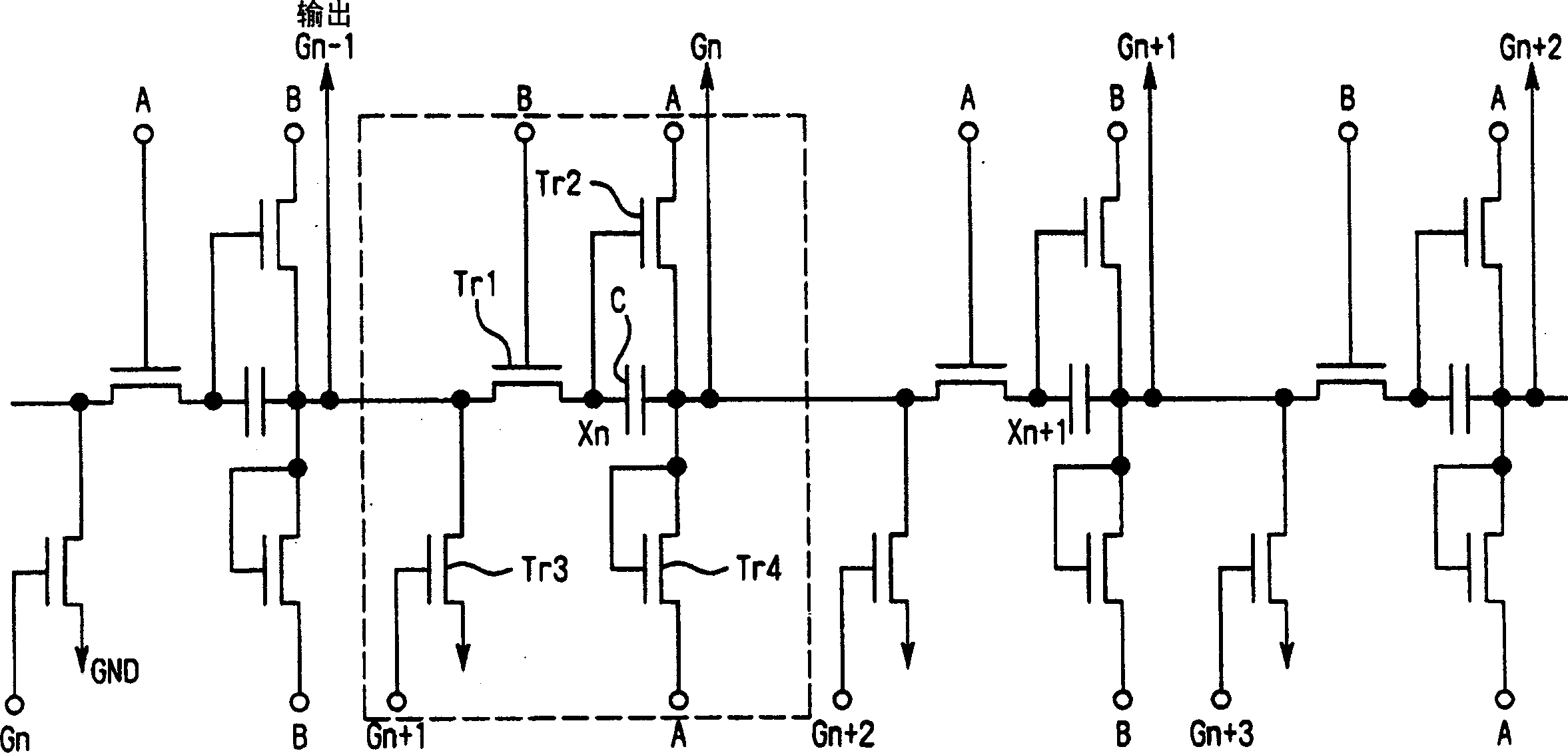

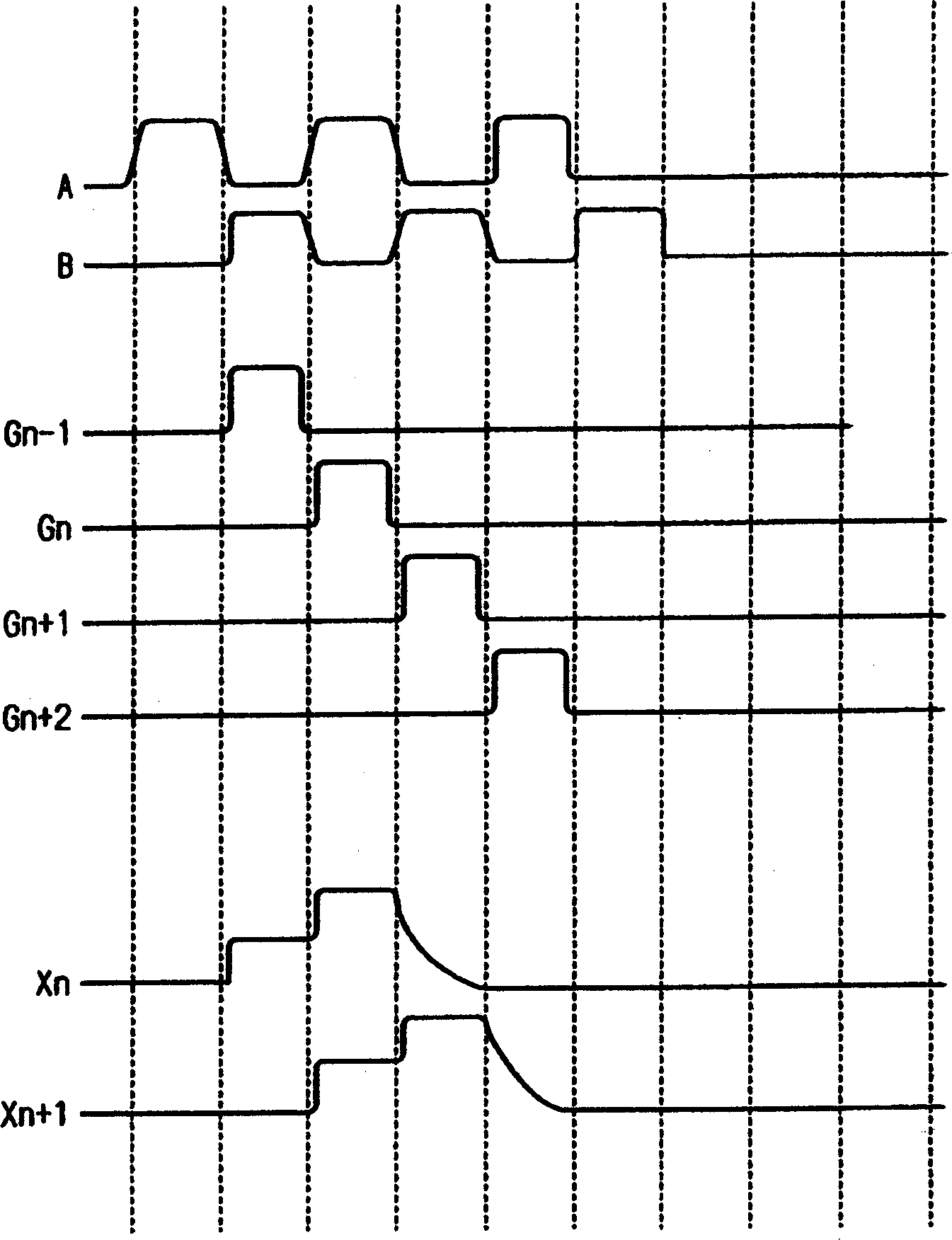

[0029] Figure 1 to Figure 3 is a diagram for explaining the shift register device of this embodiment. This shift register device is composed of a device for generating a plurality of clock signals with sequentially different phases, particularly two-phase clock signals with different phases in this embodiment, and a plurality of cascade-connected stage circuits. in, figure 1 is a circuit configuration diagram of a stage, figure 2 It is a circuit configuration diagram of four stages connected in cascade. image 3 It is a timing chart showing clock signals A, B, output signals Gn-1 to Gn+2, waveform Xn of n-stage control signals, and waveform Xn+1 of n+1-stage control signals.

[0030] Such as figure 1 As shown, each stage circuit is composed of four transistors Tr1~Tr4 and a capacitor C. The input transistor Tr1 is connected to the output of the previous stage,...

Embodiment 2

[0039] Next, an example of a shift register device having a structure in which a plurality of stages are divided into a plurality of modules and a clock signal is sequentially supplied in units of modules will be described. Figure 4 It is a schematic configuration diagram showing the shift register device of this embodiment, and shows an example in which four stages are divided into m modules. Figure 5 is its timing diagram. Since the specific configuration in each stage is the same as that of Embodiment 1, its description is omitted.

[0040] In this embodiment, when the clock control circuit M is driving other modules, all the clock signals of the module are at 'Low' level. That is, if Figure 5 As shown, during the stages S1-S4 of the drive module B1, on the module B1, as described in Embodiment 1, the clock signals A and B are input as the clock signal CK11, while all other modules B2-Bm are 'Low The 'level signals are input as clock signals CKI1 to CKIm.

[0041] Ac...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More