Embedded capacitor structure used for logic integrated cireuit

A capacitive structure and integrated circuit technology, applied in the direction of circuits, capacitors, electrical components, etc., can solve problems such as incompatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Some embodiments of the present invention will be described in detail as follows. However, the invention may be practiced broadly in other embodiments than those described in detail, and the scope of the invention is not limited thereto but rather by the claims.

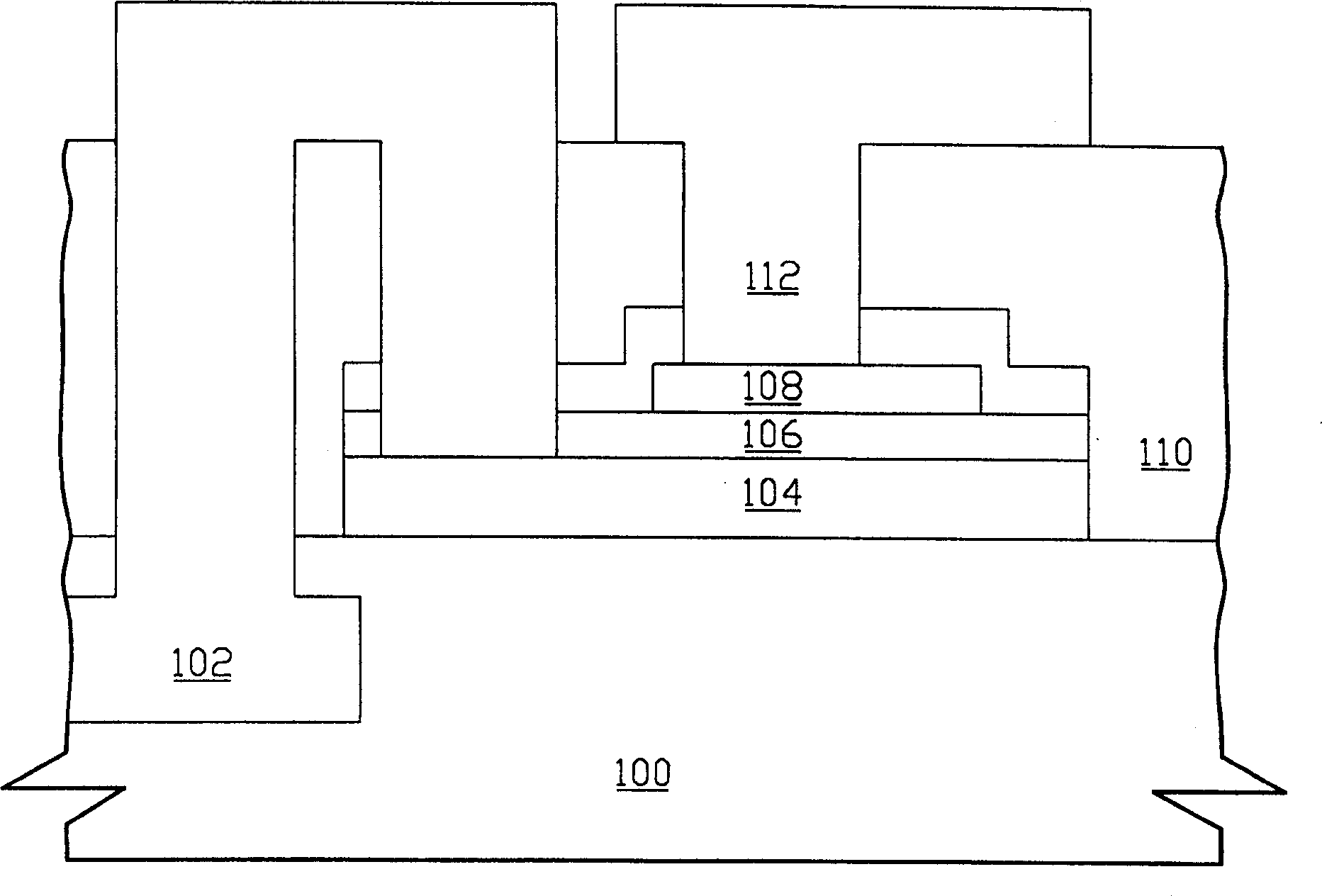

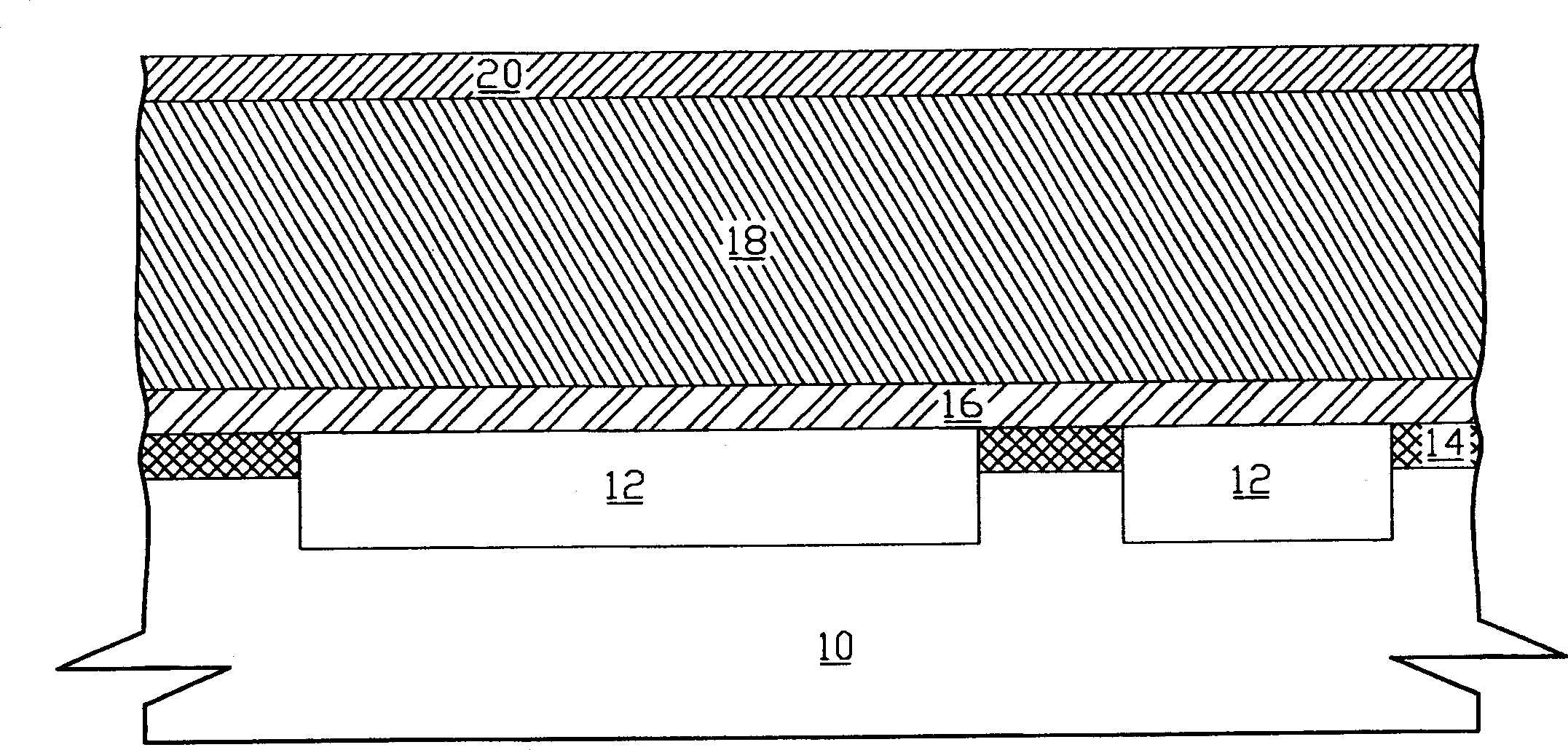

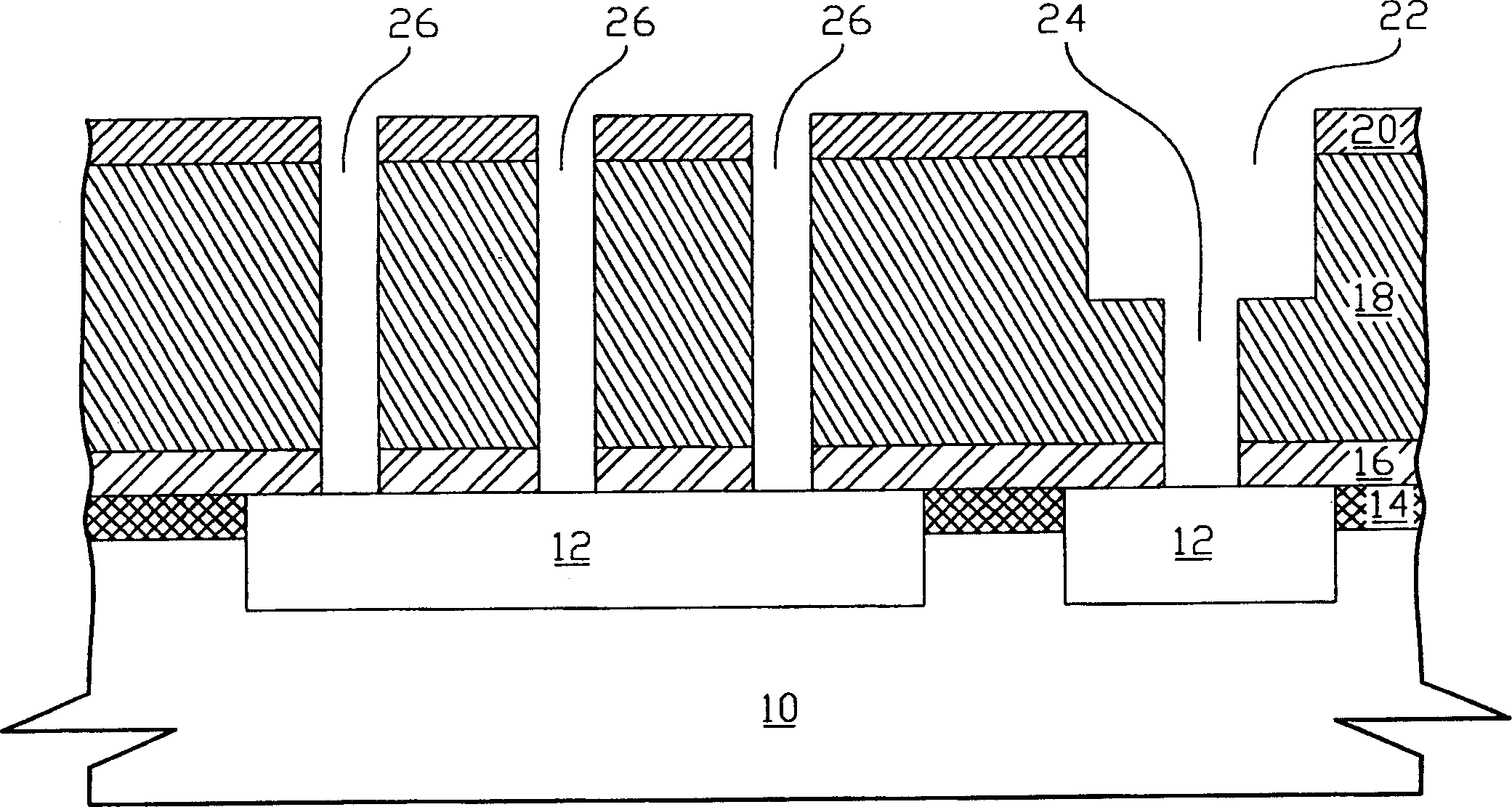

[0020] According to the present invention, a mixed-mode logic integrated circuit element is provided on a substrate, and a vertical three-dimensional metal-insulated metal capacitor structure (vertical three-dimensional MIM capacitor, vertical three-dimensional metal-insulator- metal capacitor structure) and a copper damascene structure (copper dualdamascene structure), wherein the substrate has a previous metal trace and a remaining hard mask layer. In one embodiment of the present invention, part of the previous metal wire is the first metal electrode plate (first metal electrode plate) as a vertical three-dimensional metal-insulated metal capacitor structure, and another part of the previous metal wire is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More