Method for reducing cracking and deformation of copper wire

A copper layer and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of cracks, abnormal opening resistance, stress imbalance, etc., and achieve the effect of cost economy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

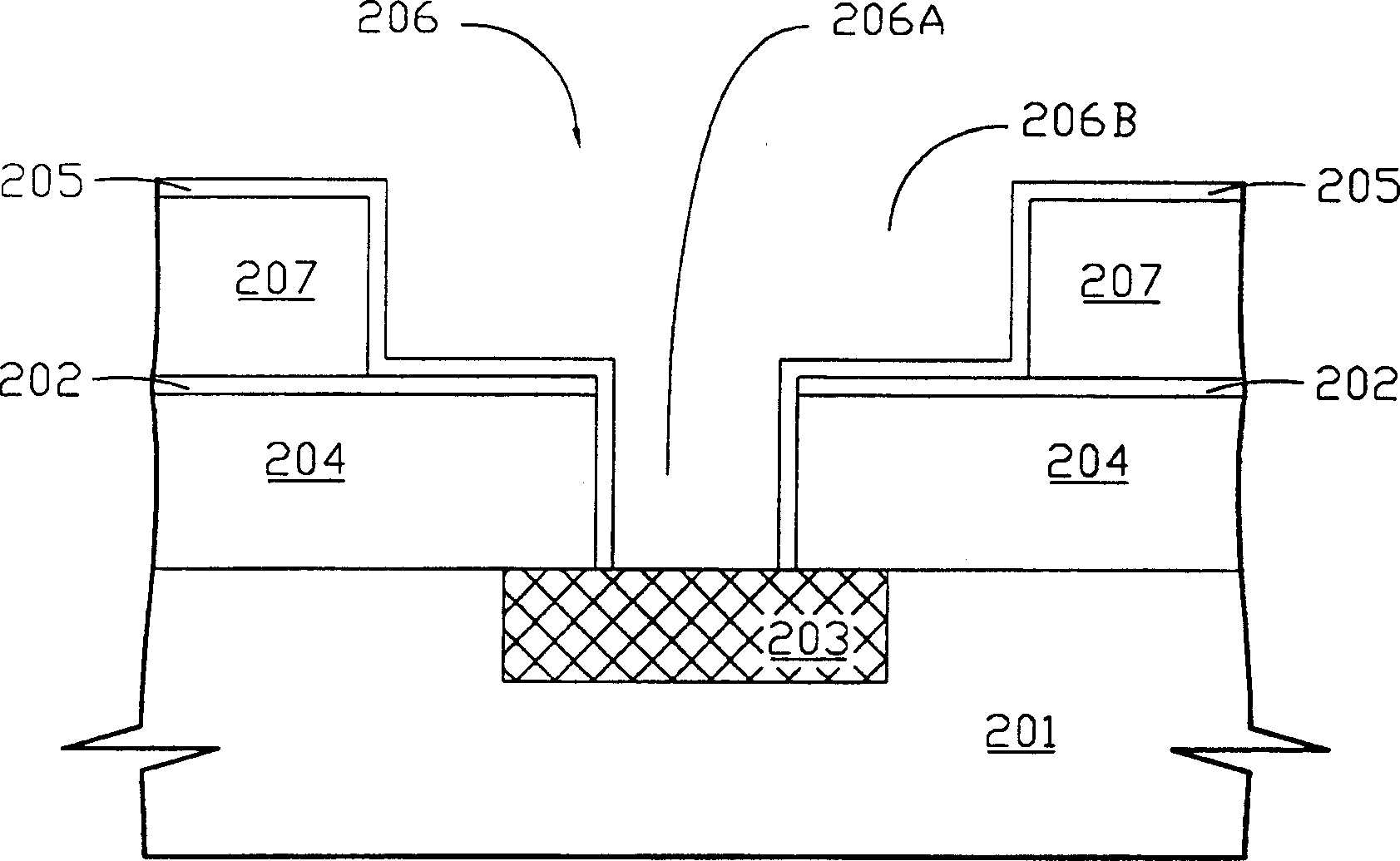

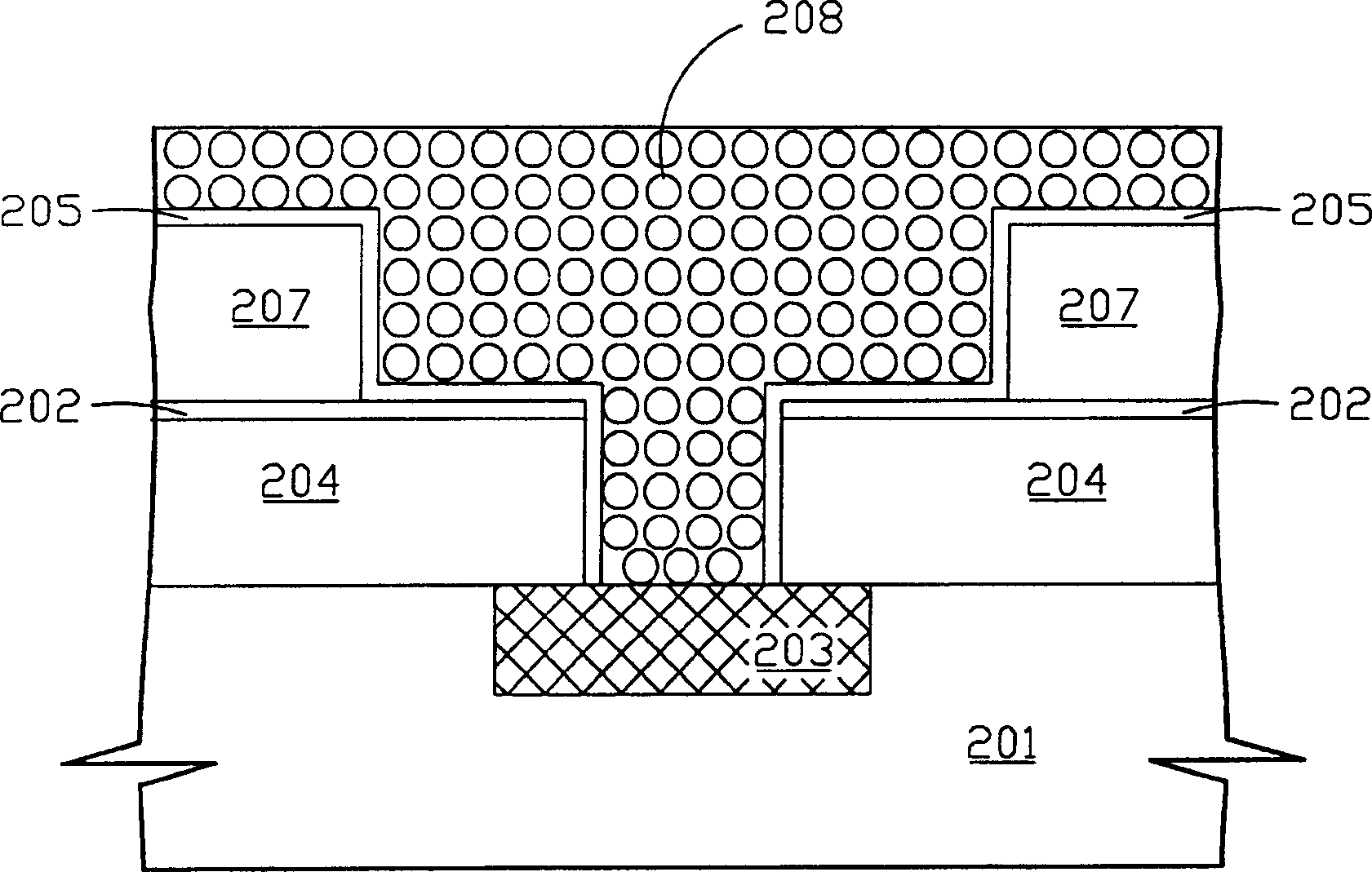

[0031] Preferred embodiments of the present invention will be discussed in detail as follows. The embodiment is used to describe a specific example of using the present invention, but not to limit the scope of the present invention.

[0032] In addition, various parts of the semiconductor device are not drawn to scale. Certain dimensions have been exaggerated compared to other relevant dimensions to provide a clearer description and understanding of the invention.

[0033] Although the embodiments shown here are shown in two dimensions with widths and depths in different stages, it should be clearly understood that the regions shown are only part of a three-dimensional cell of a wafer where the wafer may Contains many unit cells arranged in three dimensions. In contrast, in the manufacture of actual components, illustrated regions have three-dimensional length, width and height.

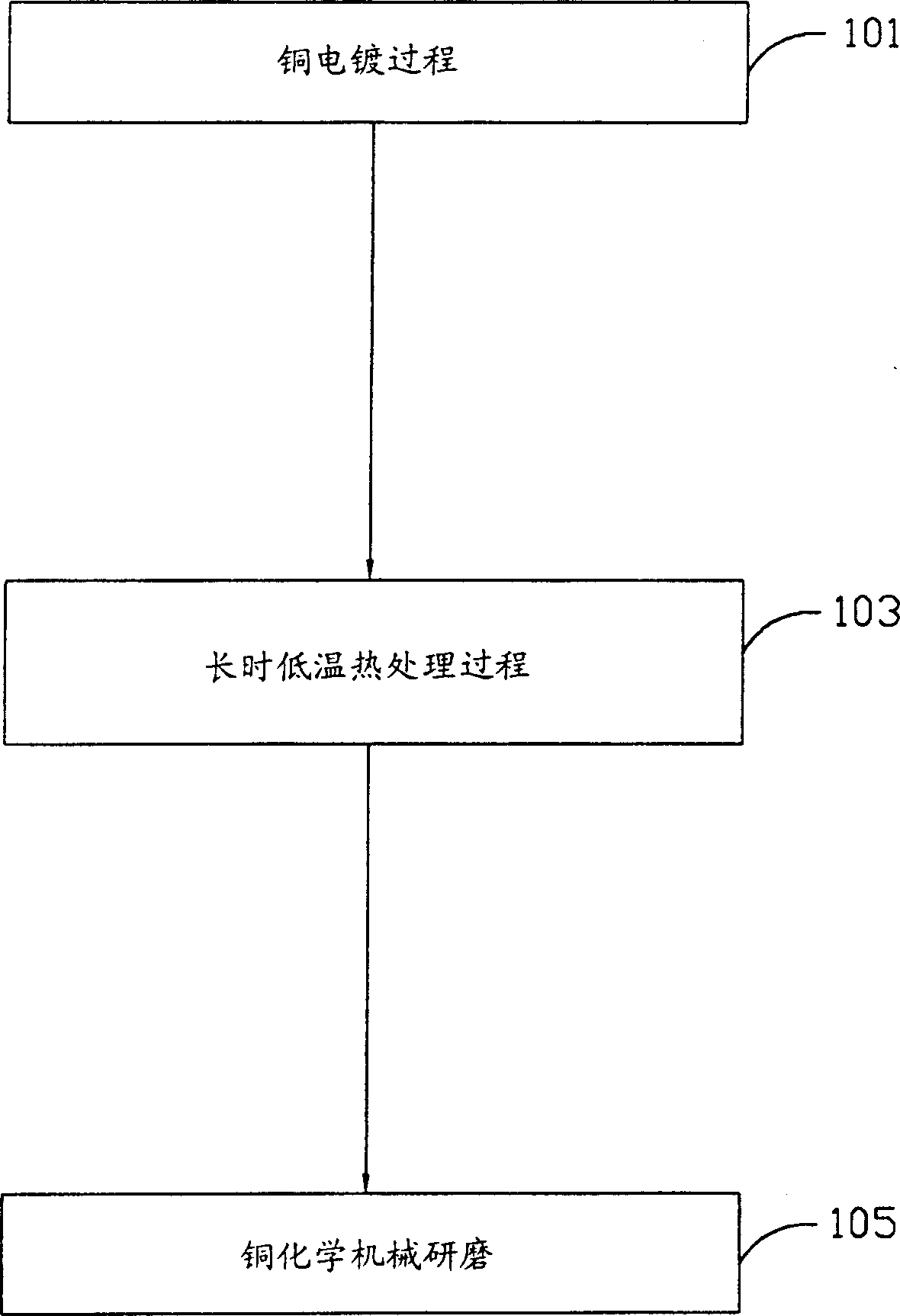

[0034] Figure 4, represents the flow chart of forming the copper interconnection in the pres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More