Semiconductor device and producing method thereof

A manufacturing method and semiconductor technology, applied in the field of diffusion layer, can solve the problems of low-impedance extended diffusion layer, enlargement, difficulty in forming shallow joints, etc., and achieve the effects of shallow extended diffusion layer, shallow resistance, and reduction of redundant point defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

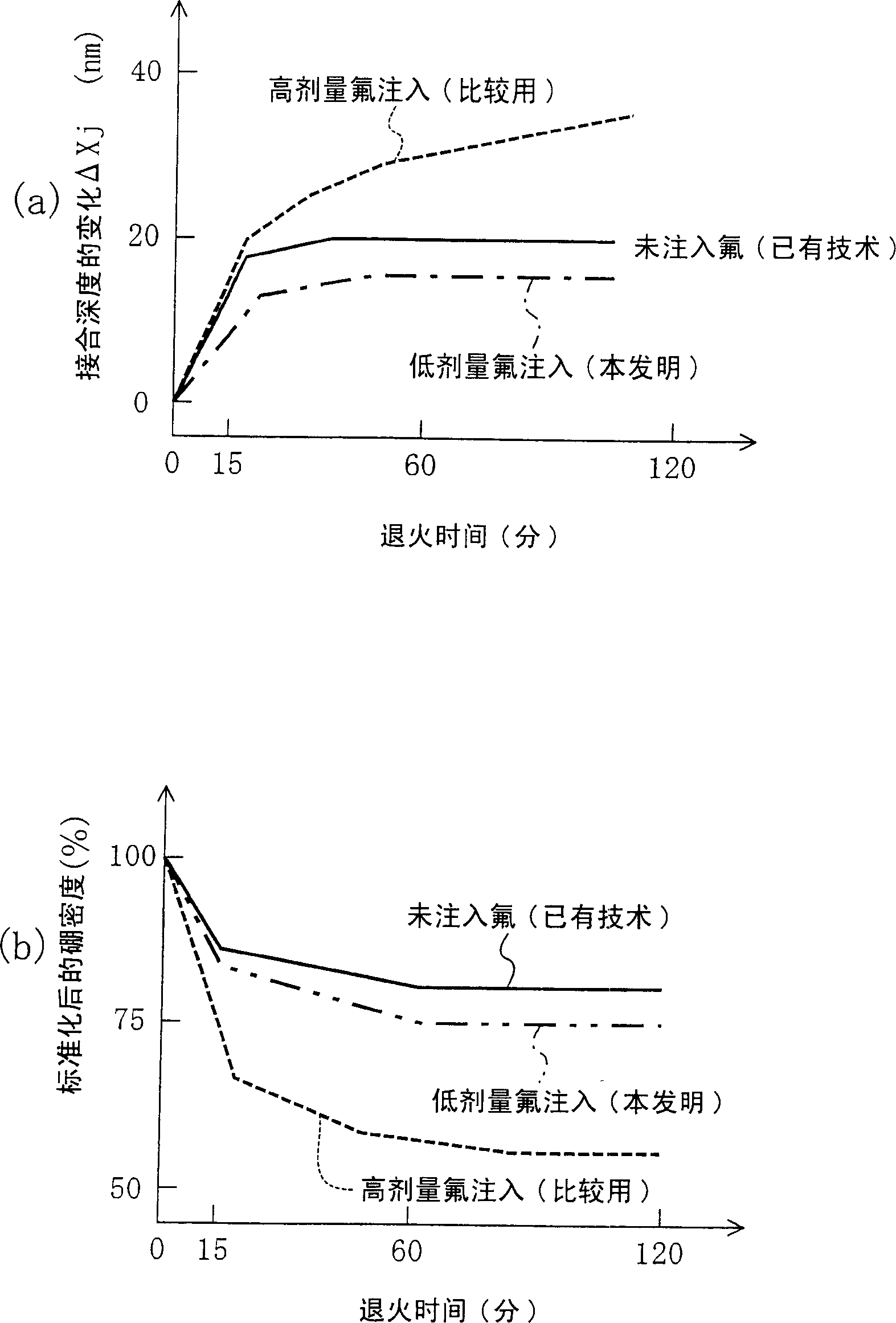

[0046] A first embodiment of the present invention will be described below with reference to the drawings.

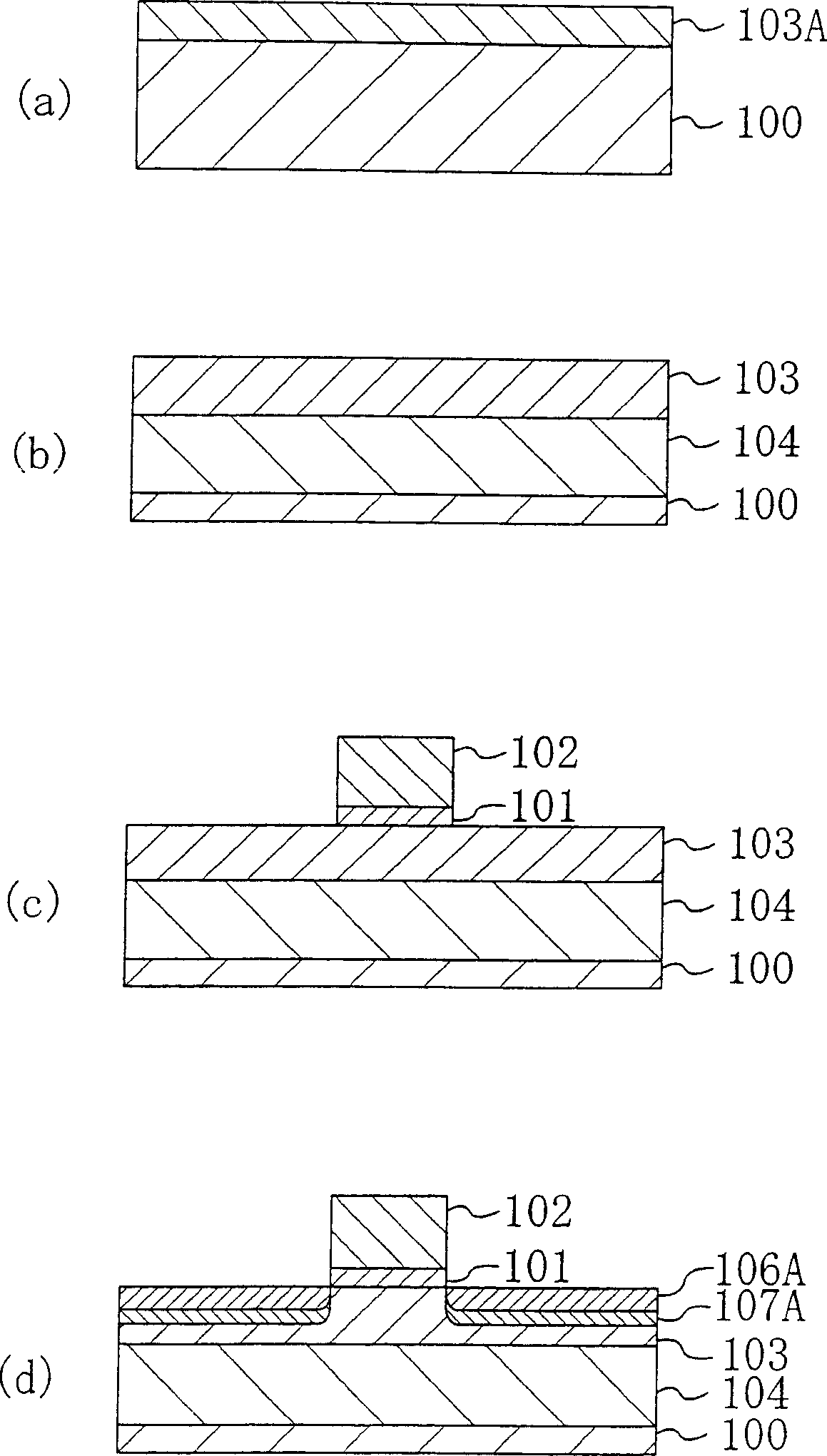

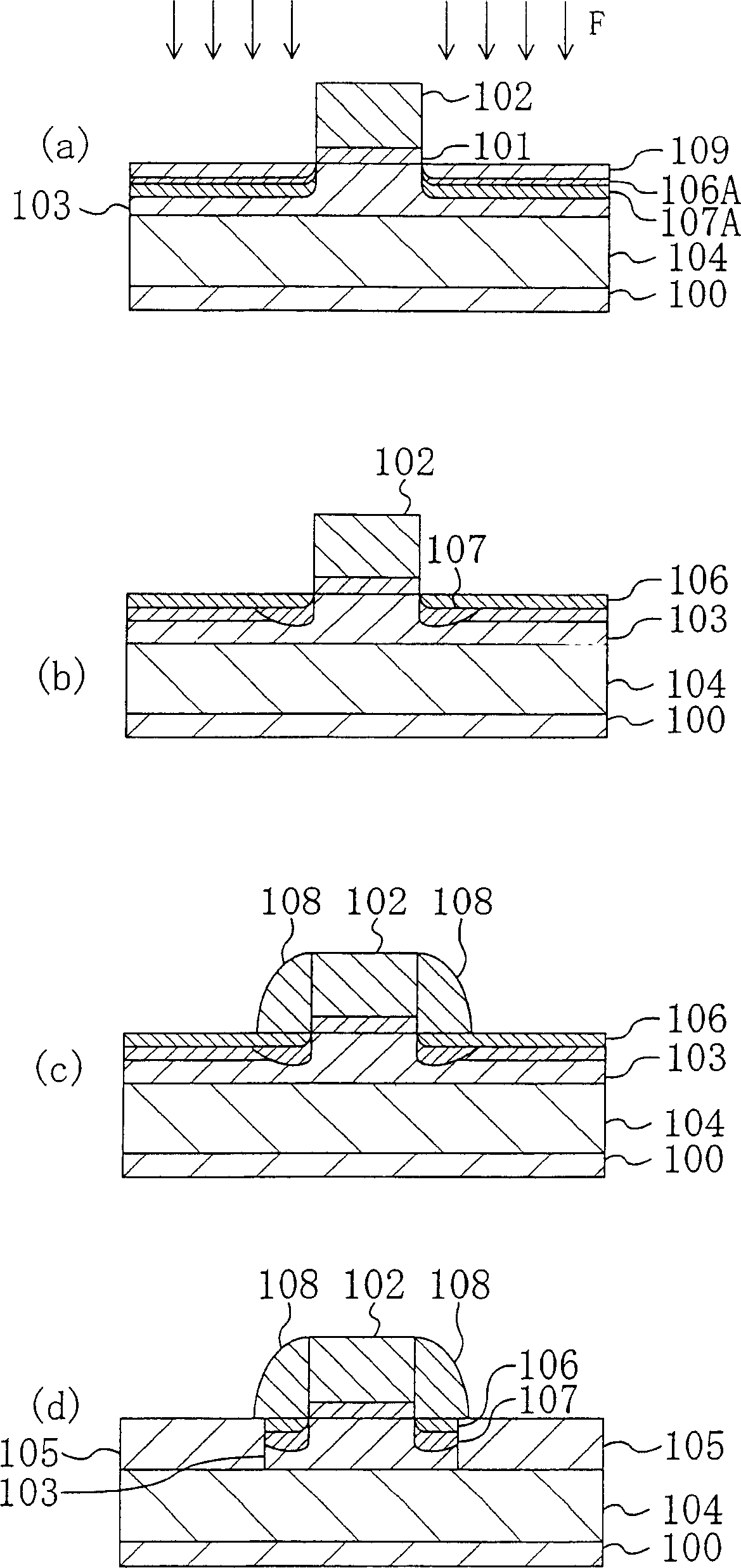

[0047] figure 1 (a)~ figure 1 (d) and figure 2 (a)~ figure 2 (d) A cross-sectional structure showing the sequence of steps in the method for manufacturing a semiconductor device according to the first embodiment of the present invention.

[0048] First, if figure 1 As shown in (a), in the channel formation region of the semiconductor substrate 100 made of P-type silicon, the implantation energy is 140keV and the implantation dose is 5×10 12 / cm 2 Under the implantation conditions of , arsenic (As) ions, which are N-type impurities, are ion-implanted to form an N-type channel implantation layer 103A on the upper portion of the semiconductor substrate 100 . Thereafter, in the N-type well formation region of the semiconductor substrate 100, at an implantation energy of 260 keV and an implantation dose of 1×10 13 / cm 2 Under the first implantation conditions, p...

no. 2 Embodiment

[0070] Hereinafter, a second embodiment of the present invention will be described with reference to the drawings.

[0071] Figure 4 (a)~ Figure 4 (e) and Figure 5 (a)~ Figure 5 (d) A cross-sectional structure showing the sequence of steps of the method for manufacturing a semiconductor device according to the second embodiment of the present invention.

[0072] First, if Figure 4 As shown in (a), by implanting energy at 70keV and implanting dose at 5×10 12 / cm 2 Under certain implantation conditions, arsenic (As) ions, which are N-type impurities, are ion-implanted into the channel formation region of the semiconductor substrate 100 made of P-type silicon, thereby forming an N-type channel implantation in the upper part of the semiconductor substrate 100. Layer 103A. Afterwards, by implanting energy at 260keV and implanting dose at 1×10 13 / cm 2 Under the first implantation conditions of the semiconductor substrate 100, phosphorus (P) ions, which are N-type impu...

no. 3 Embodiment

[0092] A third embodiment of the present invention will be described below with reference to the drawings.

[0093] Figure 7 (a)~ Figure 7 (e) and Figure 8 (a)~ Figure 8 (d) A cross-sectional structure showing the sequence of steps of the method for manufacturing a semiconductor device according to the third embodiment of the present invention.

[0094] First, if Figure 7 As shown in (a), by implanting energy at 70keV and implanting dose at 5×10 12 / cm 2 Under implantation conditions, arsenic (As) ions are ion-implanted as an N-type impurity into the channel formation region of the semiconductor substrate 100 made of P-type silicon, thereby forming an N-channel implantation layer 103A on the upper portion of the semiconductor substrate 100. . Afterwards, by implanting energy at 260keV and implanting dose at 1×10 13 / cm 2 Under the first implantation conditions of the semiconductor substrate 100, phosphorus (P) ions, which are N-type impurities, are ion-implanted ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More