Boundary scan testing device for integrated circuit

A technology of boundary scan testing and integrated circuits, applied in the direction of measuring devices, measuring electricity, measuring electrical variables, etc., can solve problems such as expensive, difficult to promote, complex structure, etc., achieve low cost, easy to promote, and improve the pass rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The specific implementation manner of the present invention will be described below in conjunction with the accompanying drawings.

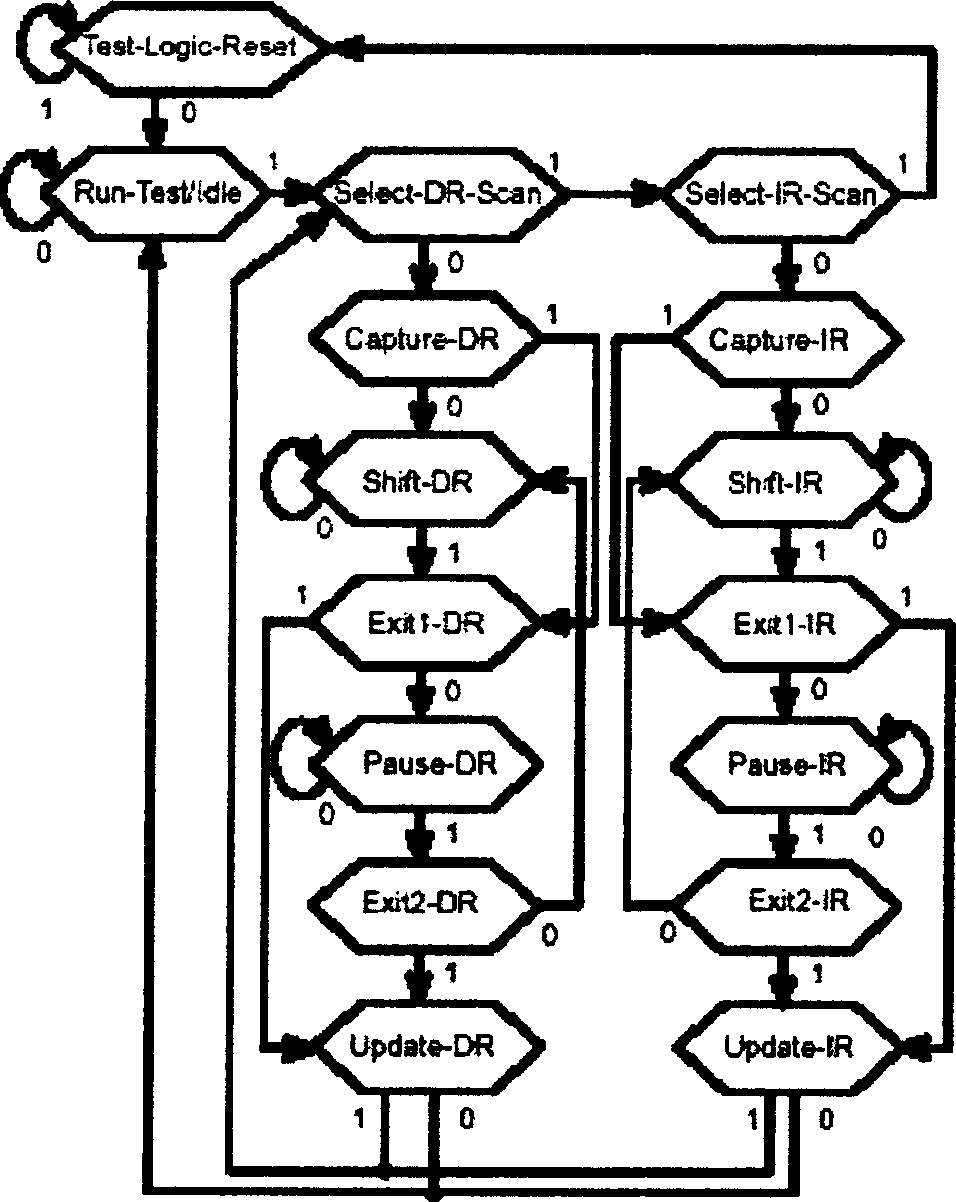

[0019] figure 1 It is the state flow diagram of the TAP controller defined by IEEE 1149.1. It is the principle basis of the present invention.

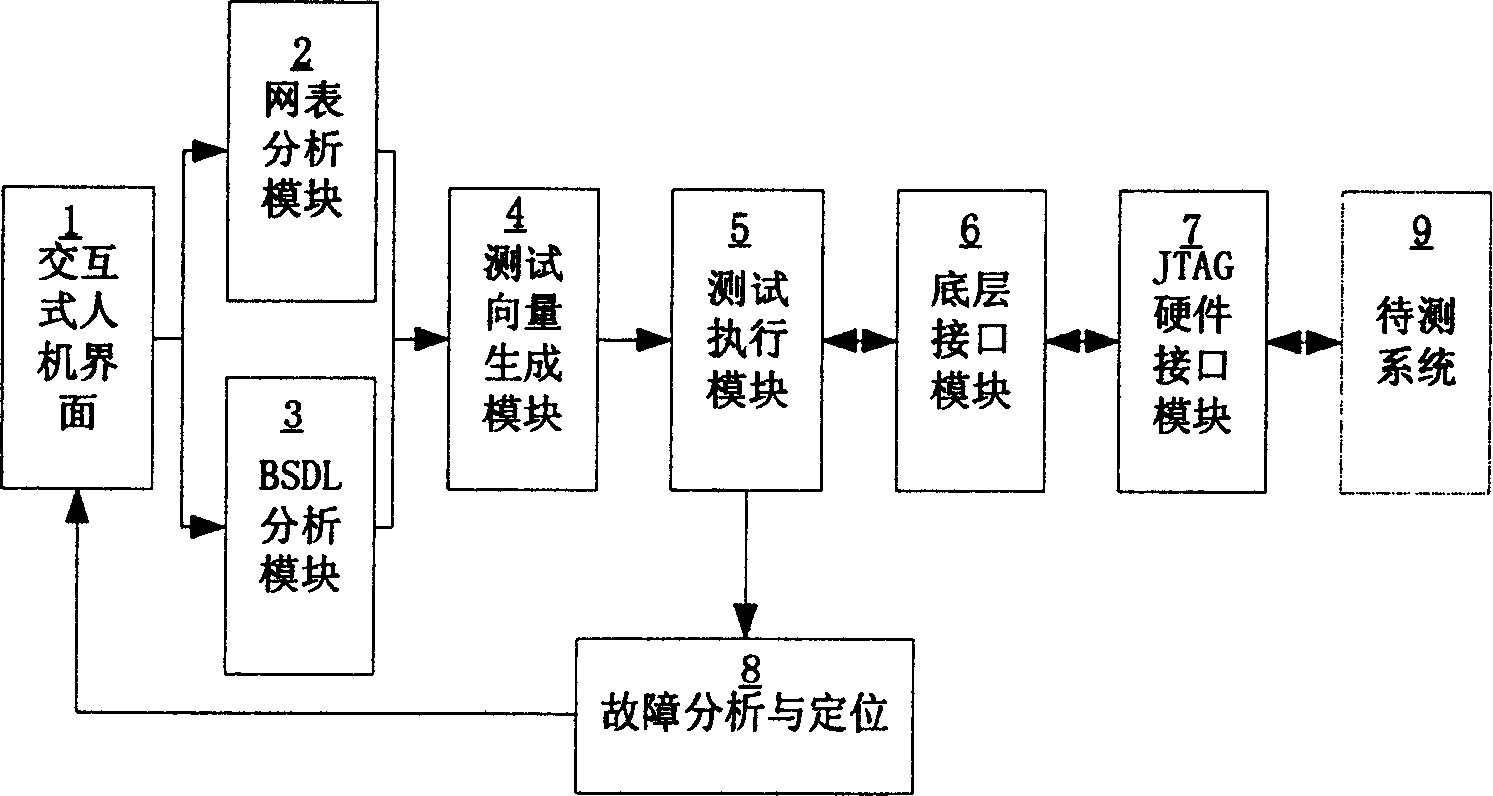

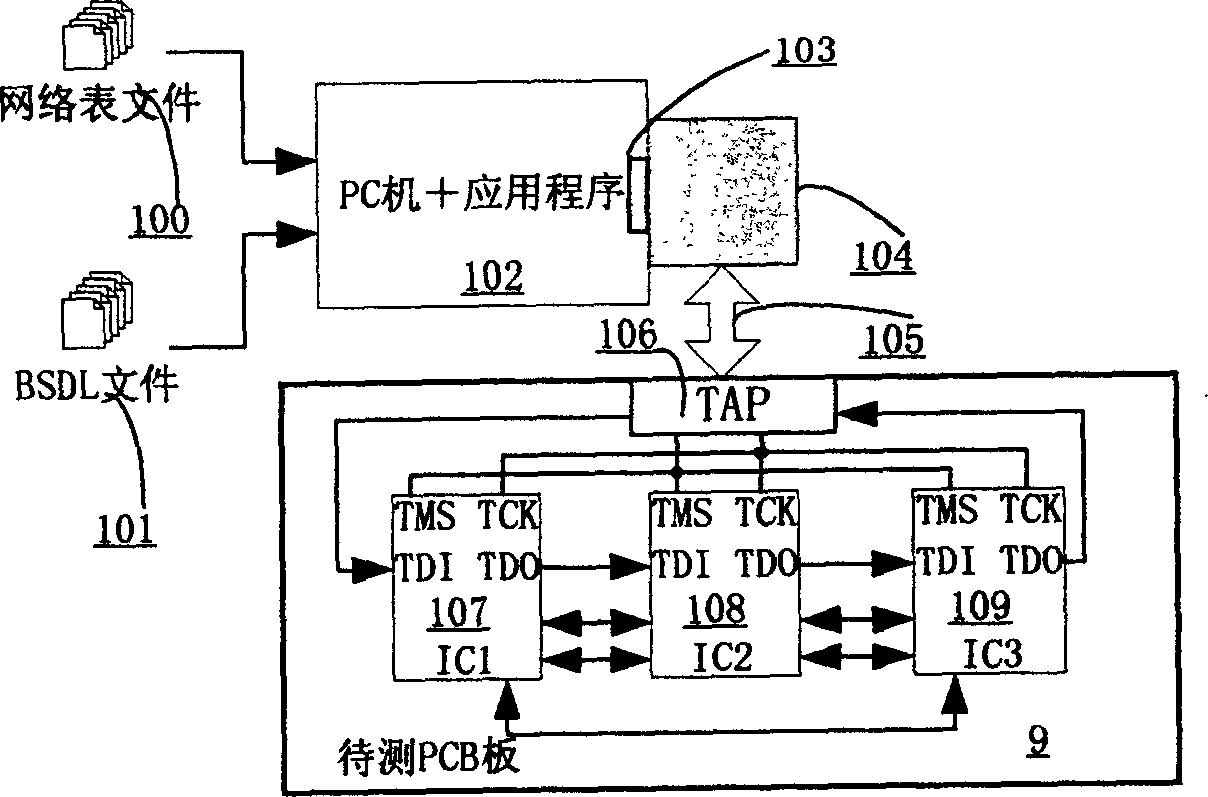

[0020] figure 2 It is an embodiment and a working flow chart of the device of the present invention. When the human-computer interaction interface 1 is started, the program of the initialization part of the program is started at the same time. Input the PCB netlist file and BSDL file, and perform the analysis of the two types of files respectively: netlist file analysis module 2 and BSDL file analysis module 3. Then execute the test vector generating module 4 to generate test vectors according to the analysis results of the two types of files. The test execution module 5 sends the test vector to the system under test 9 through the bottom layer interface module 6 and the JTAG hardware interfa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More