Array type reconstructural DSP engine chip structure based on CORDIC unit

A chip structure, array technology, applied in the field of DSP, can solve the problem of fixed chip data word width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

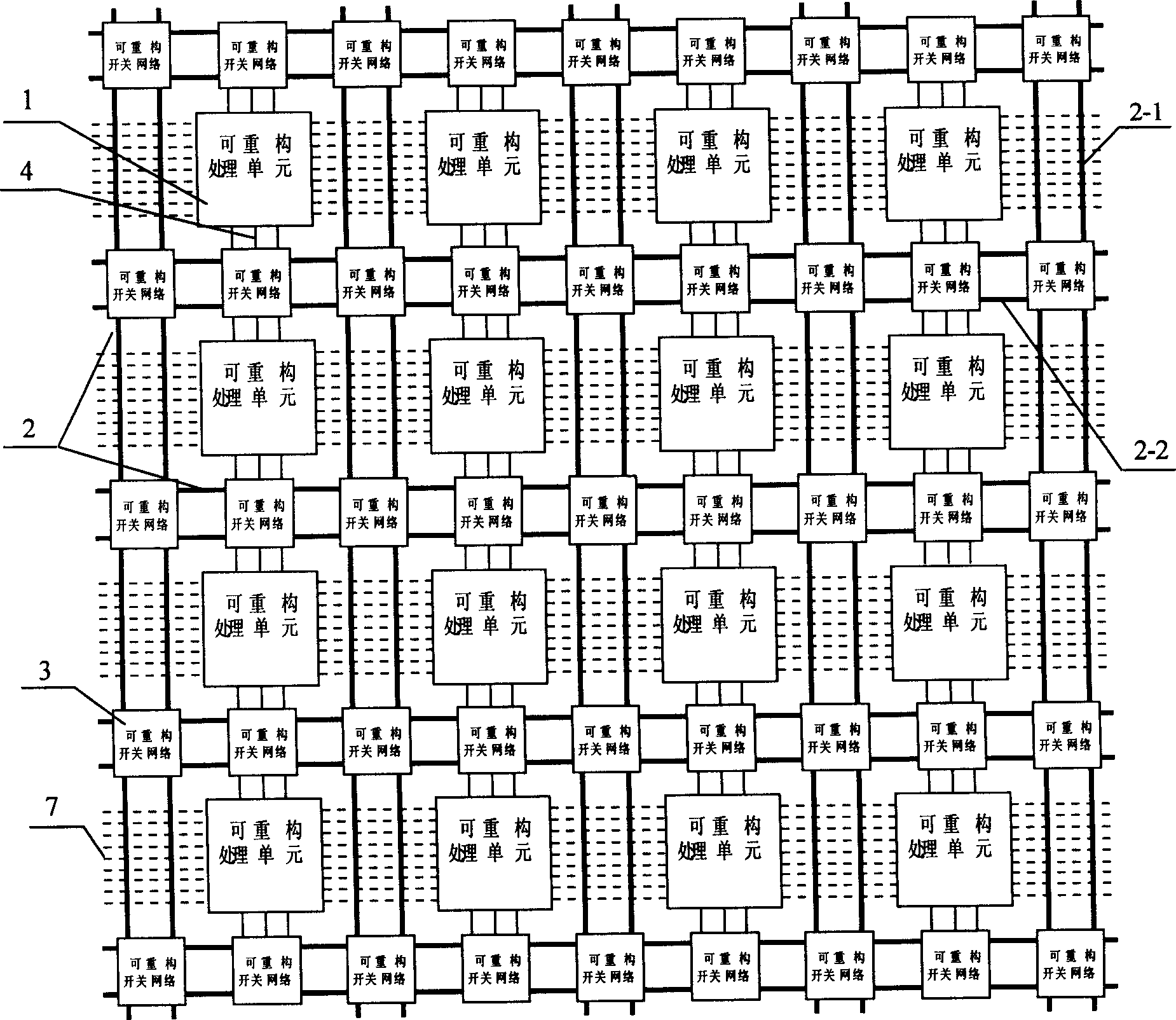

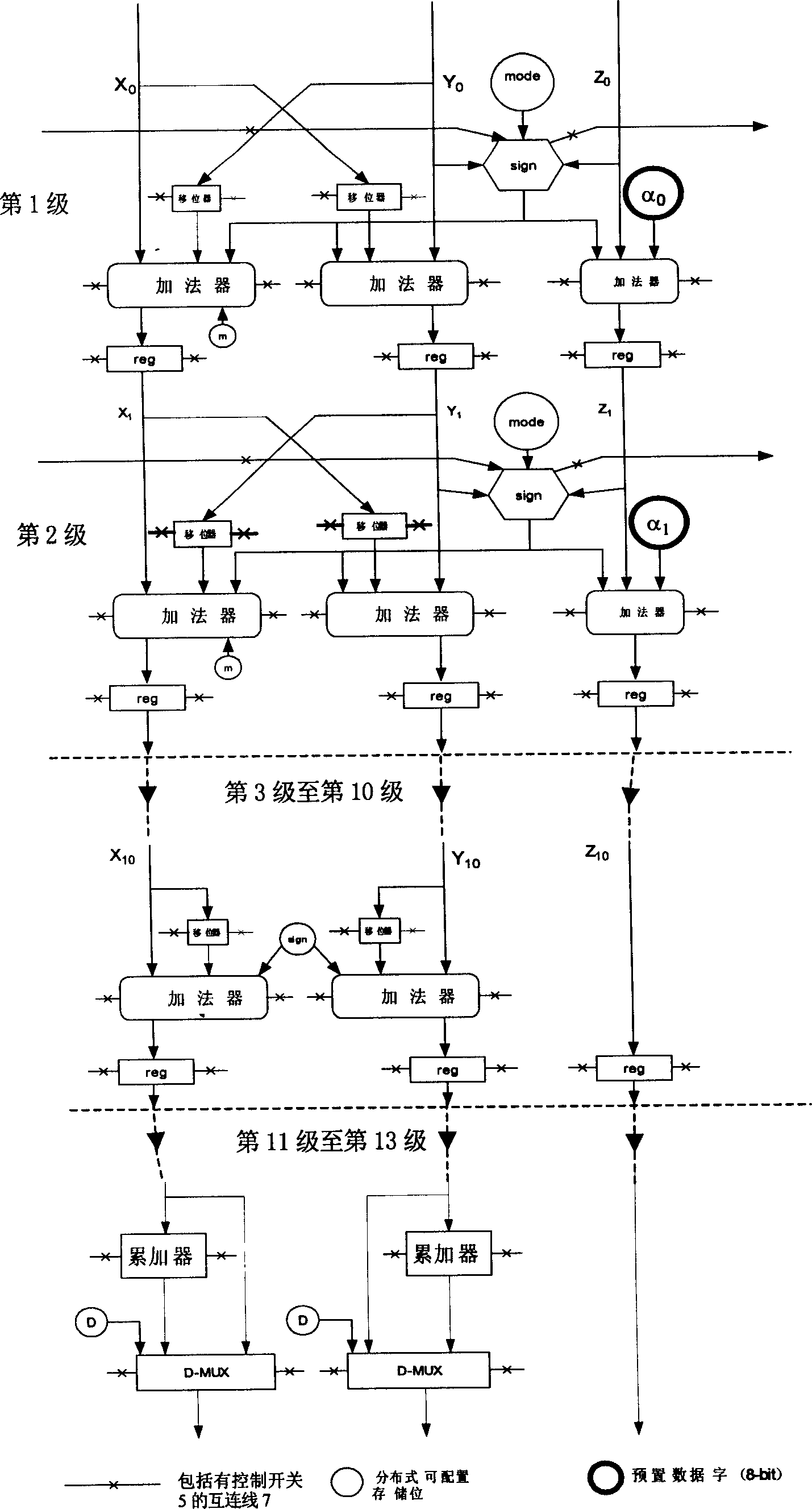

[0005] Specific implementation mode one: the following combination figure 1 , Figure 3 to Figure 6 This embodiment will be specifically described. An interconnection bus 2 is arranged between several reconfigurable processing units 1 arranged in an array, and the vertical interconnection bus 2-1 and the horizontal interconnection bus 2-2 are connected to each other through a reconfigurable switch network 3. Each adjacent reconfigurable processing unit 1 in the vertical arrangement direction is vertically connected through the basic unit data line 4, and the basic unit data line 4 is connected with the horizontal interconnection bus 2-2 through the reconfigurable switch network 3, The reconfigurable processing unit 1 is a several-stage pipeline structure of the cordic algorithm, the adder and the adder in the corresponding position in the same pipeline of the horizontally adjacent reconfigurable processing unit 1, the shifter and the shifter in the corresponding position The...

specific Embodiment approach 2

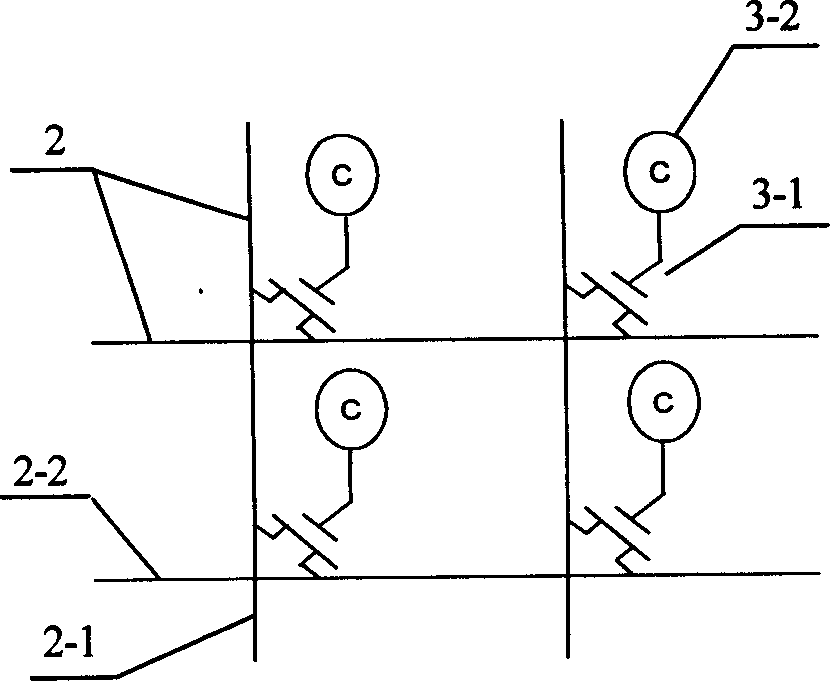

[0009] Specific implementation mode two: the following combination figure 1 and figure 2 This embodiment will be specifically described. The difference between this embodiment and Embodiment 1 is: the interconnection bus 2 is a 64-bit interconnection bus, the reconfigurable switch network 3 is composed of several switch tubes 3-1, and the switch tubes 3-1 are arranged vertically At the intersection of the 64 interconnection buses 2-1 and the 64 horizontal interconnection buses 2-2, the two main working poles of the switch tube 3-1 are connected to the longitudinal interconnection bus 2-1 and the horizontal interconnection bus 2-1 respectively. Connected to the bus 2-2, the control pole of the switch tube 3-1 is connected to the preset memory 3-2 for controlling the switch tube. When this embodiment is working, the configuration of the chip is determined by setting whether the switch tube 3-1 is connected or turned off in the preset memory 3-2 through programming. The switc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More