Phase-lock loop framework capable of avoiding frequency drift and jitter

A phase-locked loop and frequency technology, applied in the automatic control of power, electrical components, etc., can solve the problems of long-term frequency jitter, frequency is not accurate 125MHz, frequency drift, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

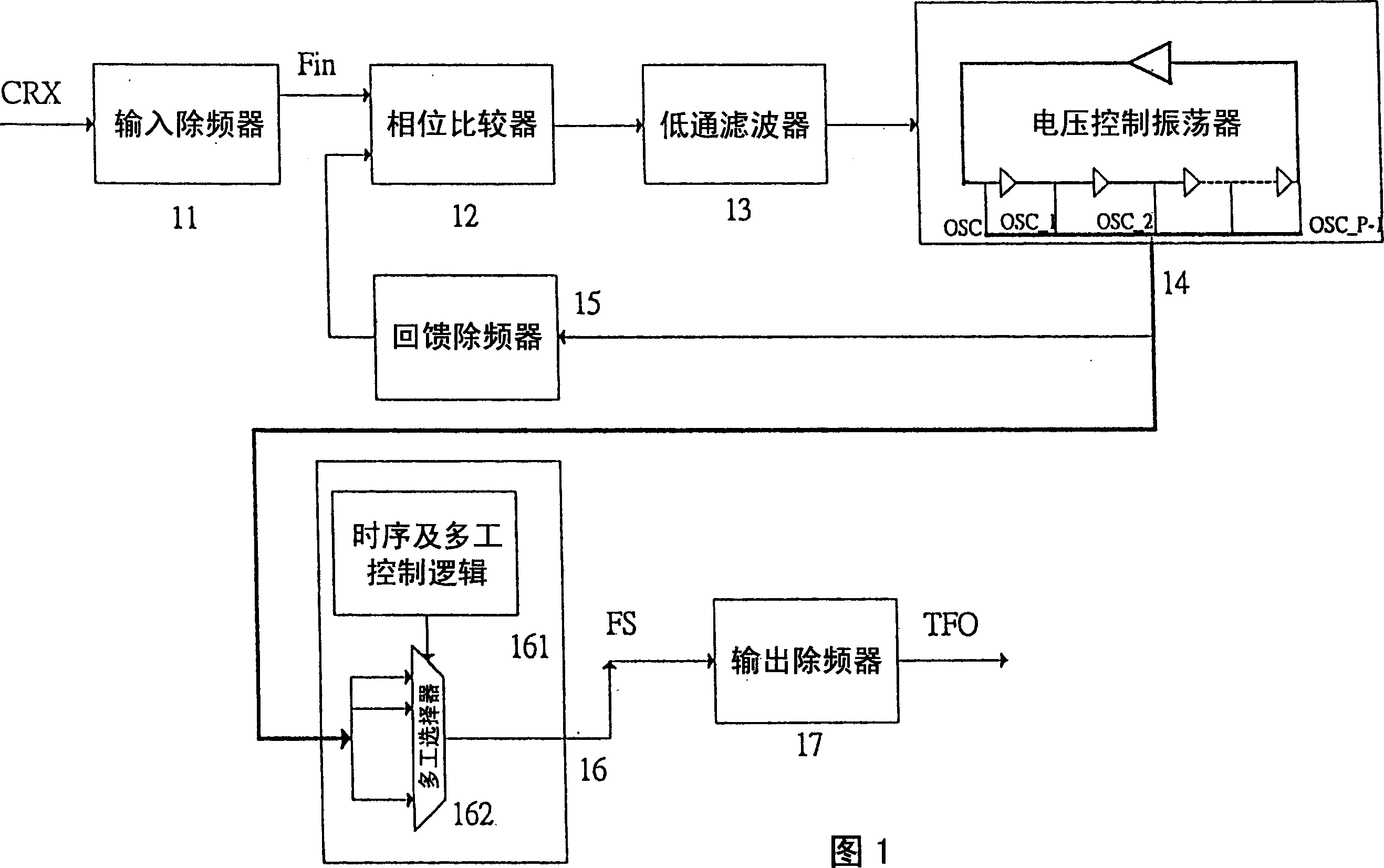

[0015] A preferred embodiment of the phase-locked loop structure that can avoid frequency drift and jitter of the present invention, please first refer to shown in Figure 1, it comprises a first frequency divider 11, a phase comparator 12, a low-pass A filter 13 , a VCO 14 , a second frequency divider 15 , a phase devourer 16 , and a third frequency divider 17 . Wherein, the circuit block composed of the first frequency divider 11 , the phase comparator 12 , the low pass filter 13 , the voltage controlled oscillator 14 , and the second frequency divider 15 is a phase locked loop.

[0016] In the aforementioned PLL loop, the first frequency divider 11 divides an input reference signal CRX by a divisor M (M is a positive integer); the second frequency divider 15 divides an input reference signal CRX by a divisor N (N is a positive integer) Perform frequency division on an oscillation signal OSC; the phase comparator 12 compares the output frequency division signal of the first f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com