Embedded signal processor simulator

A signal processor and simulator technology, applied in the field of embedded signal processor simulators, can solve problems such as slow simulation speed and lack of simulation debugging methods, and achieve the effect of high debugging accuracy and debugging efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

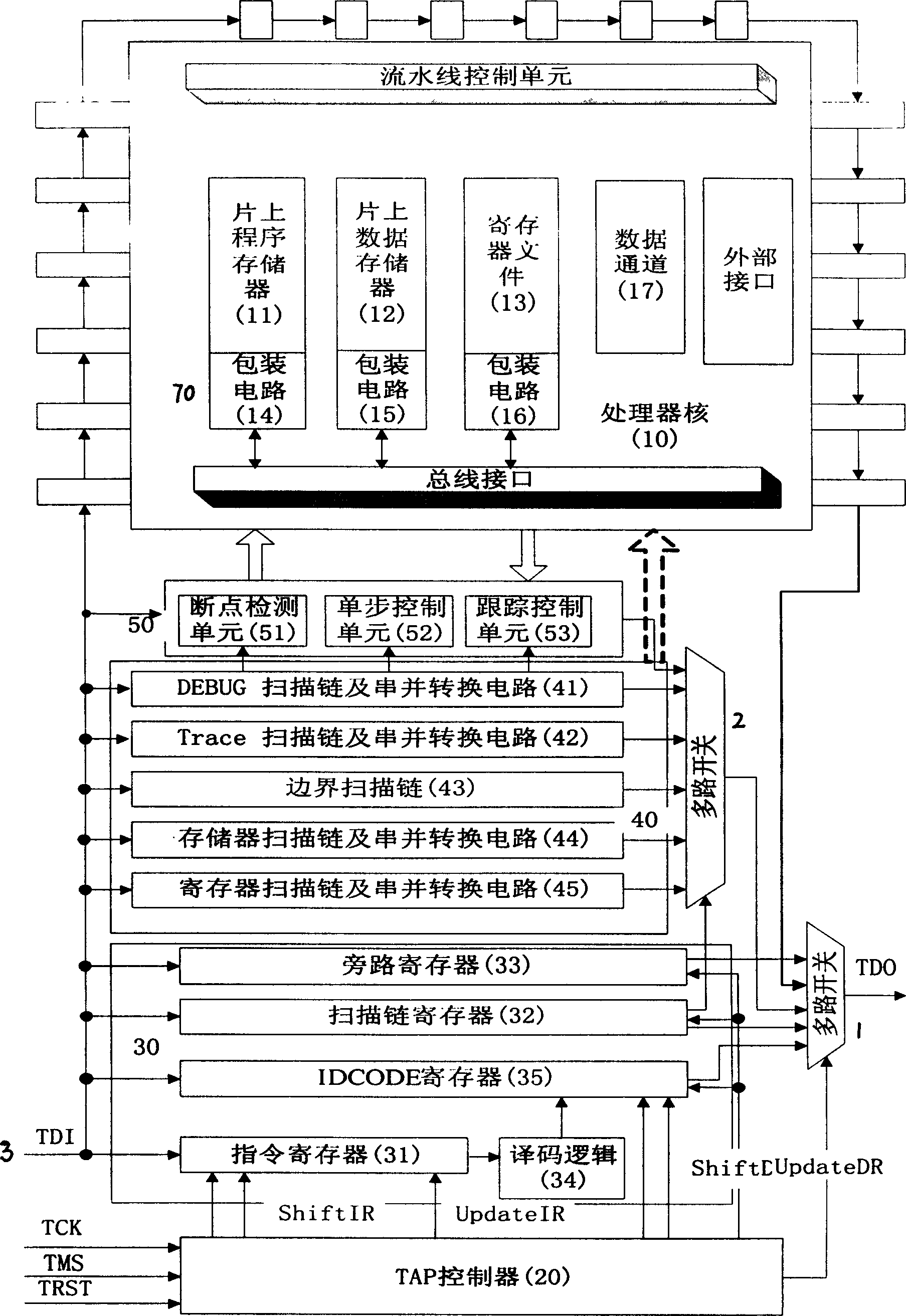

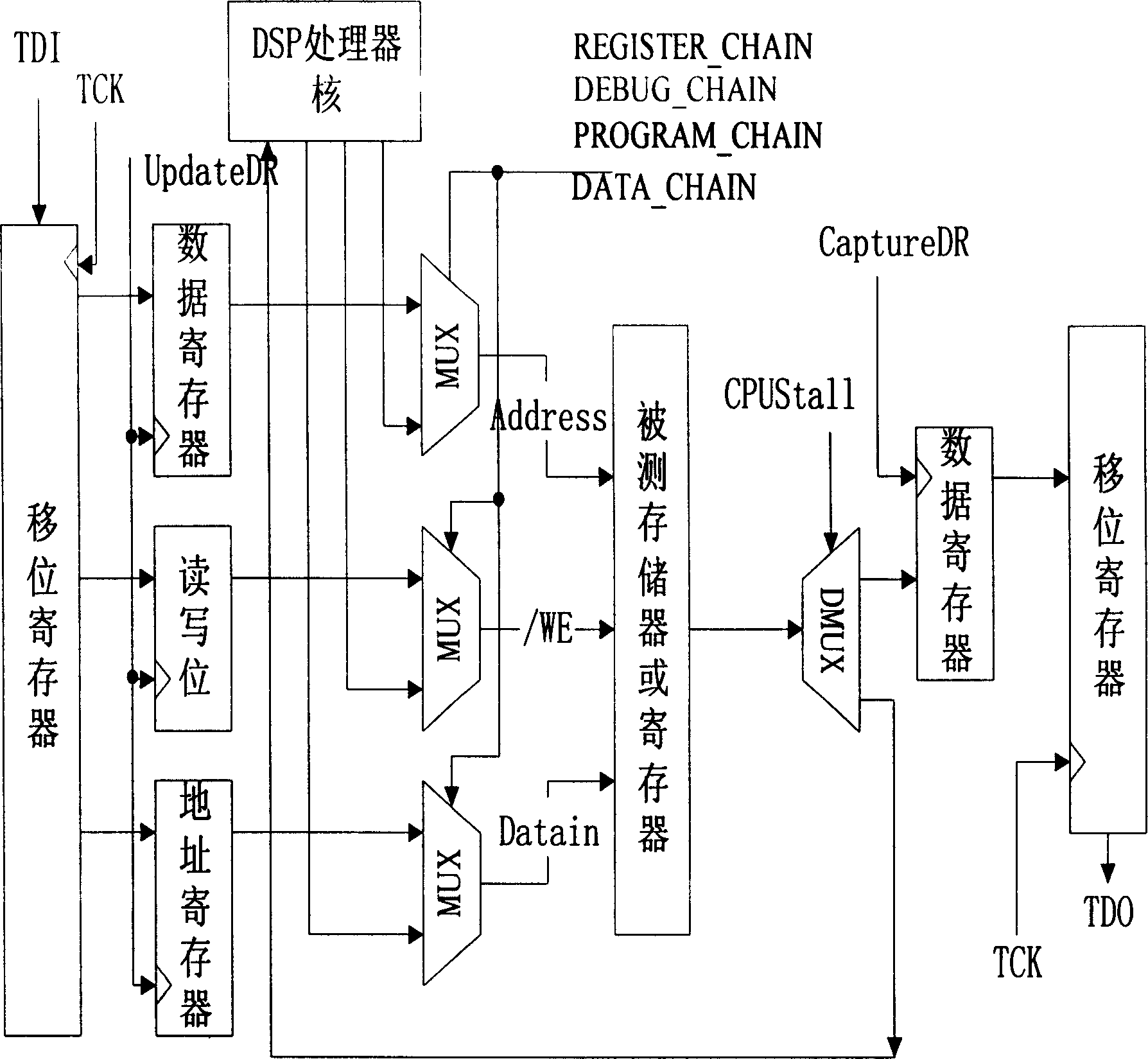

[0022] The invention proposes to partially modify and expand the standard JTAG protocol, and completes the design of an embedded analog module (EICM) suitable for DSP processors. The advantage of this is that the TAP controller and instruction register provided by the JTAG interface can be fully utilized, and only a small modification of the DSP processor core, the memory management unit and the JTAG interface is required, and there is no need to modify the internal registers of the processor. Replacement, the real-time simulation function of the DSP processor can be completed, and the compatibility with the JTAG protocol can be fully maintained.

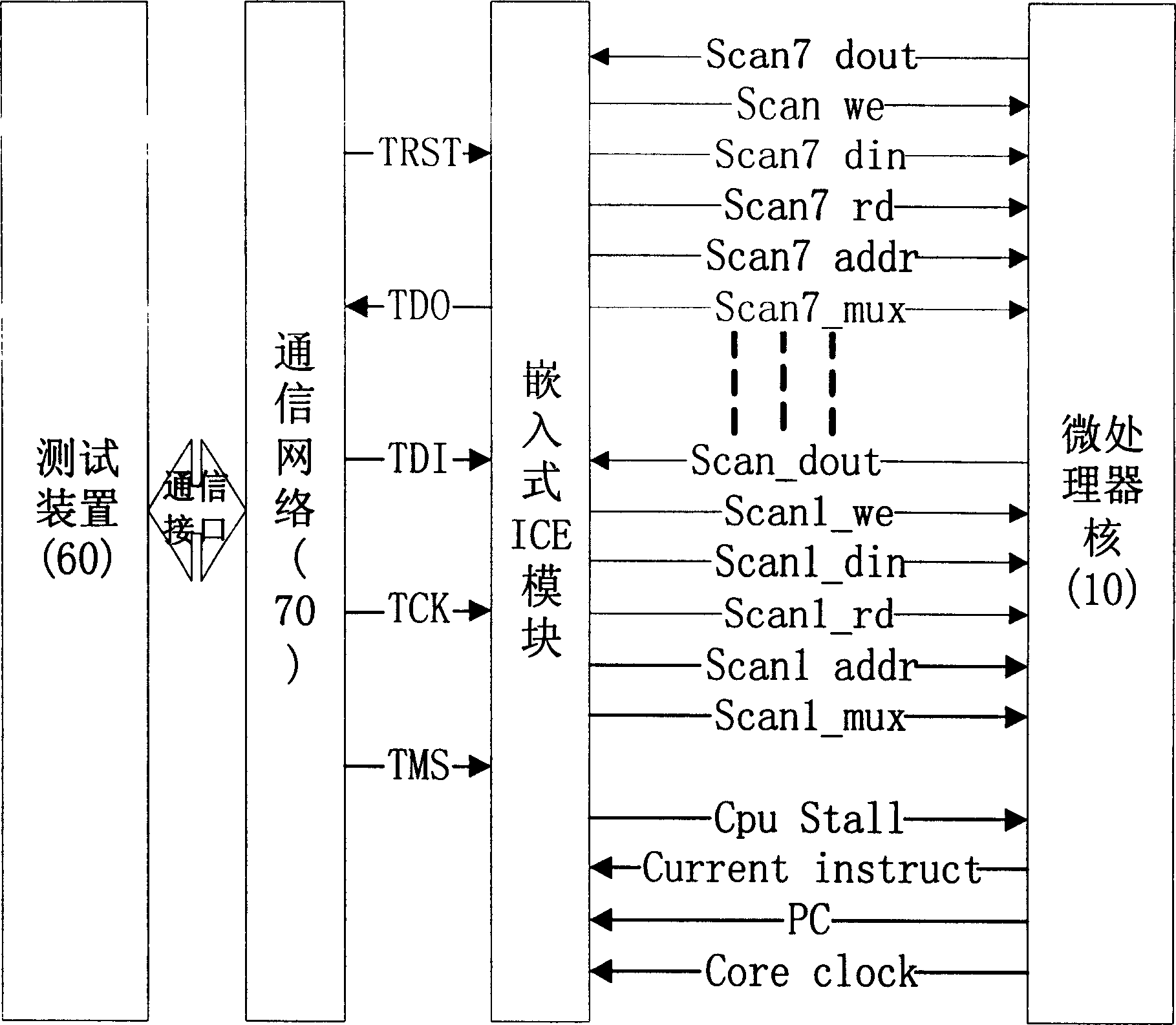

[0023] When designing the EICM, using such as figure 1 The structure shown, its connection circuit with the tested processor core is as follows figure 2 . In addition to using the standard TAP module of IEEE1149.1 and the boundary scan chain control module, the EICM simulator has designed the instructions of the JTAG instruction ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More