Method and apparatus for producing wirte-in gating clock signal

A technology of gated clock and write gate, applied in the directions of generating/distributing signals, information storage, digital memory information, etc., can solve the problems of power consumption, complex clock skew balance of clock network, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

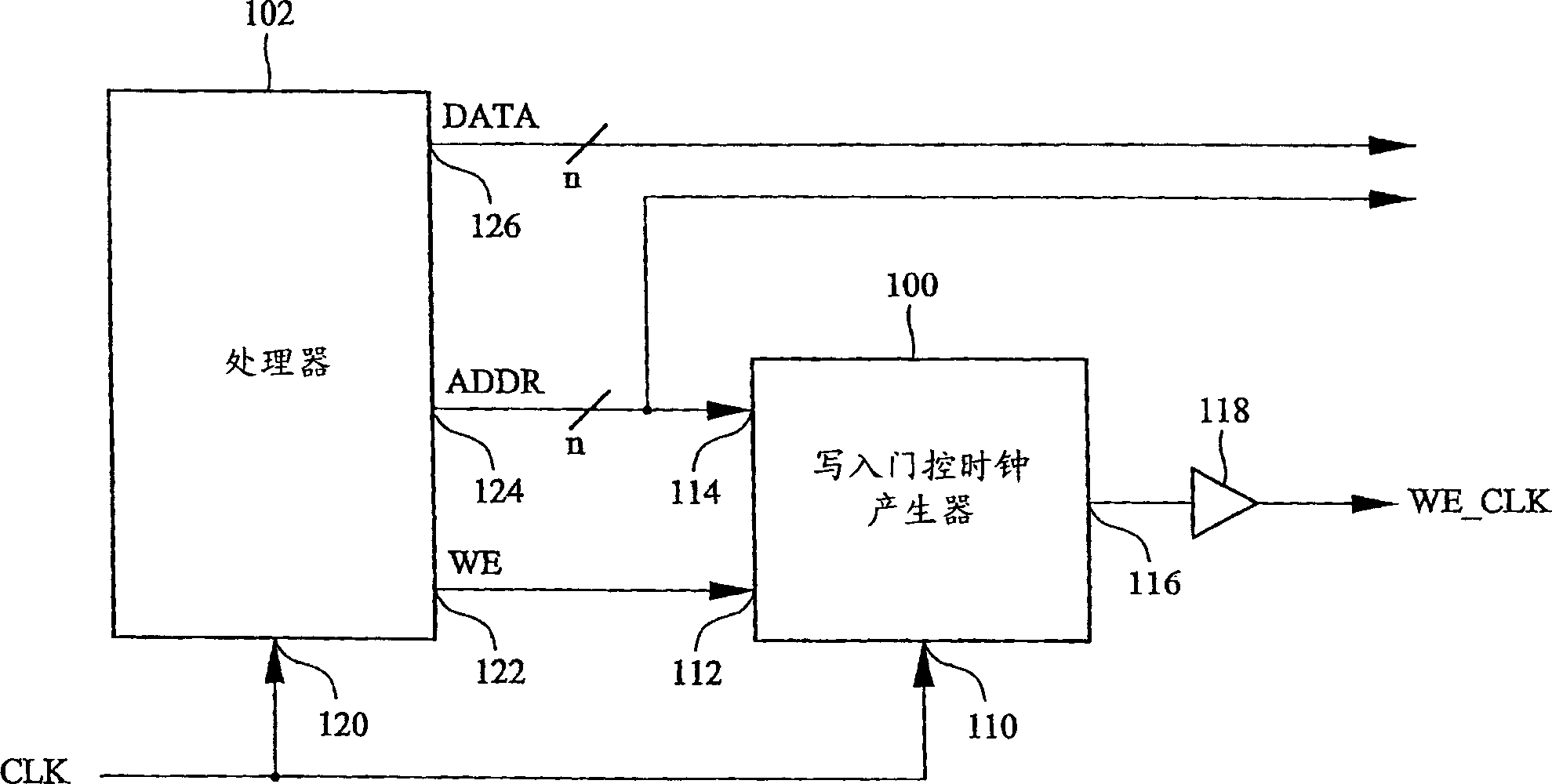

[0044] When the clock is running, even if the input data has not changed, the storage components still consume power. Providing a clock edge for writing to storage elements and when asserting enable signals saves power. The present invention can be used to generate a write gating clock (eg, WG_CLK) during a write operation. The write gating clock WG_CLK described above maximizes power savings and is more efficient than existing gating clocks.

[0045] The above-mentioned write gating clock WG_CLK can be used for many peripheral storage devices. The above-mentioned write gating clock WG_CLK is generated in response to a write enable signal (eg, WE) of a processor (or other circuits). The write gating clock WG_CLK can also be generated in response to signals on the address bus and other processor control signals. The write gating clock WG_CLK usually operates at the end of a write cycle. refer to image 3 , is shown here as an example of the write-gated clock generator 100 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More