Method for forming electronic devices in multi-layer structure of substrate

A technology for electronic devices and multi-layer structures, which is applied in the fields of electro-solid devices, nanotechnology for information processing, nanotechnology for materials and surface science, etc. It can solve the problems of insufficient position accuracy and small overlapping capacitance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

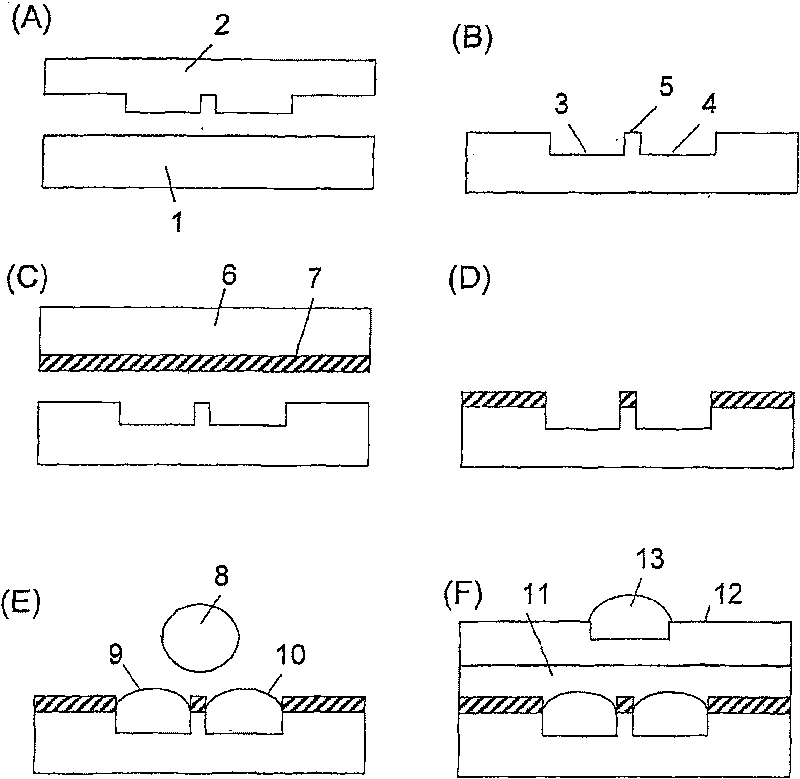

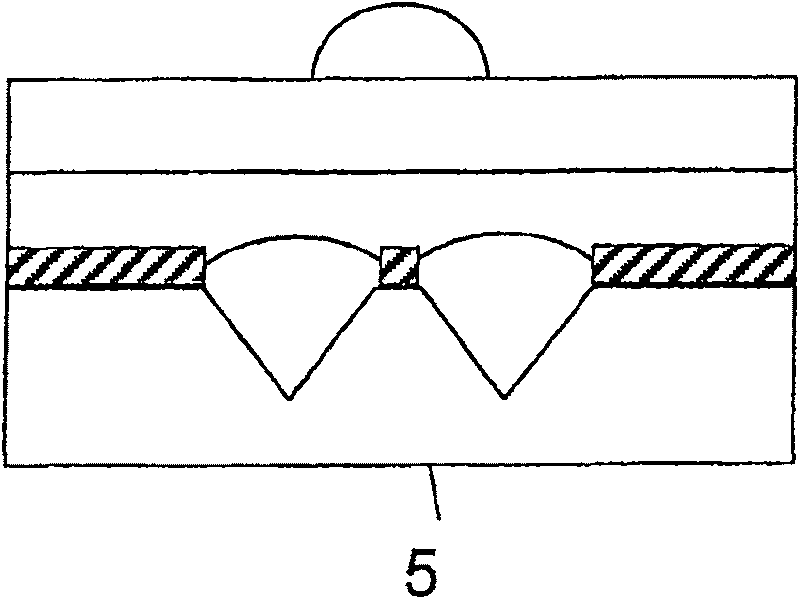

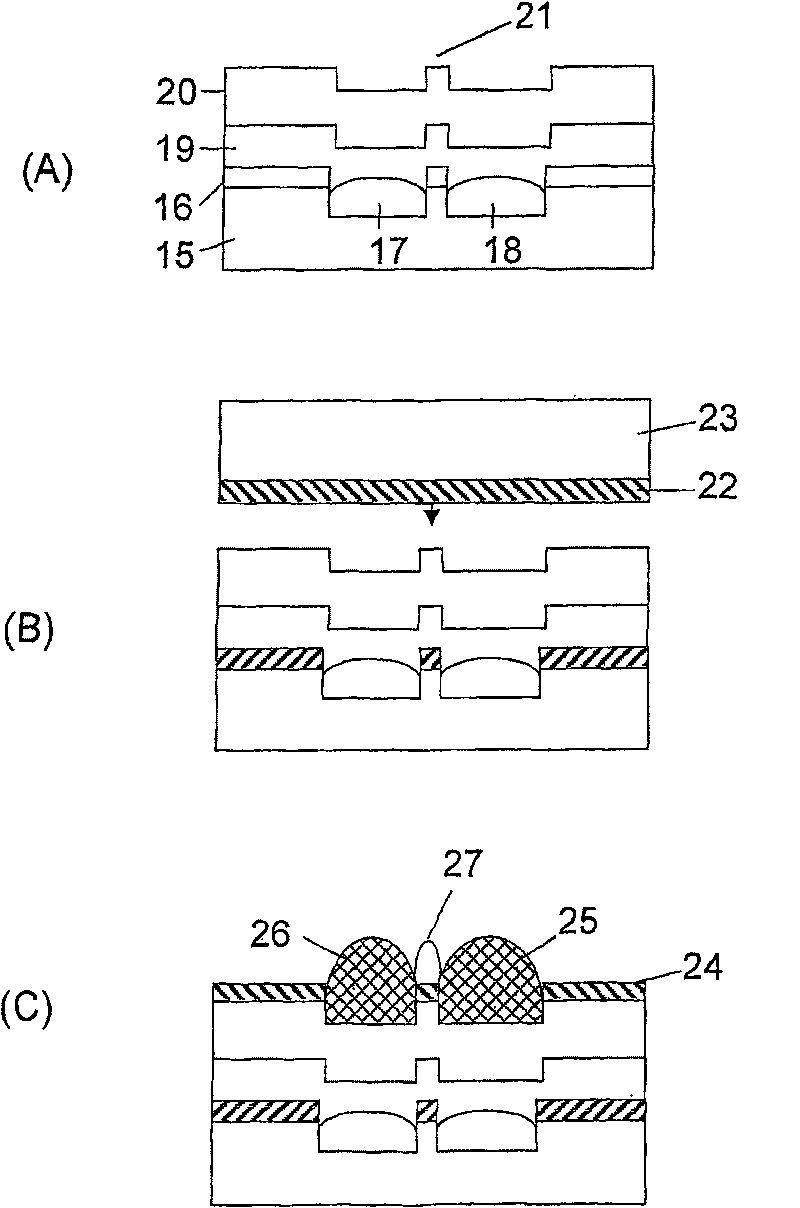

[0026] figure 1 A schematic diagram showing the use of imprinting to define the critical channel length of a FET device. The substrate 1 is a flexible plastic substrate such as poly(ethylene terephthalate) (PET), polyethersulfone (PES), and polyethylene naphthalate (PEN). Alternatively, the substrate may be a rigid substrate, such as a glass substrate coated with a polymer layer. The substrate is imprinted by pressing an embossing tool 2 comprising an array of raised features into the substrate. The imprinting step is performed at an elevated temperature, preferably close to the glass transition temperature of the substrate or the uppermost layer on the substrate. The embossing step can also be carried out by placing the substrate 1 in its liquid phase. Preferably, the thickness of the polymer layer is chosen to be greater than the height of the raised features of the embossing tool. If the polymer layer is thinner than the height of the raised features of the stencil, car...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| glass transition temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More