Memory chip internal power administrative framework in deep shutdown mode

A memory and deep technology, applied in the direction of information storage, static memory, digital memory information, etc., can solve the problem that the low current goal is difficult to achieve and other problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

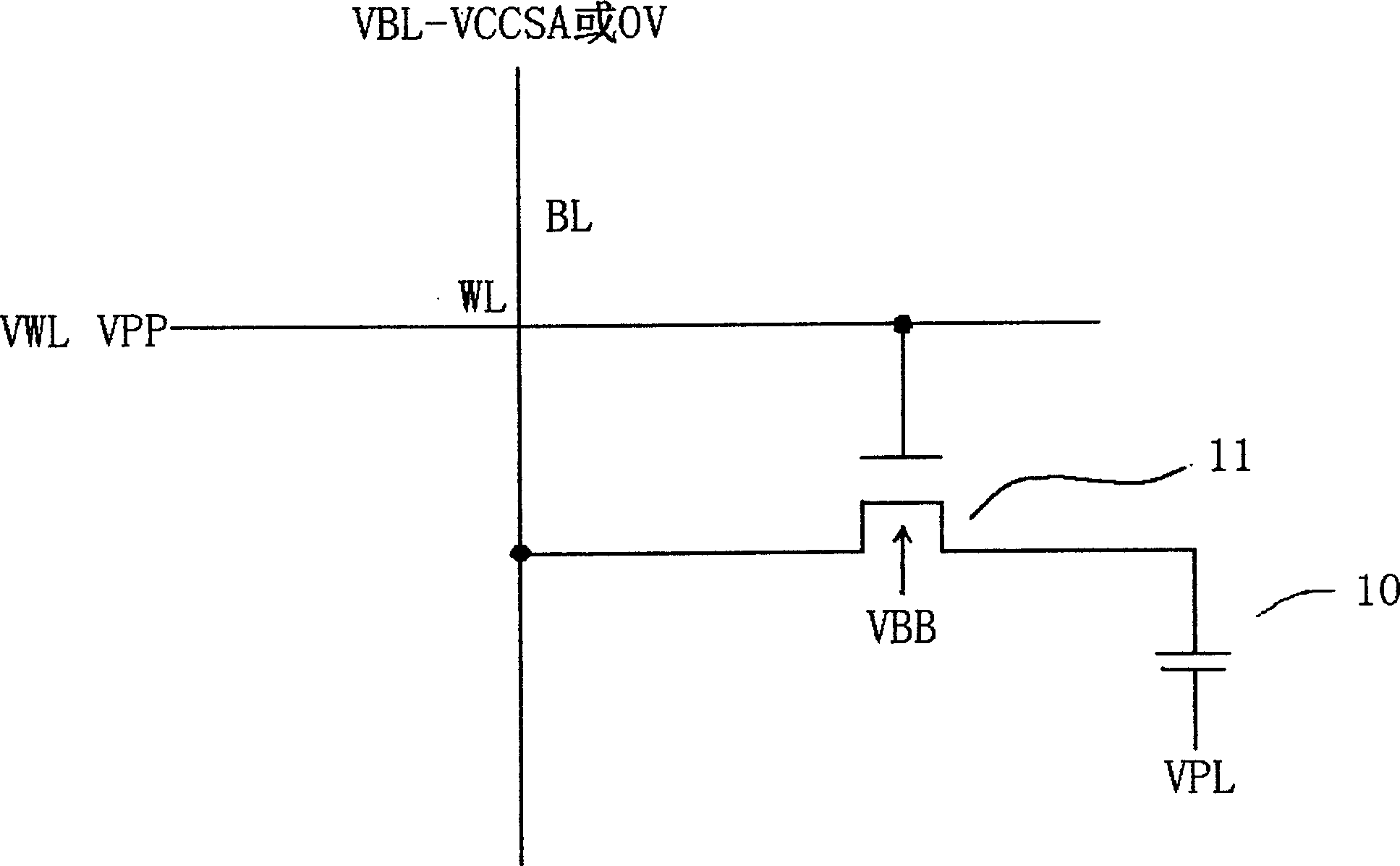

[0026] Figure 1A Shown in is the circuit diagram of the DRAM memory cell with the voltage used in the enabled state of the present invention. The bit line voltage VBL is connected to the sense amplifier voltage, which depends on the bit line data and is equal to VCCSA or 0 volts. The word line voltage VWL of the memory cell in the enabled state is VPP, and the panel voltage VPL coupled to the storage capacitor 10 is a voltage lower than the bit line sense amplifier power supply voltage VCCSA, and is generally a bit line sense Half the value of the amplifier voltage VCCSA. The base voltage VBB of the enabling unit 11 is lower than 0 volts.

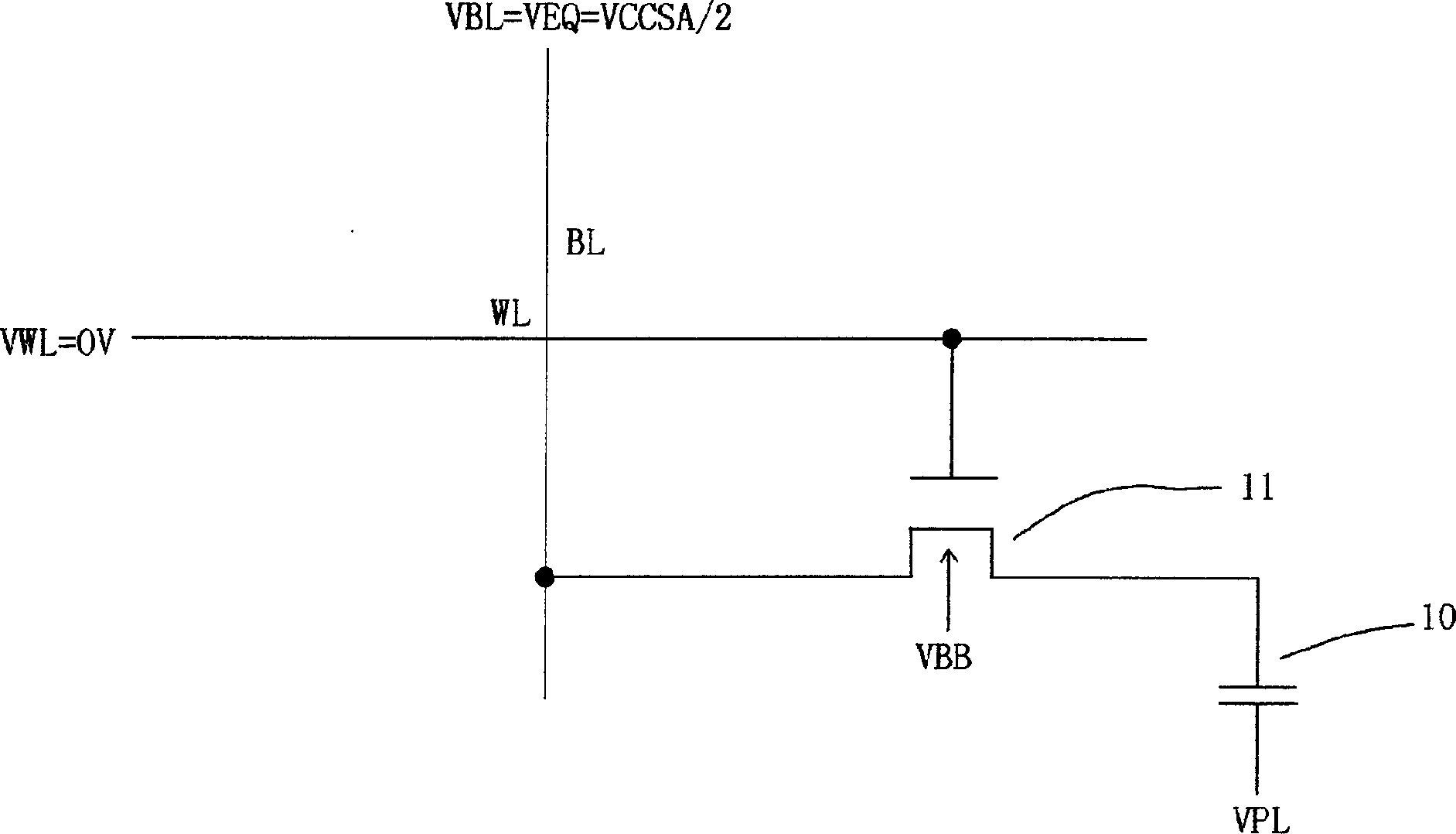

[0027] Figure 1B Shown in is the circuit diagram of the DRAM memory cell with the voltage used in the precharge state of the present invention. The bit line voltage VBL is coupled to the voltage VEQ (the equal voltage of the bit line sense amplifier), which is lower than the bit line sense amplifier power supply voltage VCCSA, and is genera...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More