Production of non-volatile memory

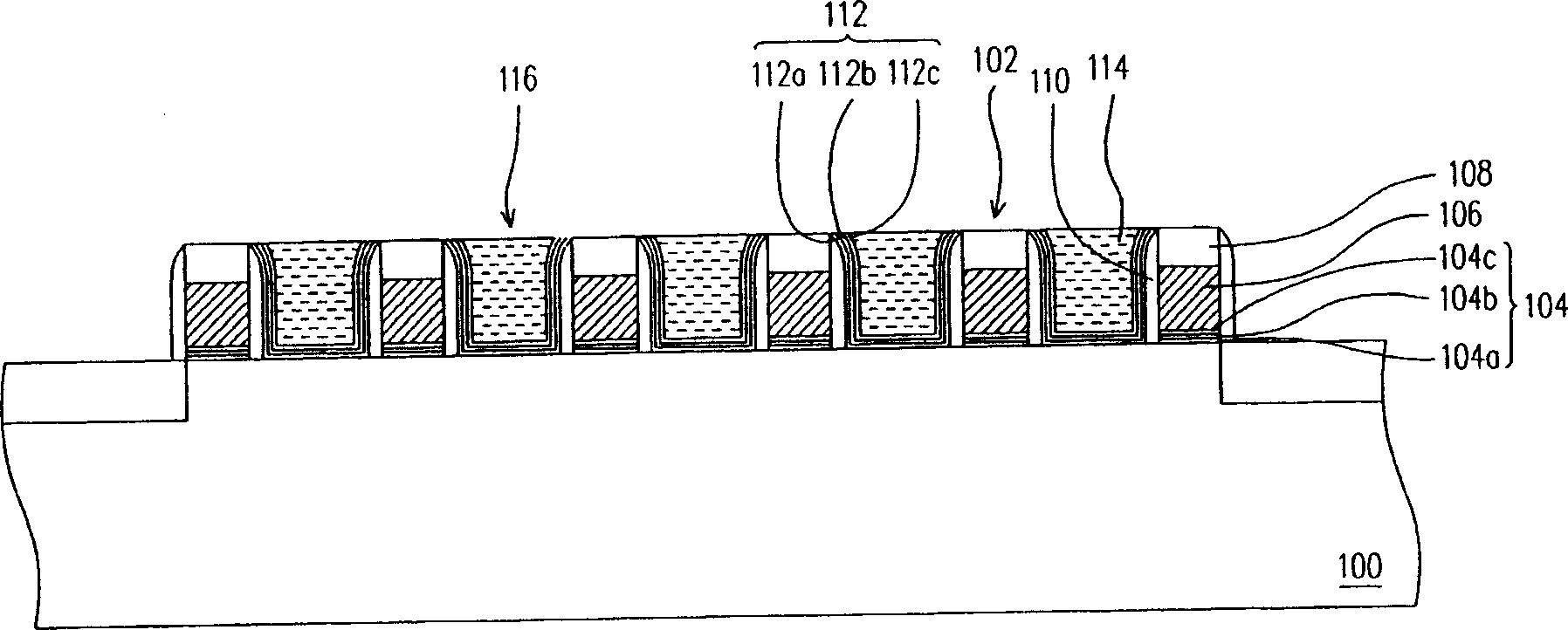

A manufacturing method and non-volatile technology, which are applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of inconsistent performance of the storage unit 102 and the storage unit 116, uneven thickness of the composite dielectric layer 112, and storage unit 116. problems such as poor reliability, to achieve the effect of improving poor quality, reducing costs, and simplifying process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

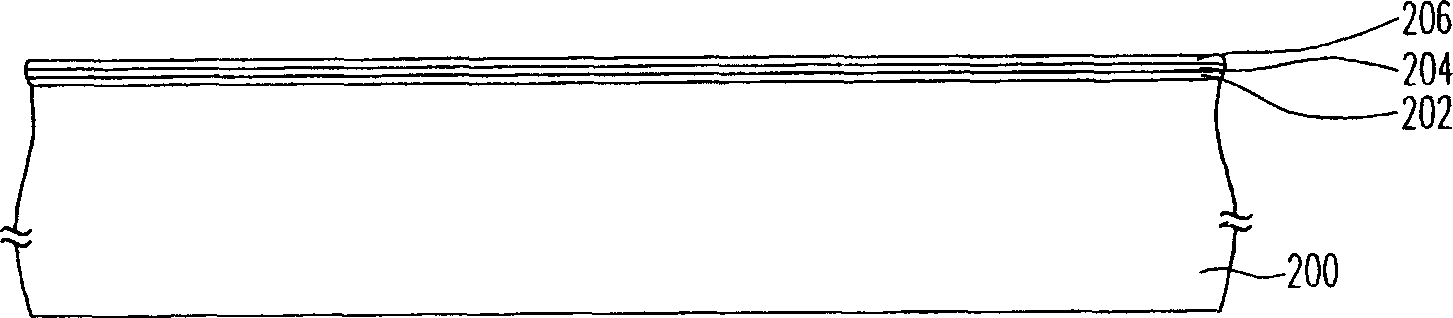

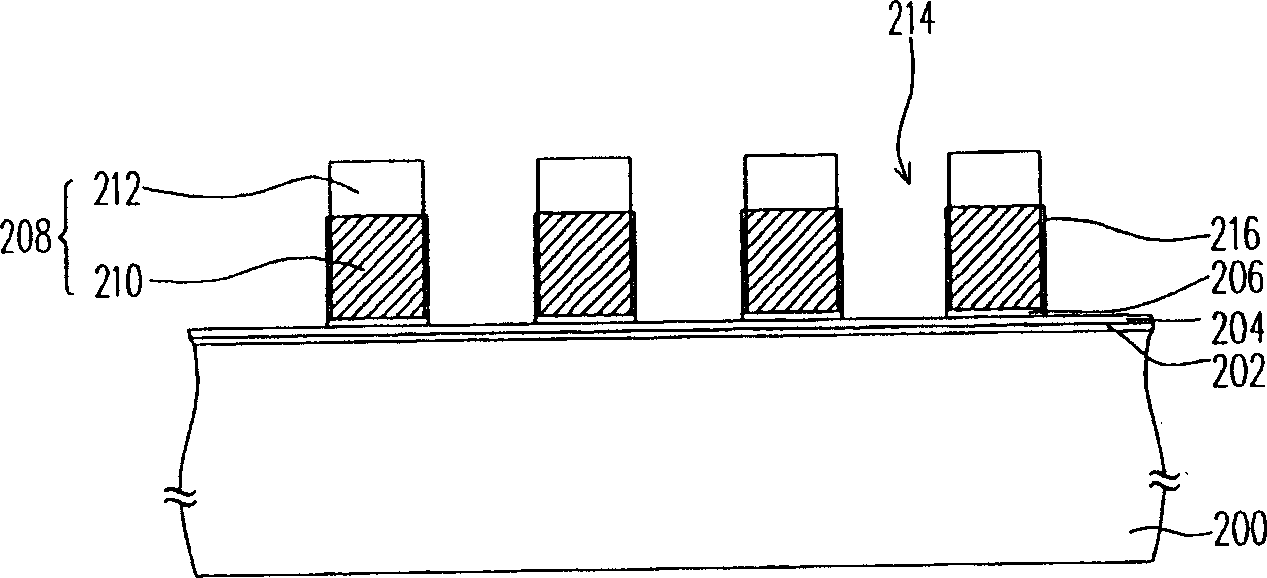

[0051] Figure 2A to Figure 2D A cross-sectional view of the manufacturing process of a non-volatile memory according to a preferred embodiment of the present invention is shown.

[0052] First, please refer to Figure 2A, providing a substrate 200, the substrate 200 is, for example, a silicon substrate. Next, a bottom dielectric layer 202 , a charge trapping layer 204 and a top dielectric layer 206 are sequentially formed on the substrate 200 . Wherein, the material of the bottom dielectric layer 202 is, for example, silicon oxide, and its formation method is, for example, thermal oxidation. The material of the charge trapping layer 204 is, for example, silicon nitride, and its formation method is, for example, chemical vapor deposition. The material of the top dielectric layer 206 is, for example, silicon oxide, and its formation method is, for example, chemical vapor deposition. Of course, the bottom dielectric layer 202 and the top dielectric layer 206 can also be made...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More