Shielded bitline architecture for dynamic random access memory (dram) arrays

一种存储器阵列、存储器的技术,应用在静态存储器、数字存储器信息、信息存储等方向,能够解决耗费芯片晶粒面积、装置费用增加、总动态随机存取存储器数组面积增加等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

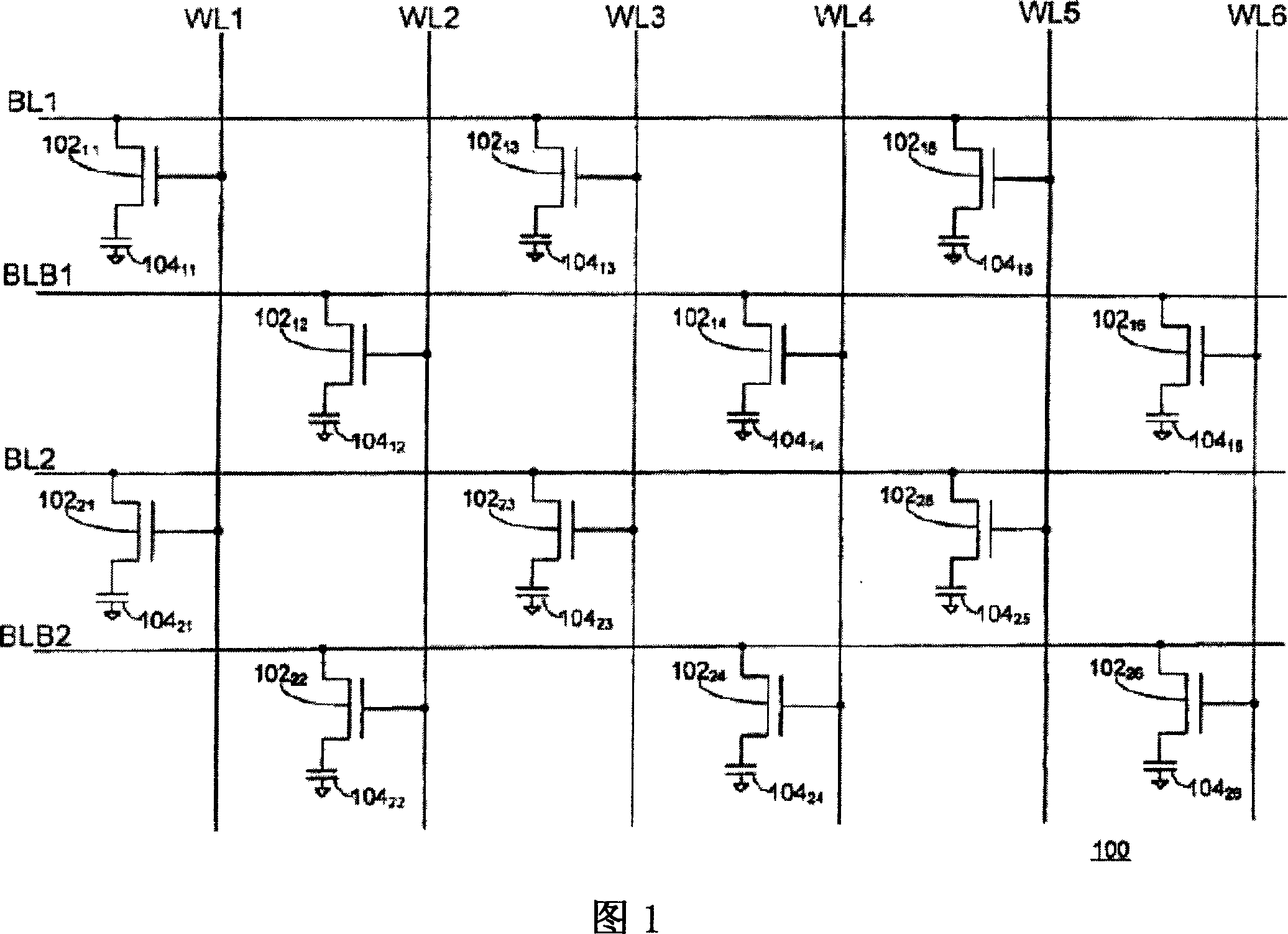

[0054] Referring to FIG. 1 , it is a part of a typical DRAM array 100 with a folded bit line structure, wherein the bit lines marked as BLB (bitline bar, such as BLB1 and BLB2) serve as the bit lines marked as BL (such as BL1 and BL2) Line reference, which is input to a sense amplifier (not shown) when the word line (WL) is "high".

[0055] Each memory cell of the DRAM array 100 includes an N-type channel access transistor 102 11 ~102 16 and 102 21 ~102 26 , and respectively include a connected storage capacitor 104 11 ~104 16 and 104 21 ~104 26 . The drain of each transistor 102 is coupled to one of the corresponding complementary bit lines, its gate is coupled to one of the word lines WL1-WL6, the source of each transistor 102 is coupled to the plate of the corresponding capacitor 104, the other plate of which Depending on the memory technology used, it is decided to couple to circuit ground (VSS) or to a common plate line.

[0056] In the part of the dynamic random...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More