Arranging method for cathode pattern in integrated gate pole changing thyratron transistor

A commutating thyristor and integrated gate technology, applied in transistors, electrical components, electrical solid devices, etc., can solve the problems of loss area, reduction of chip area utilization, etc., and achieve the effect of improving current capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

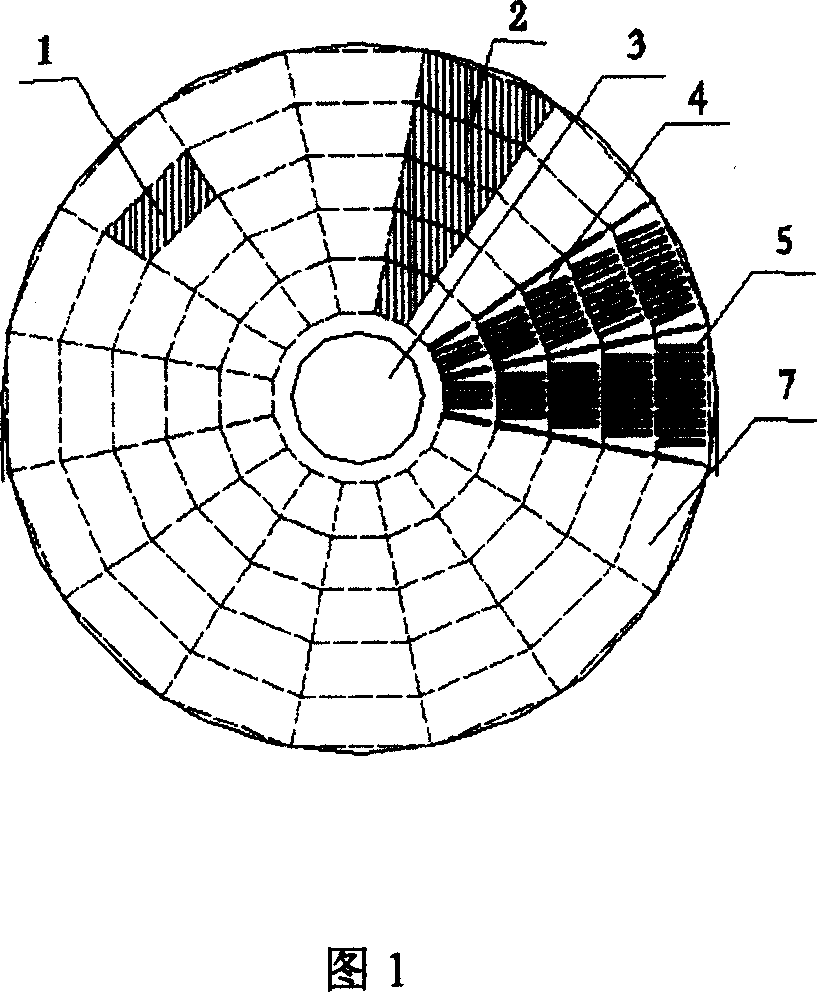

[0039] Figure 1 shows a cathode comb arrangement with a central gate structure, which is suitable for devices with a chip diameter of 30-60 mm. It can be seen from the accompanying drawings that this embodiment is a fully-controlled power semiconductor device chip, and the surface of the chip is photo-engraved with cathode combs 5, and the cathode combs 5 are arranged in a partitioned composite manner, combined with a circular arrangement Based on the respective advantages of the rectangle and the rectangle, the slivers are arranged in a rectangle inside the partition 1, and the slivers are still arranged in a circle at the joints between the partitions. On the one hand, it maintains a high area utilization rate, and on the other hand, it maintains the circular symmetry of the graph as a whole.

[0040] The partition composite method is: partition 1 is formed by double division of sector 2 and ring road 7, wherein, described partition 1 is an isosceles trapezoidal area, which ...

Embodiment 2

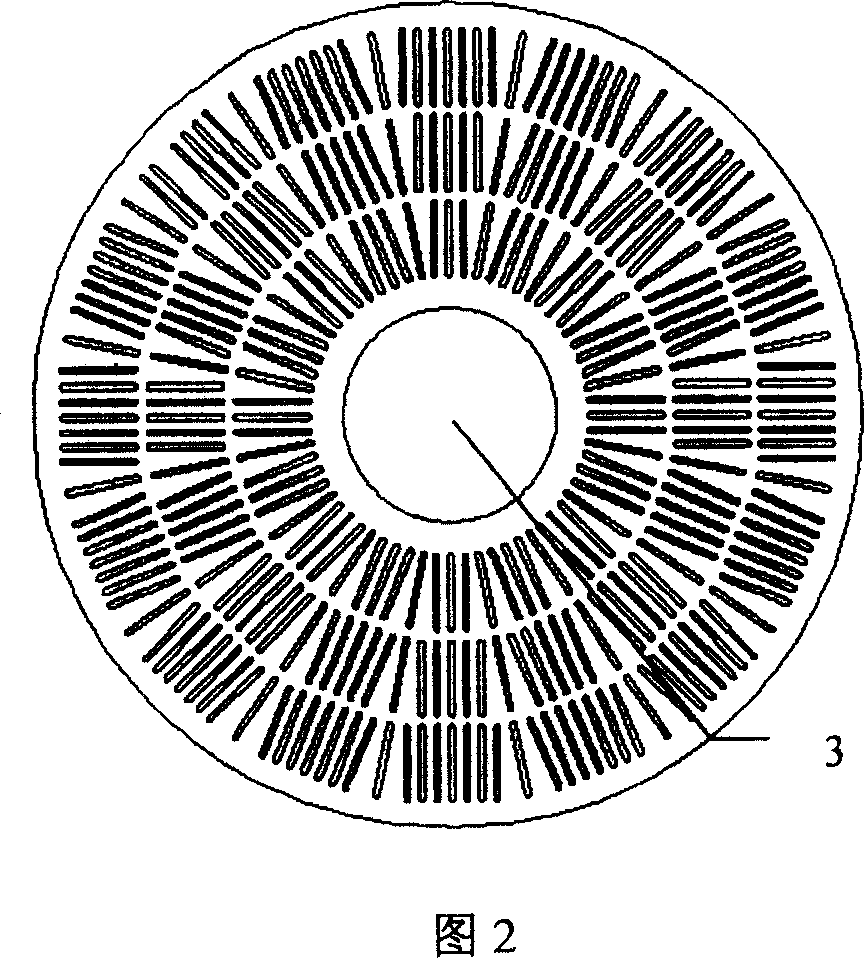

[0046] Embodiment 2 is the same as Embodiment 1 in that the sliver arrangement is the same, except that the number of sectors m in Embodiment 2 is 16, and the number of loops n is 5.

Embodiment 3

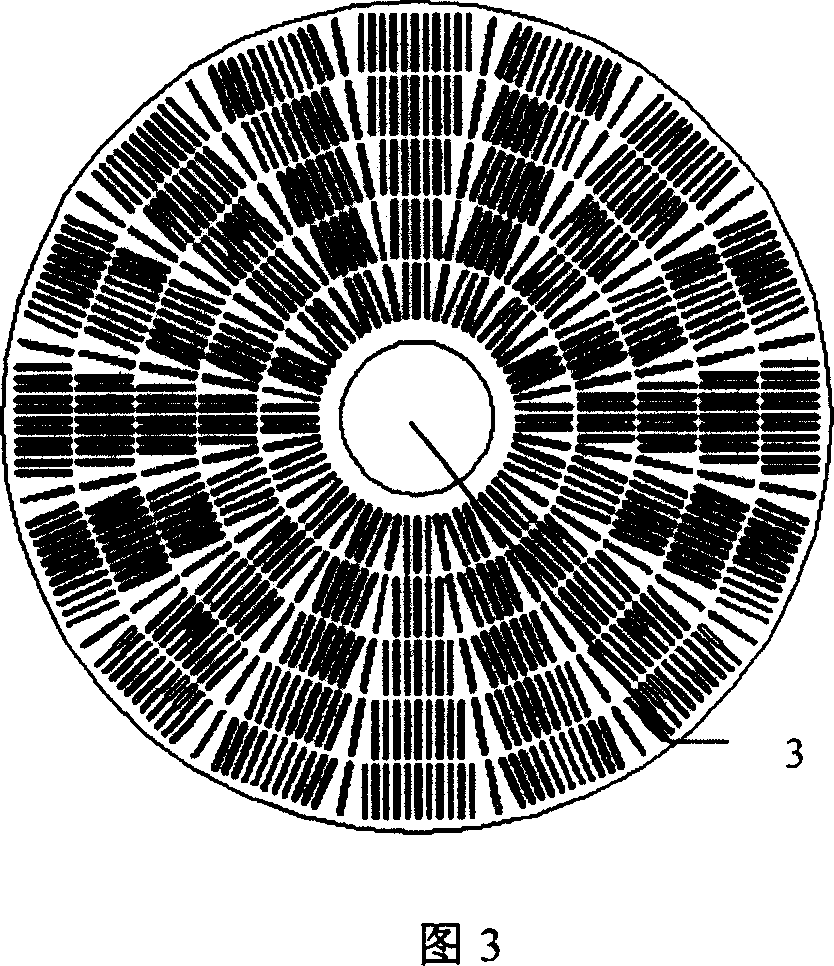

[0048] Embodiment 3 is the same as Embodiment 1 in that the sliver arrangement is the same, except that the number of sectors m in Embodiment 3 is 16, and the number of loops n is 4. However, the third embodiment is a reverse conduction chip, so a diode region 8 is provided on the outer circle of the chip.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More