Upside-down mounted chip packaging method and packaging structure thereof

A packaging method and packaging structure technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of unable to guarantee stable product quality, expensive equipment investment, and low capacity utilization, so as to avoid thermal expansion coefficient. Matching, simplification of packaging steps, and cost-saving effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

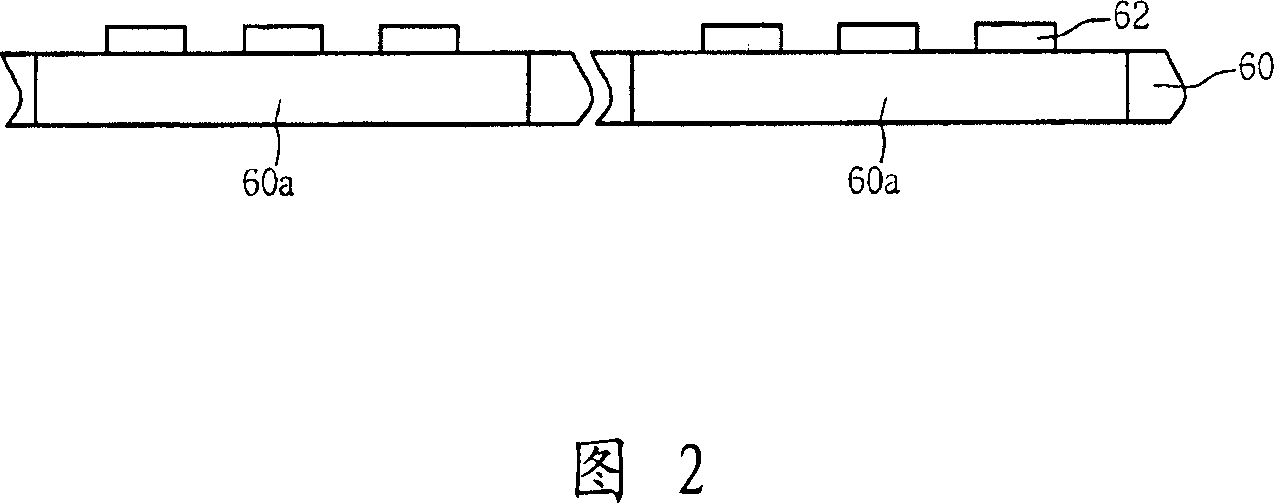

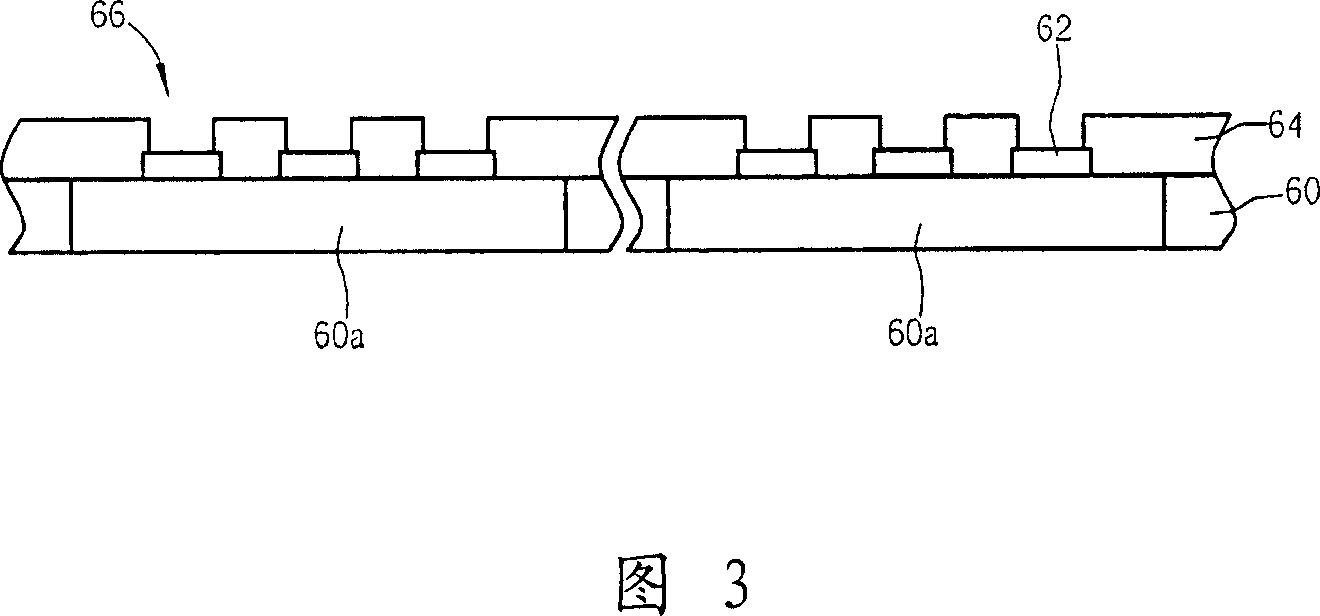

[0042] Please refer to FIG. 2 to FIG. 8 . FIG. 2 to FIG. 8 are process schematic diagrams of the first embodiment of the flip chip packaging method according to the present invention. As shown in Figure 2, at first provide substrate 60, for example multi-layer substrate, and substrate 60 has a plurality of IC substrate units 60a, and at least one metal interconnection layer (not shown in the figure) is arranged in IC substrate unit 60a shown), and a plurality of connection pads 62 are provided on the surface of the IC substrate unit 60a. As shown in FIG. 3 , a patterned insulating layer 64 is then formed, covering the substrate 60 and the connection pads 62 , exposing part of the upper surface of each connection pad 62 and forming openings 66 respectively. Wherein, the insulating layer 64 is a pre-cured adhesive layer, and the material constituting the insulating layer 64 includes photosensitive or non-photosensitive polymer resin. In addition, the material constituting the i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More