Method for realizing high-parallel frame predicator

An intra-frame prediction and predictor technology, which is used in television, electrical components, digital video signal modification and other directions, can solve the problems of increasing control logic complexity, complexity and redundancy, and achieves reduction of circuit area and simplification. The effect of control logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

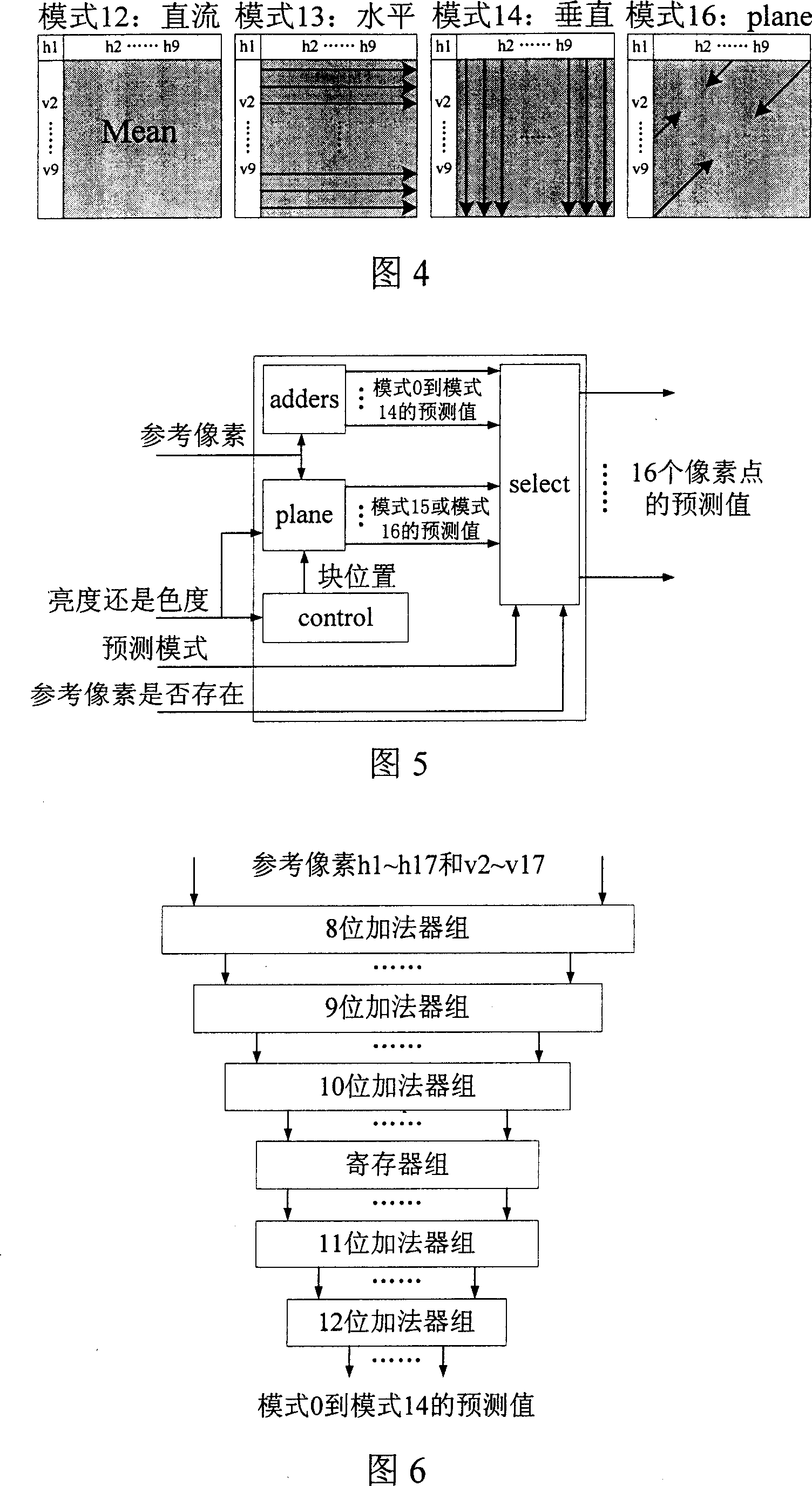

[0173] Here is a detailed description of the specific implementation process of the adders module and the plane module after removing the calculation redundancy by using the digital calculation intensity reduction algorithm, and the implementation mode of the select module.

[0174] The adders module shown in Figure 6 is composed of an adder group. By observing the prediction formulas of mode 0 to mode 14 of 16 pixels in a 4×4 size block, the same addition operation is only calculated once and the result is shared. In order to reduce the length of the critical path, a set of registers is inserted between the 10-bit adder bank and the 11-bit adder bank of Figure 6. The addition operation completed by each adder group in Figure 6 is as follows:

[0175] 8bit adder group:

[0176] Numbering

[0177] 9bit adder group:

[0178] Numbering

[0179] 10bit adder group:

[0180] Numbering

[0181] 11bit adder group:

[0182] Numbering

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More