Pin-assignment method for integrated circuit packages to increase the electro-static discharge protective capability thereof

a technology of integrated circuits and pin assignments, which is applied in the direction of solid-state devices, electric devices, electrical equipment, etc., can solve the problems of esd damage, ic chip damage, esd damage is particularly common and severe,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

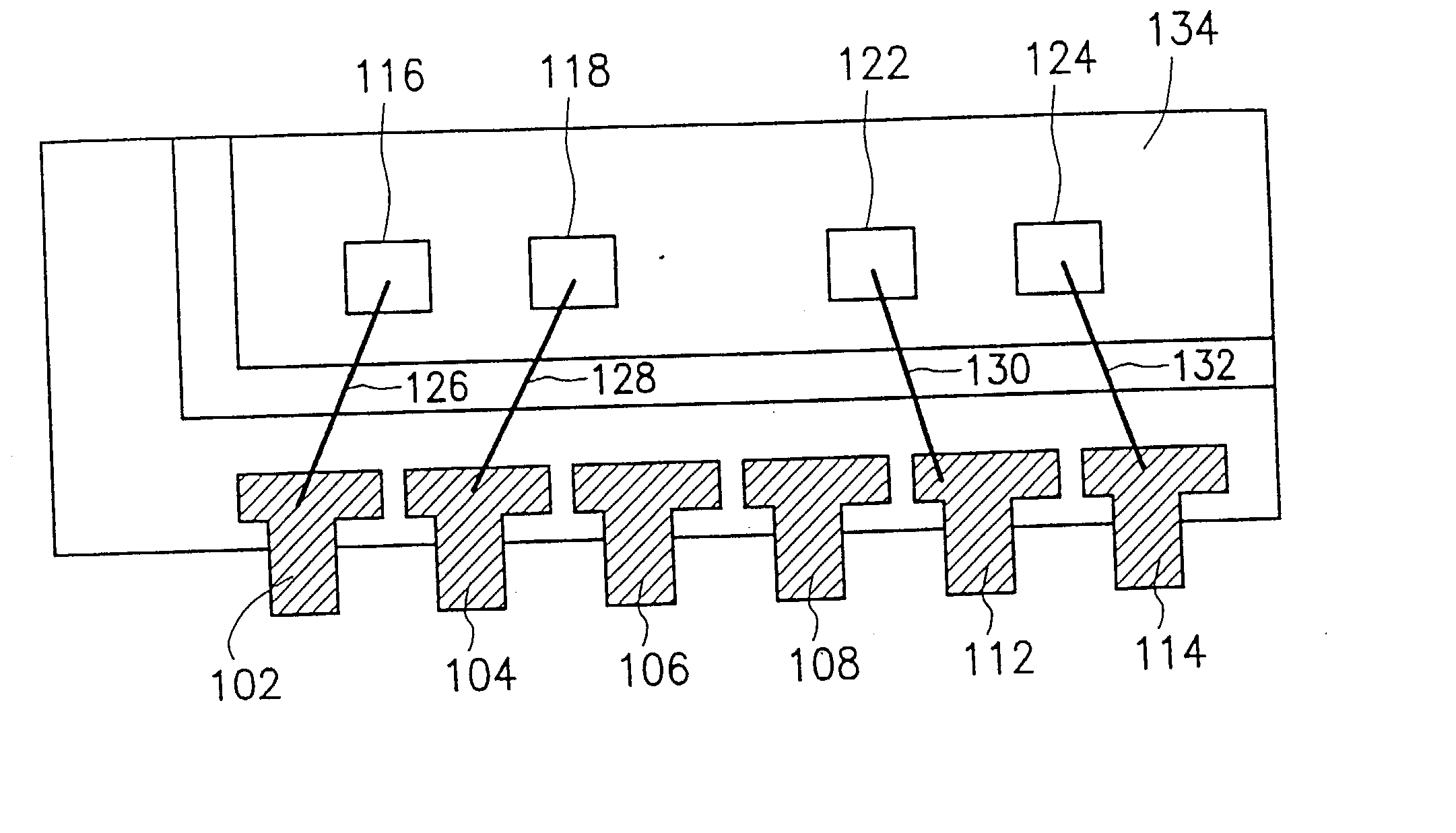

[0024] In accordance with the invention, the pins of an IC package are organized in such a manner that the no-connect pins are set apart into a plurality of groups or at least one group, with each group containing one single no-connect pin or a number of consecutive no-connect pins, and then each of the two pins that bound both sides of each no-connect pin group is assigned to be a power pin, such as a power pin V.sub.DD, a power pin V.sub.SS, or a ground pin GND, for electrically connect to a power bus V.sub.DD, a power bus V.sub.SS, or a ground bus GND of the IC chip. This arrangement is based on the fact that the pins that are connected to a power bus can better withstand the condition of its neighboring no-connect pin being subjected to an ESD stress of 5 kV. Therefore, in this case, the ESD protective circuitry for the power pins needs not be expanded while nonetheless retaining good ESD protective capability. 7File:

[0025] FIG. 3 is a schematic diagram depicting the pin-assignm...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More