Multi-chip stack package and fabricating method thereof

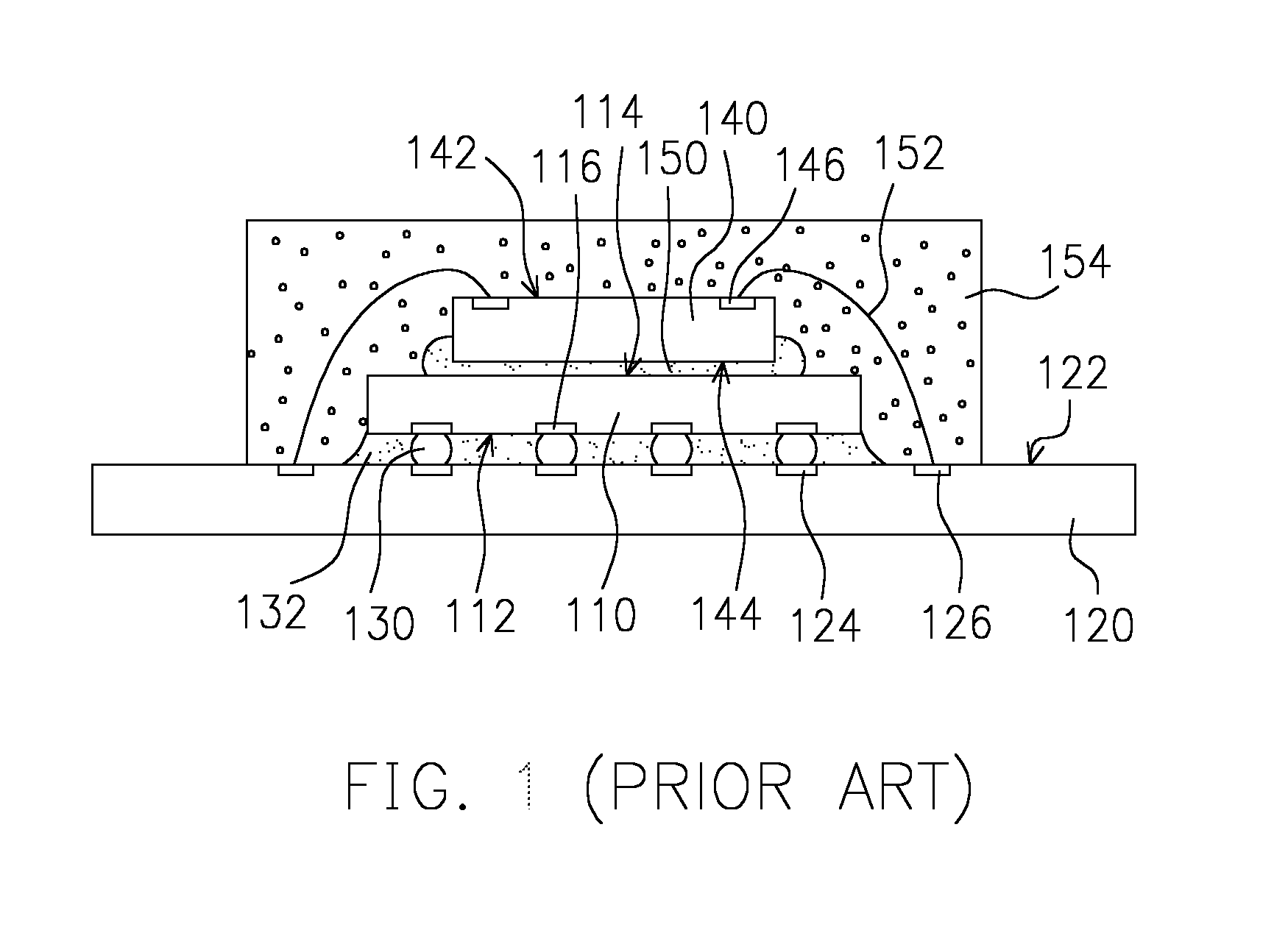

a technology of multi-chip stacks and fabrication methods, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical devices, etc., can solve the problem of adhesive material 150 bleedout, and achieve the effect of improving the bonding quality of multi-chip stacks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

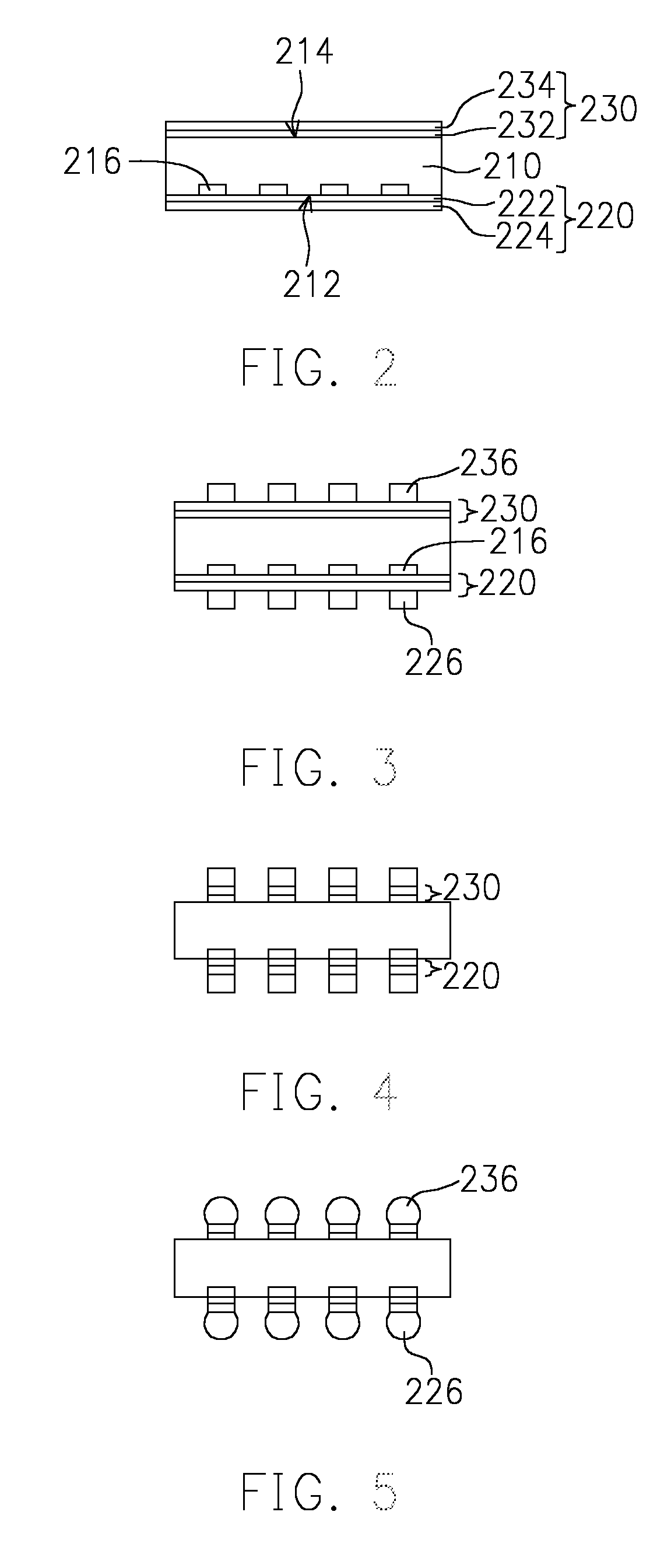

[0021] Reference will now be made in detail to the present preferred embodiments of the invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers are used in the drawings and the description to refer to the same or similar parts.

[0022] Figs. 2 to 11 are schematic cross-sectional views showing the progression of steps for fabricating a multi-chip stack package according to a first preferred embodiment of this invention. As shown in Fig. 2, a first chip 210 having a first active surface 212 and a first chip back surface 214 is provided. The first chip 210 further includes a plurality of first bonding pads 216 positioned on the first active surface 212 of the first chip 210. Thereafter, a process is carried out to form an under-bump-metallurgy layer. To form the under-bump-metallurgy layer, a sputtering process is conducted to form a first barrier layer 222 and a second barrier layer 232 over the first active surface 212 an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More