Semiconductor device, three-dimensional semiconductor device, and method of manufacturing semiconductor device

a semiconductor device and semiconductor technology, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of difficult to form through holes, difficulty in wire bonding and connecting with other electrodes, and increase in connection resistan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

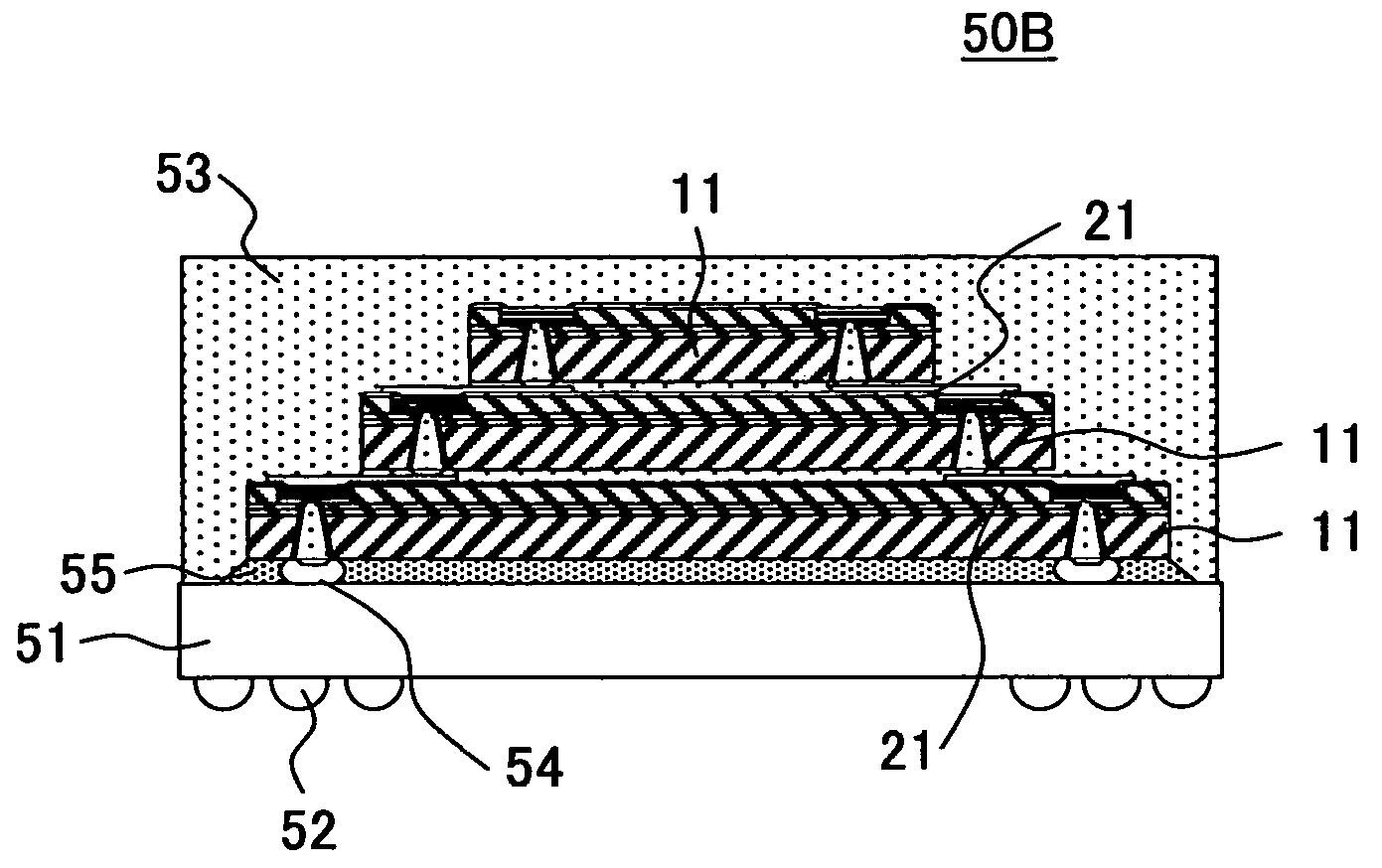

[0083]FIG. 1 illustrates the structure of a semiconductor device in accordance with a first embodiment of the present invention. FIG. 2 is a partially enlarged cross-sectional view of the semiconductor device.

[0084] The semiconductor device 10 shown in FIG. 1 has an electronic circuit unit (an integrated circuit unit) 13 that includes an active element, a passive element, and an electrode / wiring layer. The electronic circuit unit 13 is formed on a principal surface of a thin silicon semiconductor substrate 11. The wiring layer lead out from the electronic circuit unit 13 extends in an insulating layer, and is electrically connected to an electrode pad 15.

[0085] The semiconductor substrate 11 has a hole 16 formed at the location corresponding to the electrode pad 15. This hole 16 does not penetrate the electrode pad 15.

[0086] An embedded electrode 18 is provided in the hole 16 via an insulating layer 17 and a base (seed) metal layer 17a. The insulating layer 17 is formed to cover ...

second embodiment

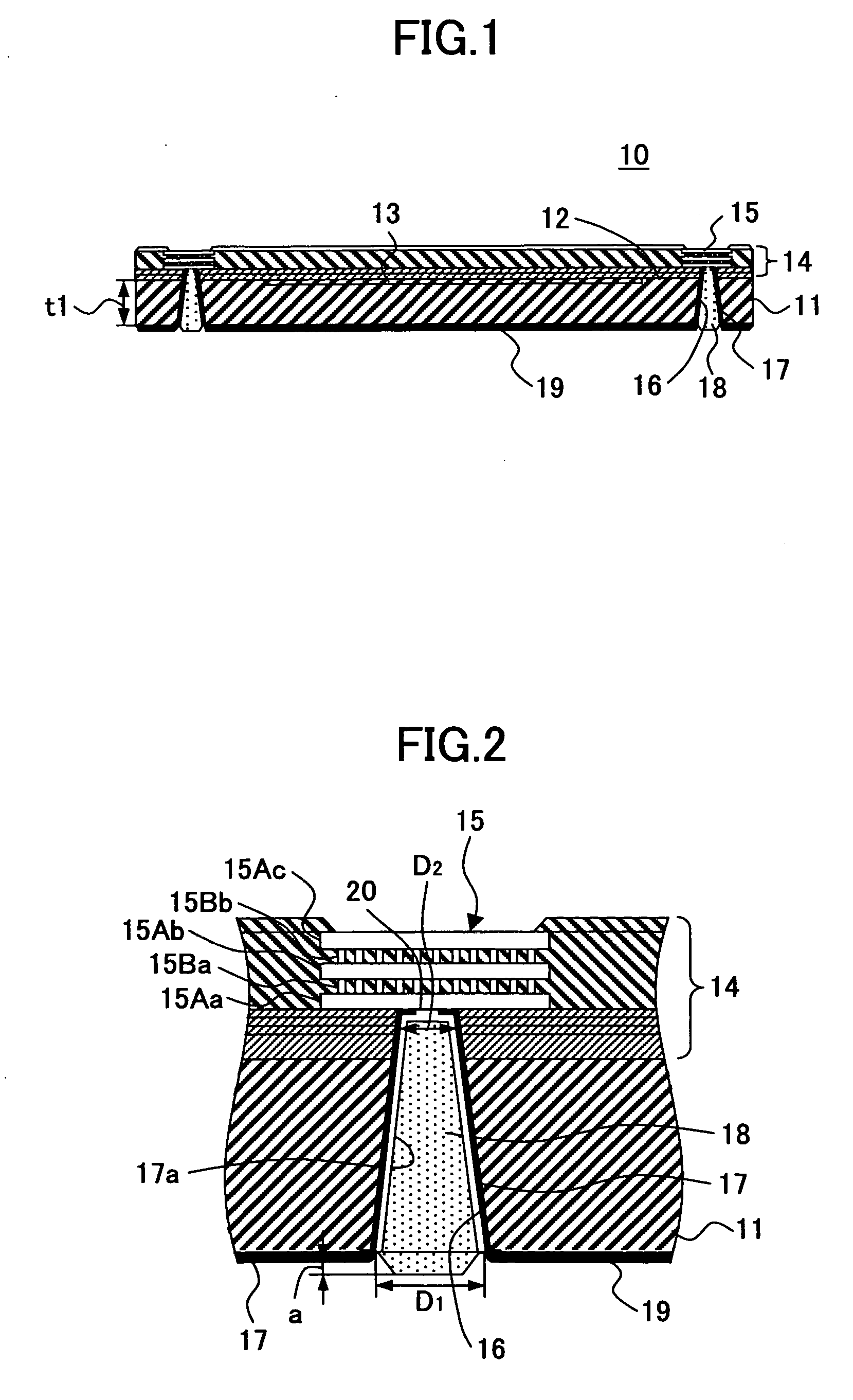

[0109]FIG. 3 illustrates the structure of a three-dimensional semiconductor device 50 as a second embodiment of the present invention. This three-dimensional semiconductor device 50 is formed with the semiconductor device 10 with the above described structure in accordance with the present invention.

[0110]FIG. 4 is an enlarged cross-sectional view of the substantial part of the semiconductor device 50, which is a semiconductor device laminated body.

[0111] In accordance with this embodiment, the semiconductor device 50 has an insulating resin sheet as a base member, and a supporting substrate (an interposer) 51 that has an electrode / wiring layer formed on the surface and / or in the inside thereof. A plural number (four (10-1 through 10-4) in FIGS. 3 and 4) of semiconductor devices 10 of the first embodiment are laminated and mounted on a principal surface of the supporting substrate 51. An external connection terminal 52 is provided on the other principal surface of the supporting s...

third embodiment

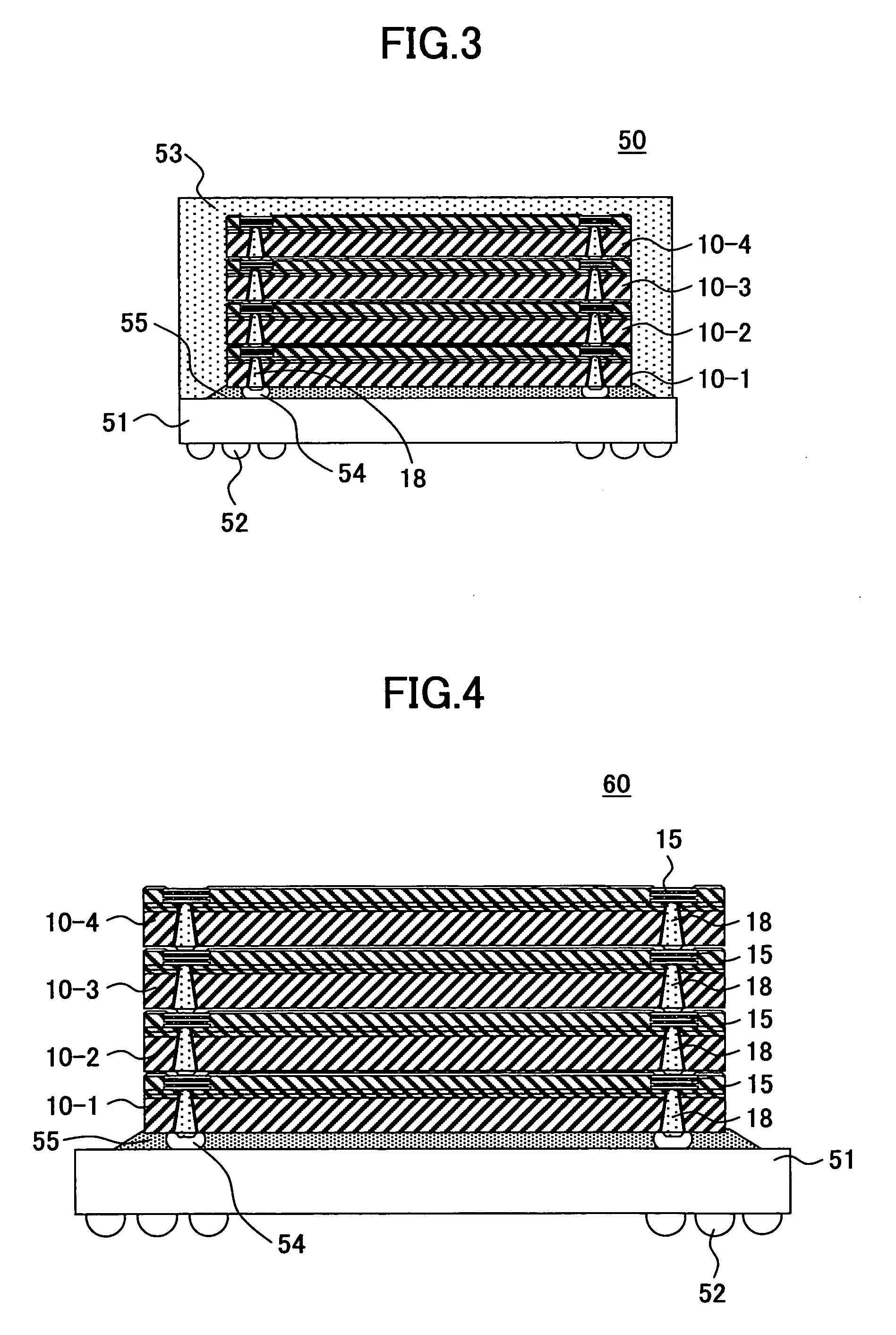

[0121]FIG. 5 illustrates a third embodiment of the present invention. The third embodiment is a modification of the three-dimensional semiconductor device having the semiconductor devices 10 in accordance with the present invention.

[0122] In this embodiment, a semiconductor device 50A has an insulating resin sheet as a base member, and a supporting substrate (an interposer) 61 that has an electrode / wiring layer formed on the surface and / or in the inside thereof. A plural number (four (10-1 through 10-4) in FIG. 5) of semiconductor devices 10 of the first embodiment are laminated and mounted on a principal surface of the supporting substrate 61. An external connection terminal 62 is provided on the other principal surface of the supporting substrate 61.

[0123] The laminated body of the semiconductor devices 10 is packaged and sealed with epoxy resin 63.

[0124] In FIG. 5, reference numeral 64 indicates a solder bump, and reference numeral 65 indicates an underfill that is made of res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More