Multilayer printed wiring board and process for producing the same

a wiring board and multi-layer technology, applied in the direction of printed circuit manufacturing, printed circuit aspects, semiconductor/solid-state device details, etc., can solve the problems of wasteful material costs, little design freedom for wiring, and assembling processes of rigid portions on inner and outer layer rigid substrates. achieve the effect of reducing material costs, reducing substrate capacity, and high wiring design freedom

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

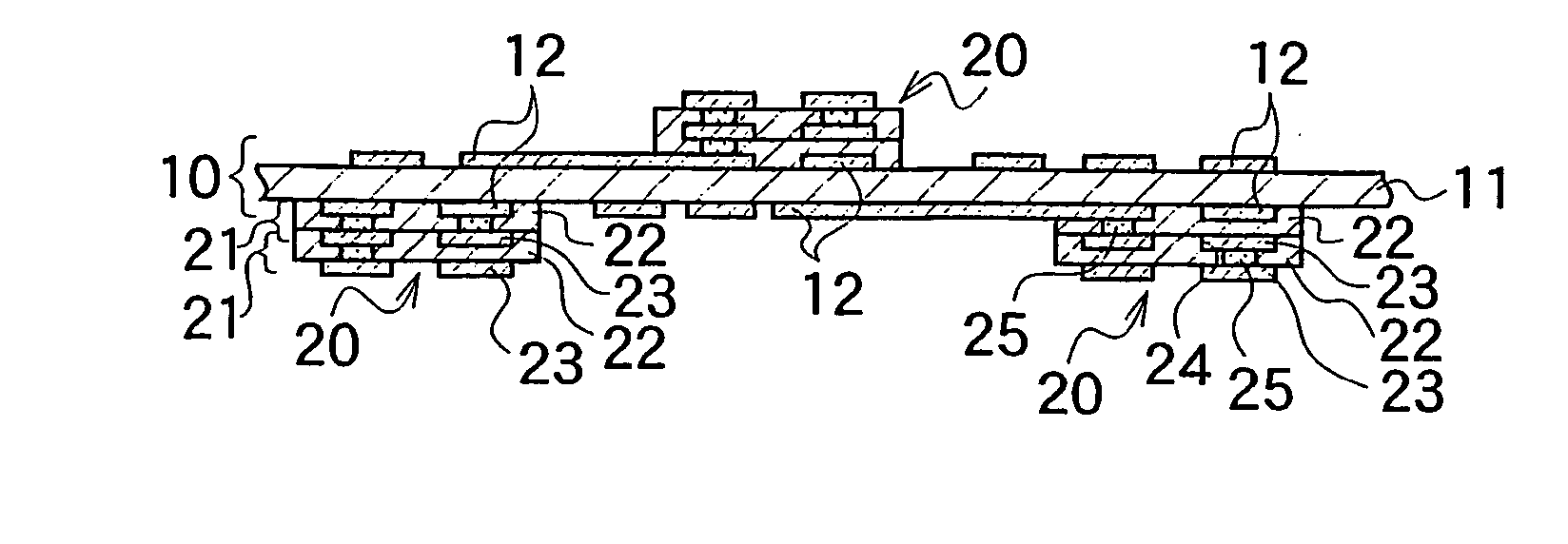

[0064]FIGS. 3 and 4 show a basic mode of a multi-layer wiring board in accordance with a first embodiment of the present invention. In the multi-layer wiring board of the present embodiment, at a plurality of portions on the surface and rear surface of a motherboard (base material) 10, partial wiring boards (multi-layer portions) 20, which have outer shapes that have been preliminarily formed into predetermined shapes, and will be described later, are bonded so as to form an island shape. Here, the island shape is defined as a state in which the peripheral sides of the partial wiring boards 20 are not coincident with the peripheral sides of the motherboard 10 so that the partial wiring boards 20 are placed inside the area which is defined by the peripheral sides of the motherboard 10. Additionally, the predetermined shapes are determined on the request of designing the motherboard.

[0065] The partial wiring boards 20 are formed as follows: a plurality of resin base materials 21 with...

first embodiment-second modified embodiment

[0096] Referring to FIGS. 14A to 14E, a manufacturing method for a multi-layer wiring board in accordance with a second modified embodiment of the first embodiment will be described below. Here, in FIG. 14 also, those parts corresponding to those shown in FIG. 12 are indicated by the same reference numerals as those of FIG. 12 and the description thereof is omitted.

[0097] As shown in FIG. 14A, a motherboard FPC 60 has a wiring circuit 61 formed thereon and is provided with a cover layer 62 with openings (opening sections 62A and 62B) formed at portions to receive laminated layers that is formed on the surface thereof. Two layers of resin base materials 57 with single-sided wiring circuits that have an outer shape that has been formed into a predetermined shape, as shown in FIG. 9, are positioned, and then superposed thereon. Thereafter, these members are subjected to heating and pressing processes by a vacuum heat pressing machine under a degree of vacuum of not more than 1 kPa so ...

second embodiment

[0101] With reference to attached Figures, a second embodiment of the present invention will be described below.

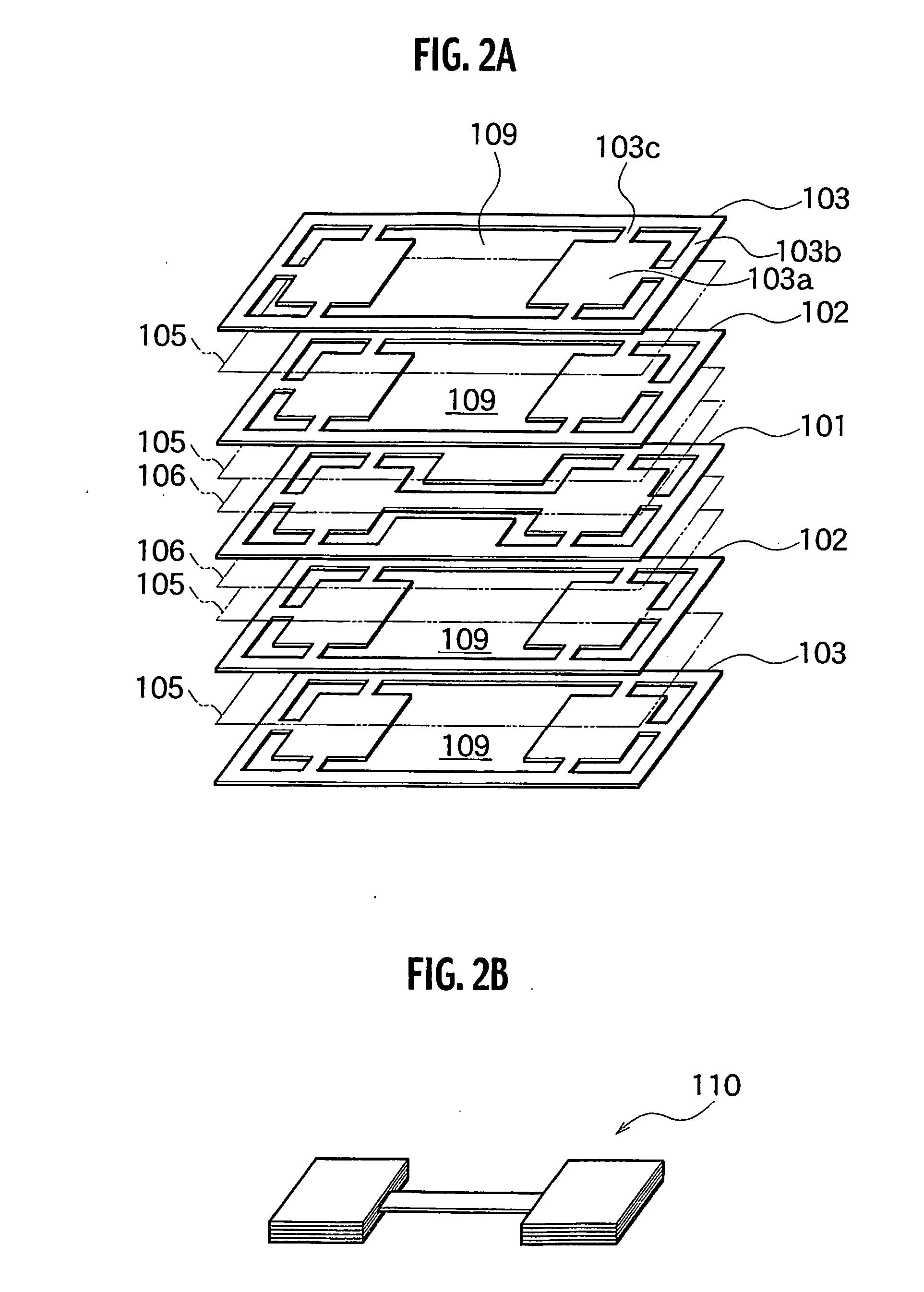

[0102]FIGS. 15 and 16 show a second embodiment of a multi-layer wiring board in accordance with the present invention.

[0103] In the multi-layer wiring board of the present embodiment, at a plurality of portions on the surface and rear surface of a motherboard (base material) 210, partial wiring boards (multi-layer portions) 220, which have outer shapes that have been preliminarily formed into predetermined shapes, are bonded so as to form an island shape. Here, the island shape is defined as a state in which the peripheral sides of the partial wiring boards 220 are not coincident with the peripheral sides of the motherboard 210 so that the partial wiring boards 220 are placed inside the area determined by the peripheral sides of the motherboard 210. Here, the predetermined shapes are determined by requirements in designing the motherboard.

[0104] The partial wiring board...

PUM

| Property | Measurement | Unit |

|---|---|---|

| elastic modulus | aaaaa | aaaaa |

| glass transition temperature | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More