Semiconductor device fabrication methods employing substantially planar buffer material layers to improve the planarity of subsequent planarazation processes

a semiconductor device and buffer material technology, applied in the direction of capacitors, electrical appliances, basic electric elements, etc., can solve the problems that the surface of the material or materials that fill the recesses and may cover the surface of the semiconductor device structure has not yet been chemically-mechanically planarized, and achieves the effect of reducing the depth of material

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

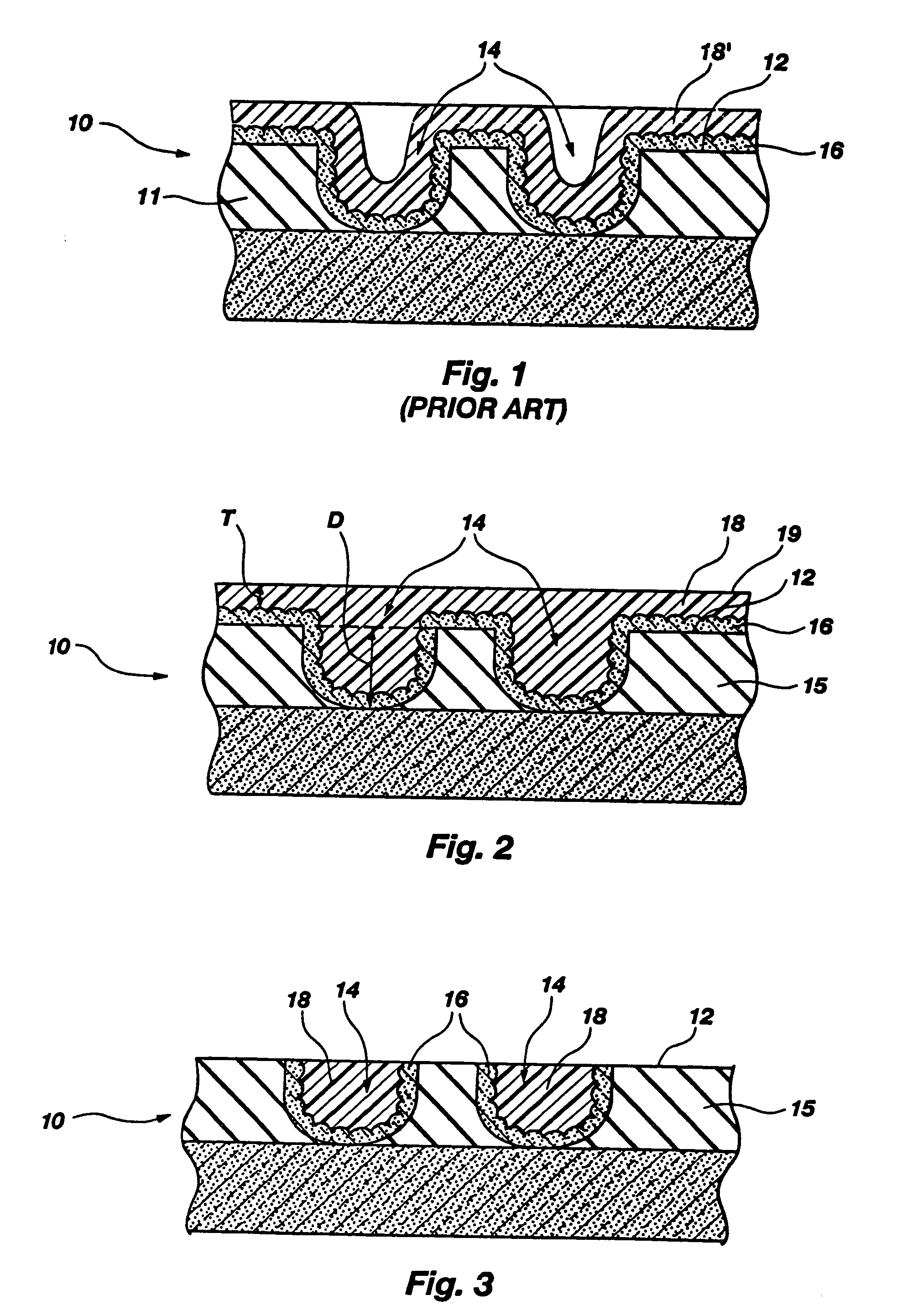

[0041] With reference to FIG. 2, a semiconductor device structure, in this case a stacked capacitor structure 10, incorporating teachings of the present invention is illustrated. Stacked capacitor structure 10 includes a surface 12 with containers 14 recessed, or formed, in surface 12. As illustrated, surface 12 and containers 14 are lined with a layer 16 of conductively doped hemispherical grain silicon. Stacked capacitor structure 10 also includes a mask layer 18 of a polymer material (e.g., polyimide or photoresist) disposed over layer 16. Mask layer 18 substantially fills containers 14 and has a substantially planar exposed surface 19. The thickness T of portions of mask layer 18 overlying surface 12 is less than the depth D of containers 14 and, preferably, is less than about half of depth D.

[0042] Stacked capacitor structure 10, including the conductively doped hemispherical grain silicon layer 16 thereof, may be fabricated by known processes, such as those disclosed in U.S. ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| stress | aaaaa | aaaaa |

| electrical insulator | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More