Apparatus and method to trace high performance multi-issue processors

a processor and multi-issue technology, applied in the field of on-chip debugging, can solve problems such as difficulty in tracing sequential execution of programs, and achieve the effect of facilitating tracing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Embodiments of the invention are discussed in detail below. While specific implementations are discussed, it should be understood that this is done for illustration purposes only. A person skilled in the relevant art will recognize that other components and configurations may be used without departing from the spirit and scope of the invention.

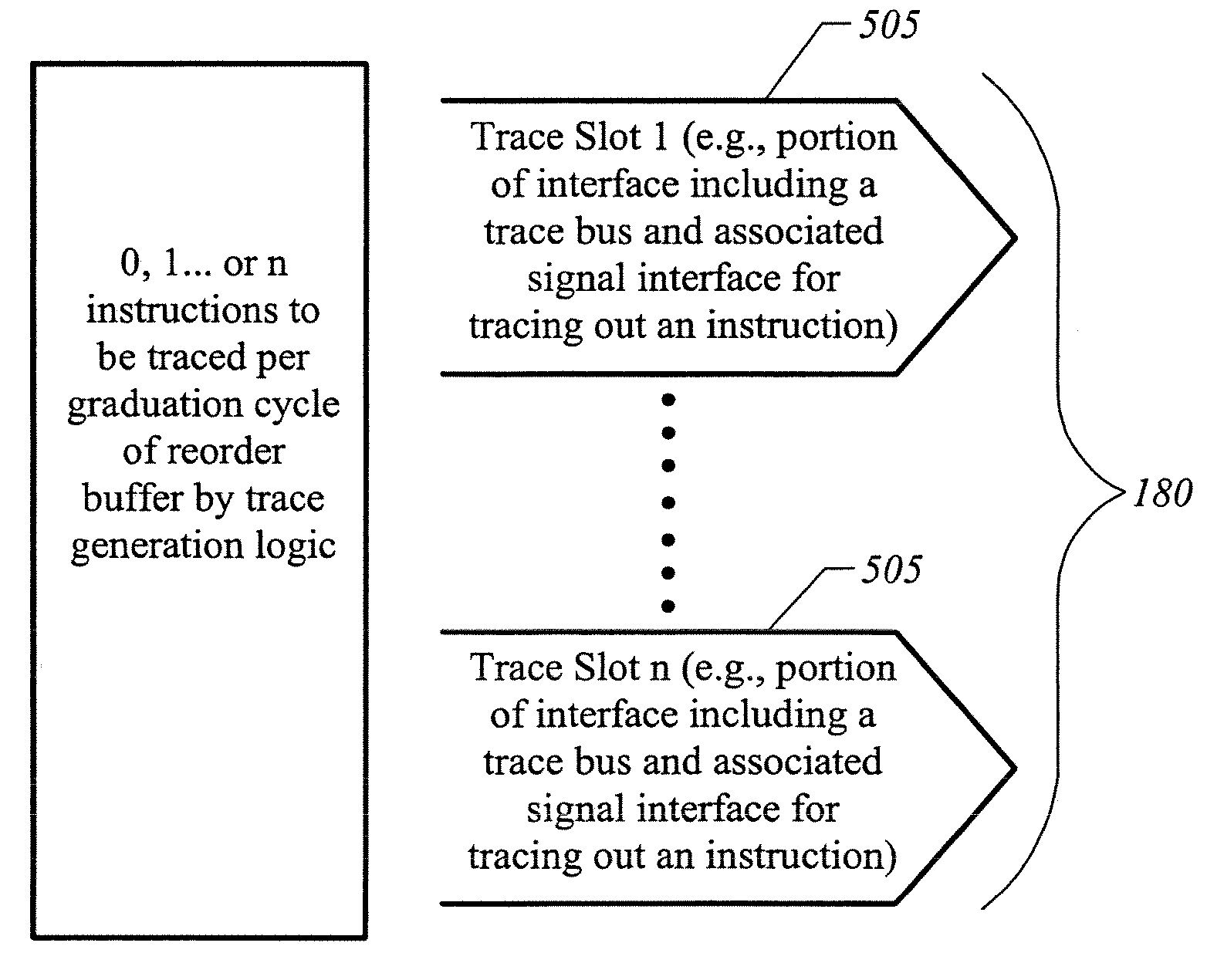

[0021]FIG. 1 illustrates a tracing system 100 that includes on-chip components identified as microprocessor core 110, trace generation logic (TGL) 120, trace control block (TCB) 130, and test access port (TAP) controller 140. TGL 120 can be embodied as part of microprocessor core 110. TGL 120 is generally operative to generate program counter (PC) and data trace information based on the execution of program code in one or more pipelines within microprocessor core 110. In some embodiments, microprocessor core 10 is a high performance multi-issue microprocessor having one or more features that may disrupt sequential execution of instruct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More