Modulation of stress in stress film through ion implantation and its application in stress memorization technique

a stress film and stress technology, applied in the manufacturing of semiconductor/solid-state devices, basic electric elements, electrical equipment, etc., can solve the problems of signal propagation time and susceptibility, the length of propagation paths, and the cost of devices containing chips, so as to increase the stress in the channel region

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

I. Introduction

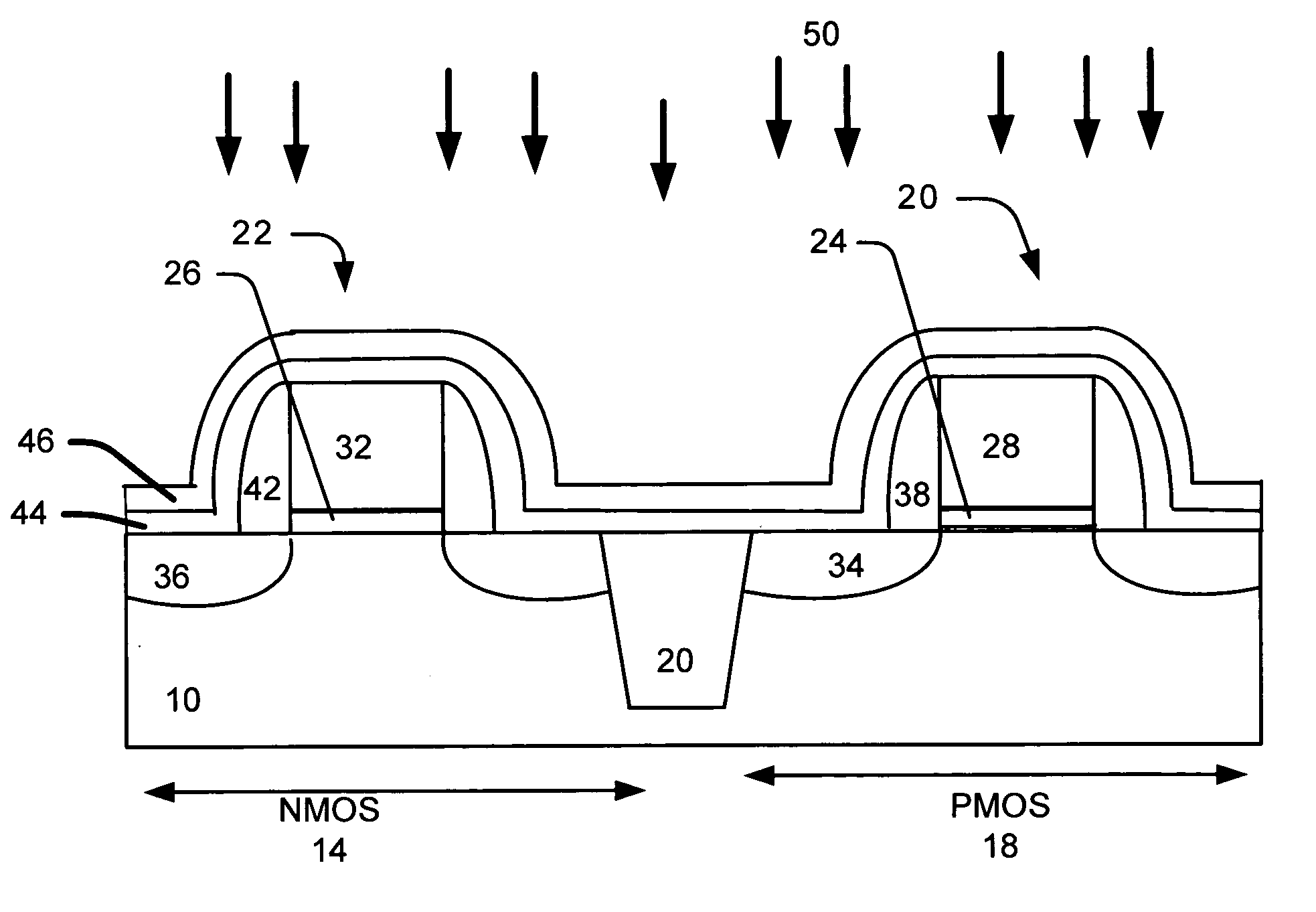

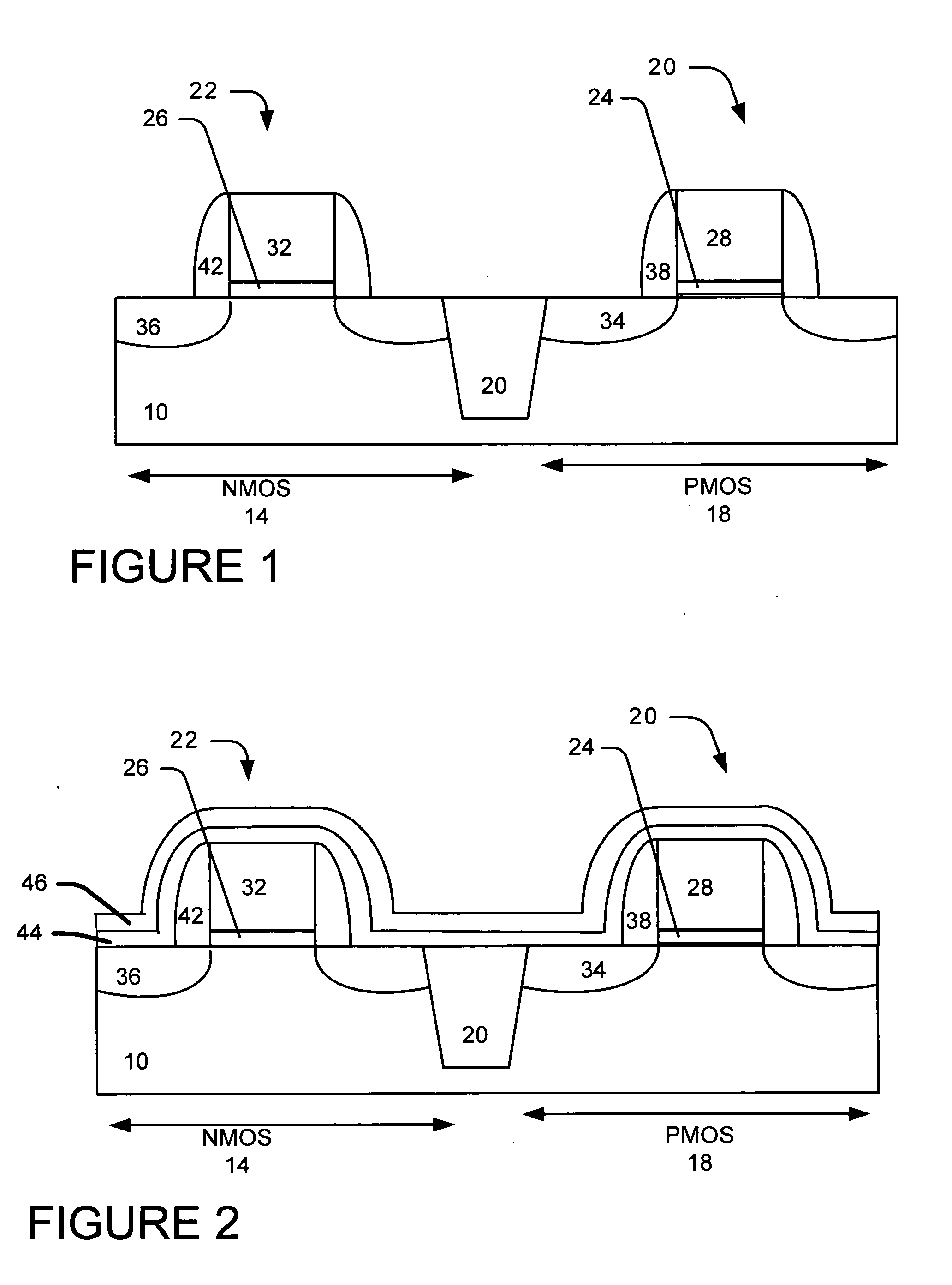

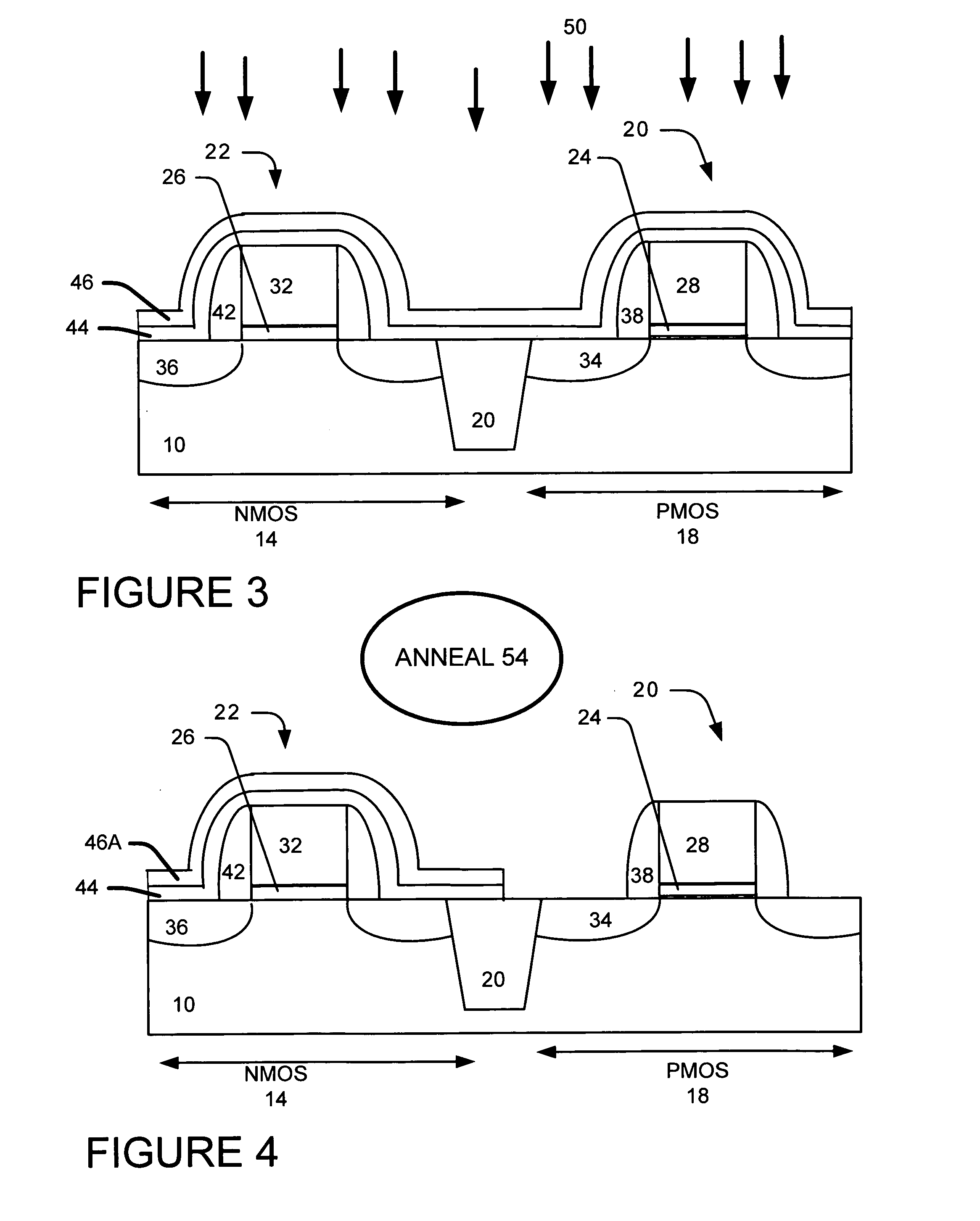

[0032] Some example embodiments of the invention provide a method to improve the performance of MOS devices by increasing the stress in the channel region. An example embodiment for a NMOS Transistor is to form a tensile stress layer (e.g., SiN) over a NMOS transistor. [0033] A gate dielectric layer and poly gate are formed. [0034] An ion implant is performed to amorphorize the gate so that the gate is comprised of amorphous Si. [0035] A important Ion implantation (I / I) is performed on the (SiN) stress layer that will initially relax the stress film but when combined with a subsequent anneal, will increase the tensile stress in the stress film higher than the initial starting stress. [0036] Then an anneal is performed that can serve two purposes: (i) increasing the tensile stress of the implanted stress film, (ii) crystallizes the silicon containing gate thus increasing the amount of stress from the stress layer that the gate retains / memorizes.

[0037] The Si containin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More