Data processor

a data processor and data technology, applied in the field of data processors, can solve the problems that the cpu (central processing unit) taking no measures against overflow may fall into undesirable operation stop, and achieve the effect of free, smooth and efficient restoration from interrupts and excellent applicability to multitask processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

>

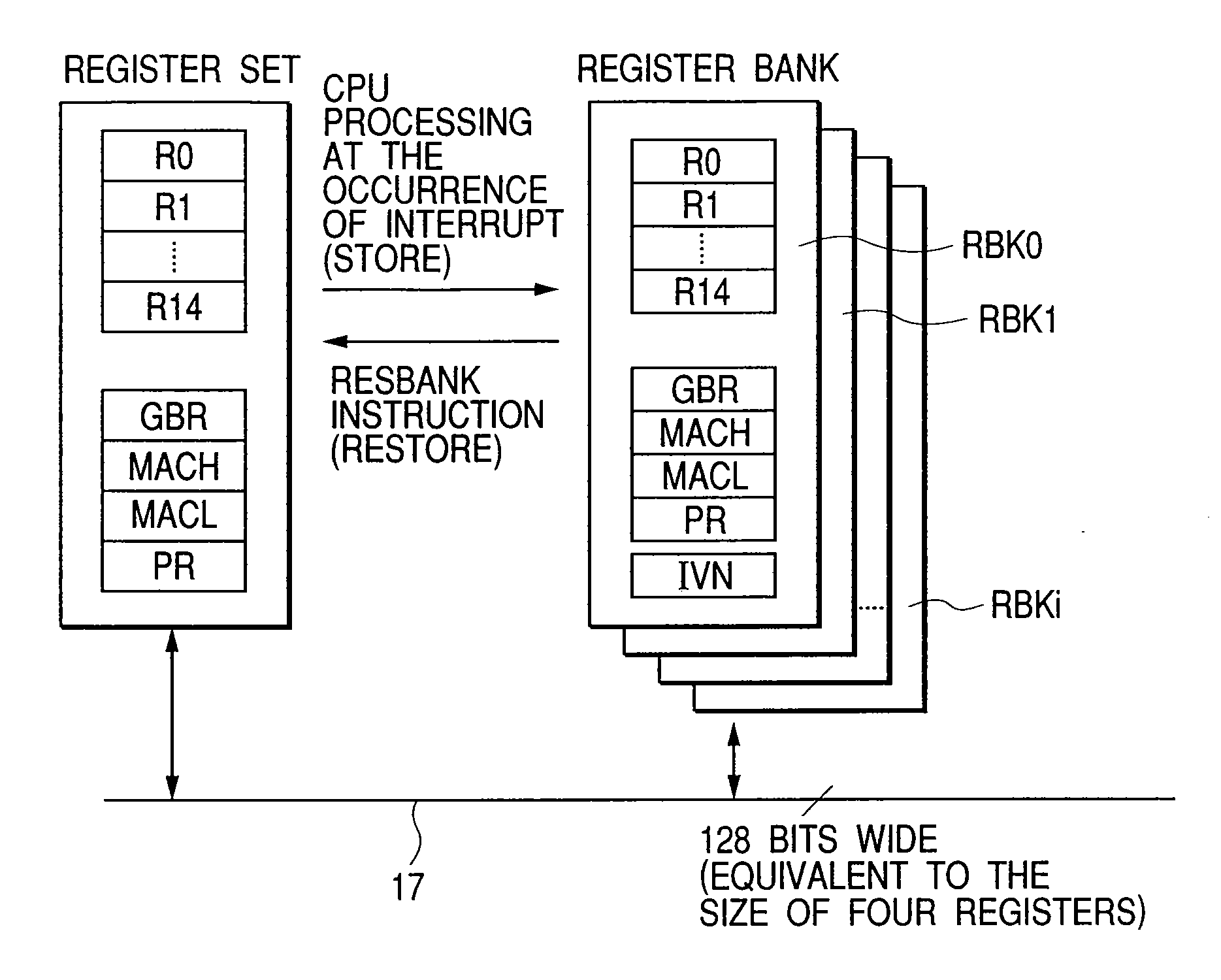

[0035]FIG. 1 is a block diagram showing a data processor according to an embodiment of the present invention. A data processor 1 shown in the figure is formed on a single semiconductor board (semiconductor chip) such as a single-crystal silicon by, e.g., CMOS integrated circuit manufacturing technology.

[0036] The data processor 1 shown in the figure comprises: a CPU 2; a bank memory 3; an interrupt controller (INTC) 4; a bus state controller (BSC) 5; a ROM (read only memory) 6; and a RAM 7.

[0037] The CPU 2 is connected to the RAM 7 over a data bus 10 and a data address bus 11, and to the ROM 6 over an instruction data bus 12 and an instruction address bus 13. The RAM 7 is used as a work area or data temporary storage area of the CPU 2. The ROM 6 stores operation programs of the CPU 2 such as OS and control programs. The buses 10 to 13 are interfaced via the bus state controller 5 to a peripheral data bus 14 and a peripheral address bus 15, where external input-output circuits suc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More