Clock buffer circuit of semiconductor device

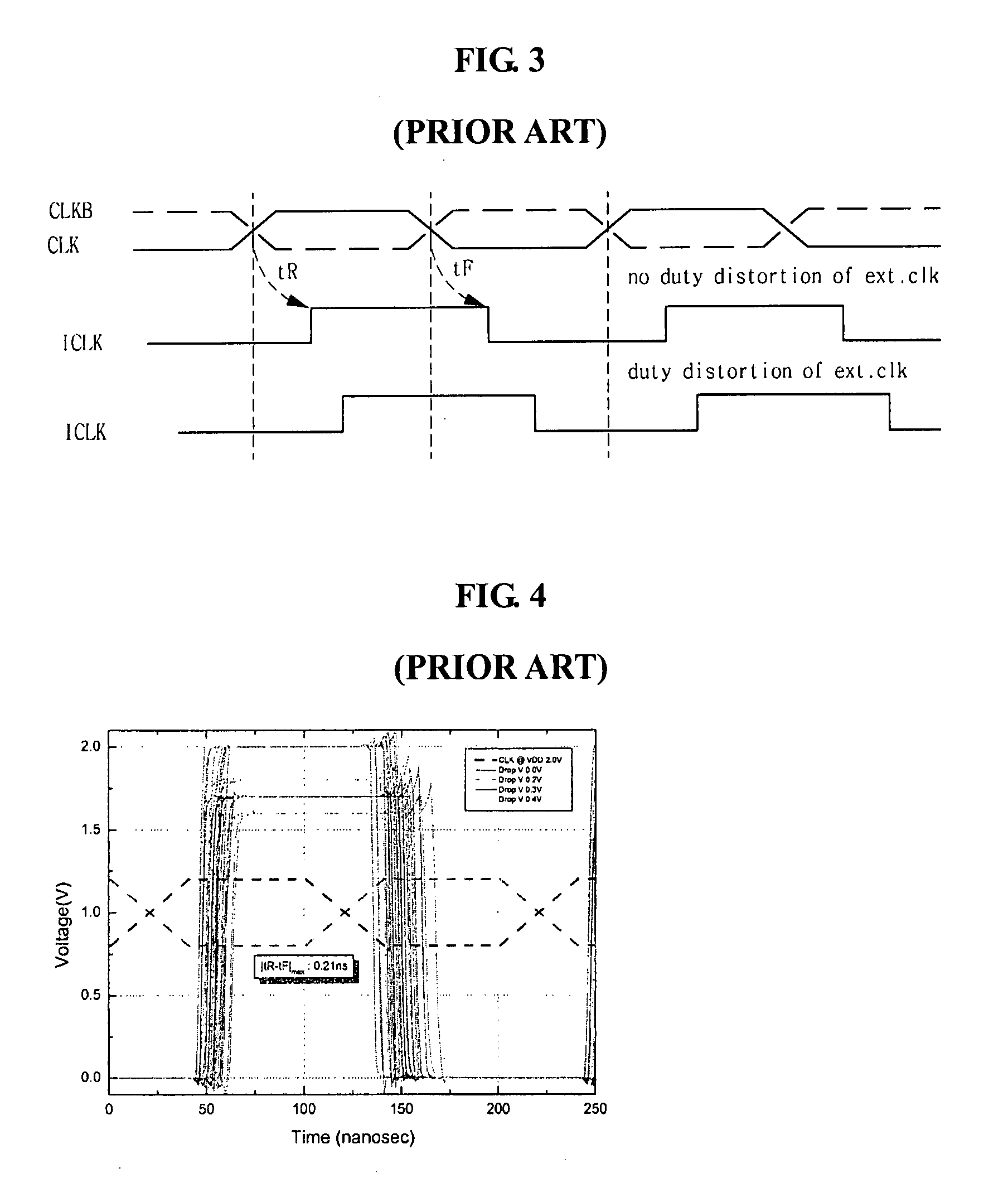

a technology of clock buffer and semiconductor device, which is applied in the direction of generating/distributing signals, instruments, pulse techniques, etc., can solve the problems of duty distortion deteriorating the high-speed operation of a memory device, the dcc accuracy is reduced, and the characteristics of tr/tf may not be equal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026]Preferred embodiments of the present invention will now be described in detail with reference to the accompanying drawings.

[0027]A clock buffer circuit of a semiconductor device according to the present invention is adapted to receive an external clock signal and generate an internal clock signal with no duty distortion, so that external parameters to be corrected by a duty correction circuit (DCC) can be reduced, resulting in an increase in accuracy of the DCC. Therefore, it is possible to improve the high-speed operation and reliability of a memory device.

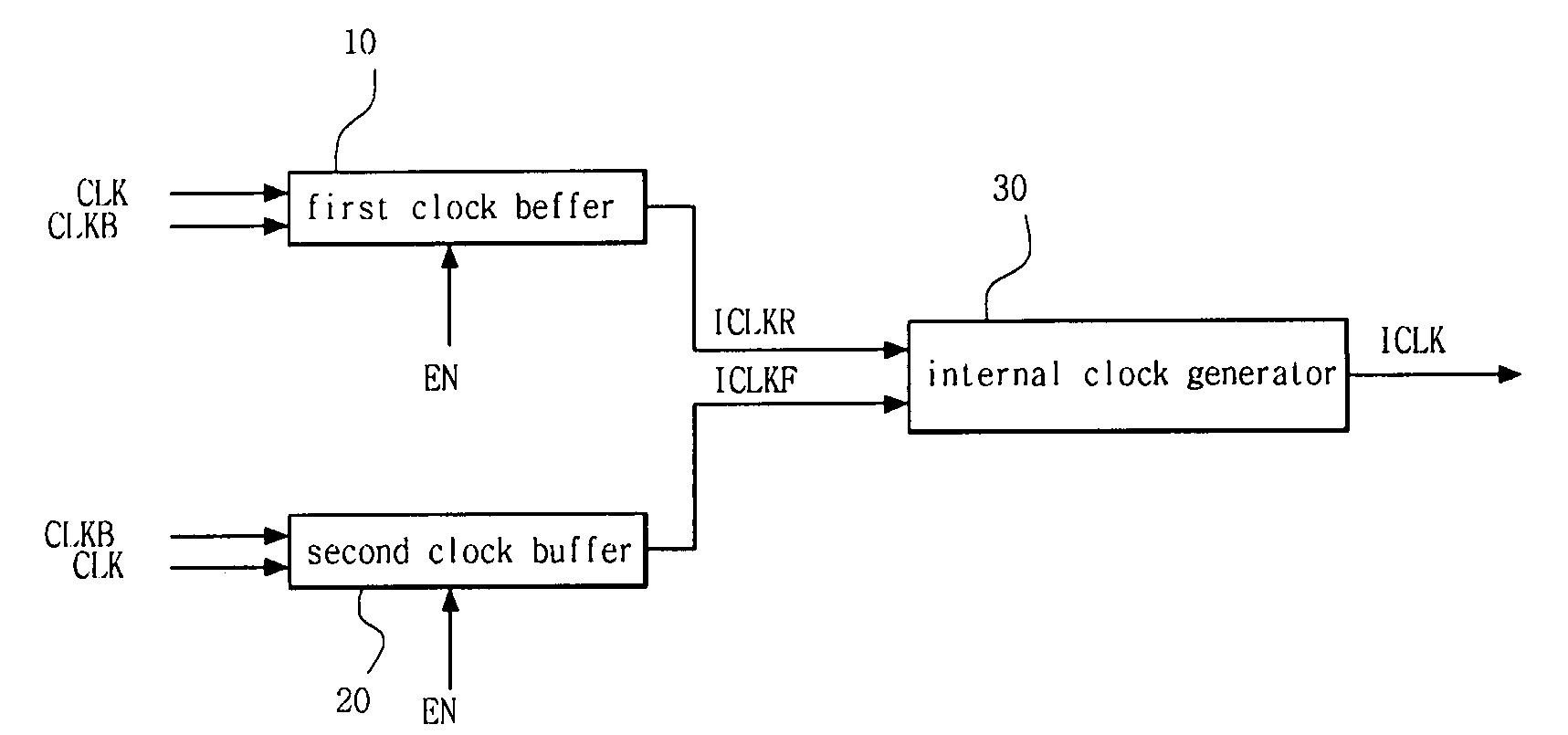

[0028]FIG. 5 is a block diagram showing the configuration of a clock buffer circuit according to an exemplary embodiment of the present invention, and FIG. 6 is a detailed circuit diagram of the clock buffer circuit of FIG. 5.

[0029]As shown in FIG. 5, the clock buffer circuit according to this embodiment comprises a first clock buffer 10 for receiving and buffering a normal-phase clock signal CLK, a second clock buffer 20 f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More