Level shifter having low duty cycle distortion

A level converter, level technology, applied in electrical components, generating electrical pulses, pulse technology and other directions, can solve problems such as large duty cycle distortion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

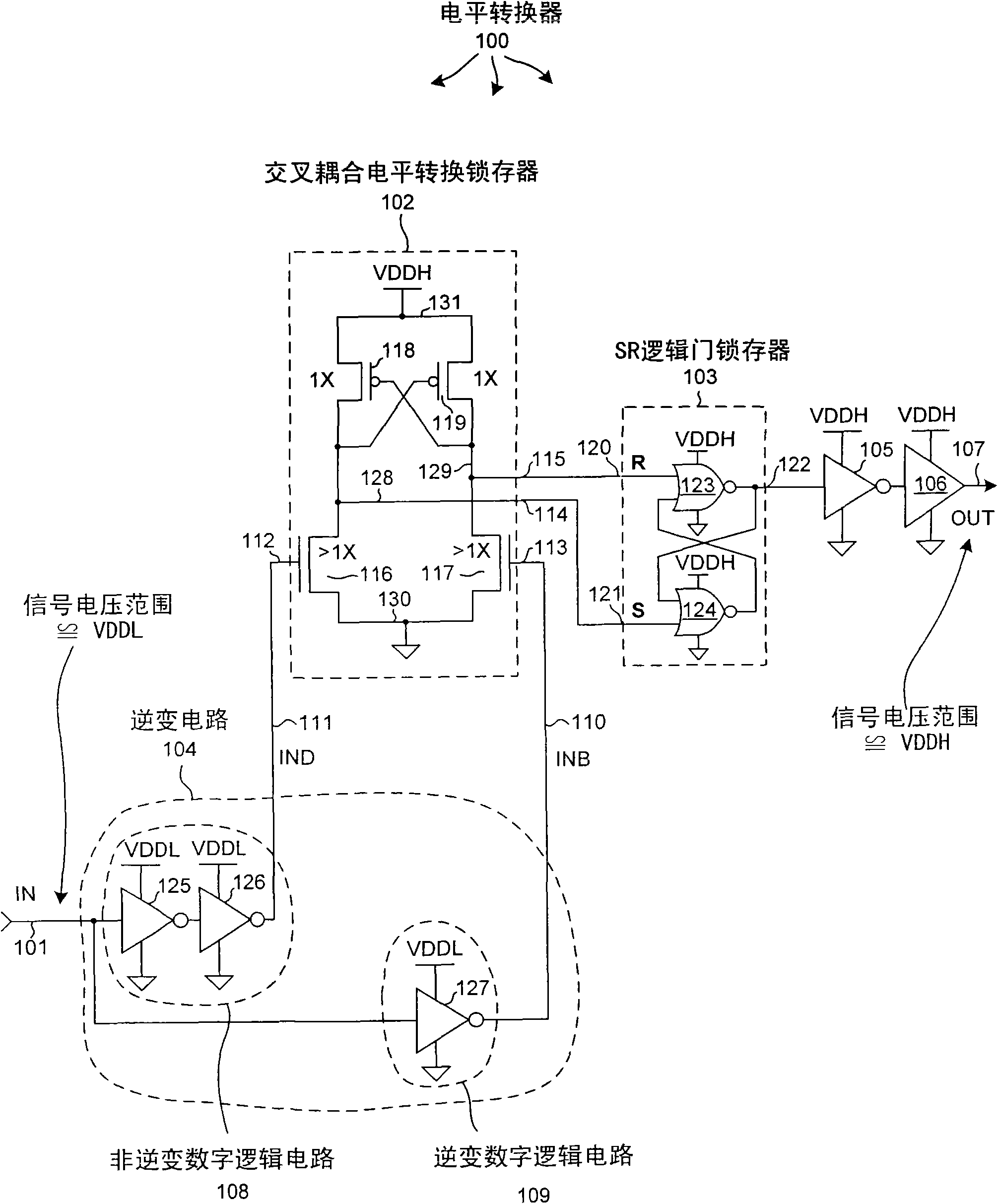

[0022] image 3 is a simplified diagram of a level shifting circuit according to one novel aspect. The level shift circuit 100 includes: an input node 101, a cross-coupled level shift latch 102, a set-reset (SR) logic gate latch 103, an inverter circuit 104, an inverter 105, a buffer 106, and an output Node 107. The digital input signal IN is received on input node 101, then level shifted and output on node 107 as a digital output signal OUT. The digital input signal IN transitions within a first signal voltage range (eg, from ground potential to a VDDL voltage of about 1.2 volts). The digital output signal OUT transitions within the second signal voltage range (eg, from ground potential to a VDDH voltage of approximately 1.8 volts). The level shifting circuit 100 is implemented in complementary logic including P-channel field effect transistors and N-channel field effect transistors.

[0023] The inverter circuit 104 includes a non-inverting digital logic circuit 108 and a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More