Flexible instruction processor systems and methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[0344]In a first embodiment a FIP JVM has been developed which utilises shared segregated resources. This embodiment provides good area utilisation, but at the expense of speed, because of routing congestion.

second embodiment

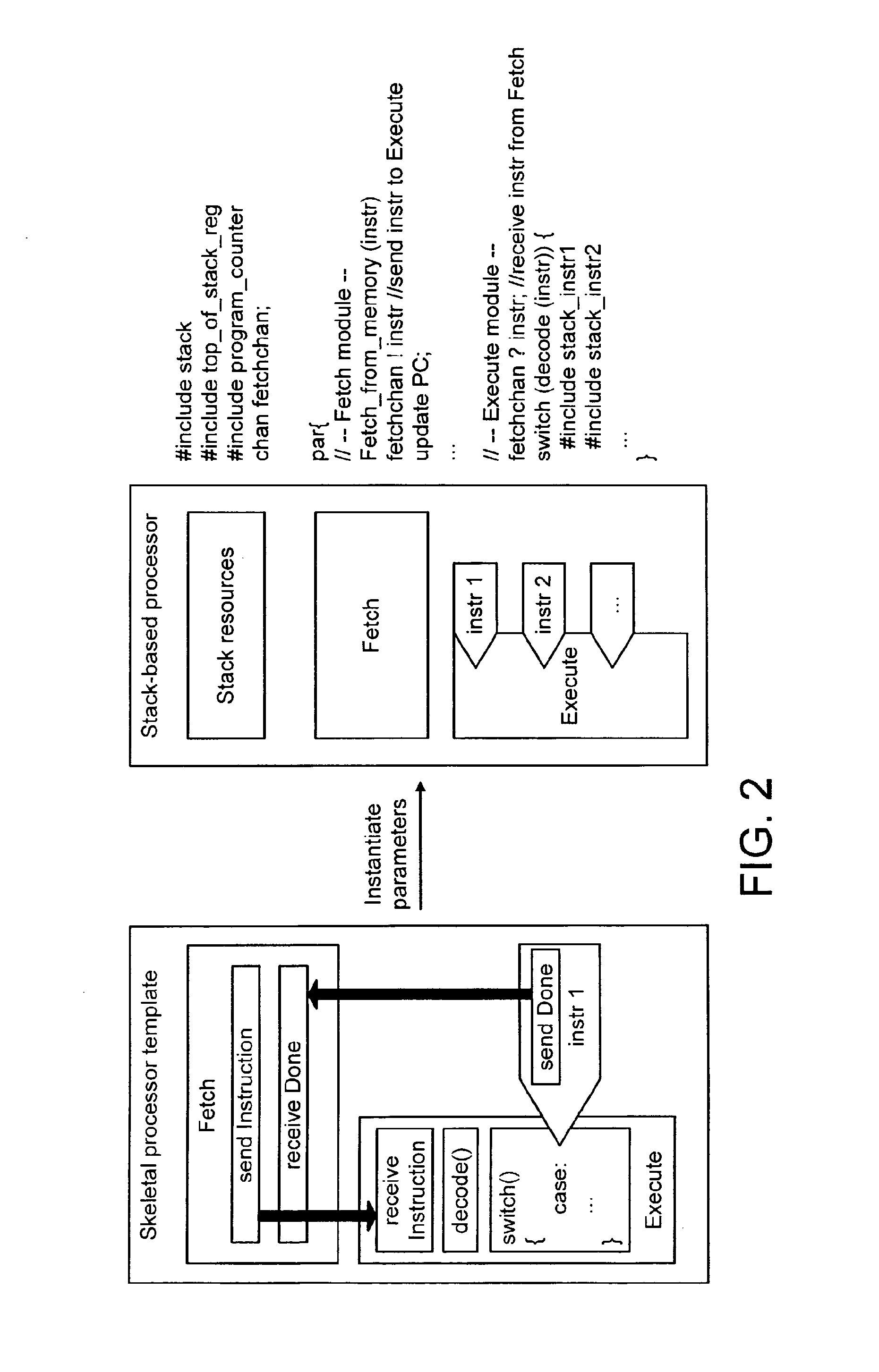

[0345]In a second embodiment a FIP JVM has been developed which utilises two stages of pipelining and only shares irreplaceable resources, such as the stack and main memory. Stack-based processors are intrinsically sequential. Speed optimisation of the FIP JVM introduces parallelism which is manifested as register-style instruction implementations.

third embodiment

[0346]In a third embodiment a FIP JVM has been developed which incorporates deeper pipelines for certain instructions and ‘register’ style improvements, such as having top-of-stack registers. The top-of-stack registers are replicated. Instructions can be read from different top-of-stack registers, but are written back to the stack directly. Replicated registers are updated during the fetch cycle. Most instructions are processed by four pipeline stages, although certain instructions, such as the instruction for invoking functions, require deeper logic and the implementation of those instructions has been partitioned into five or six pipeline stages. Routing has also been pipelined to reduce the effects of congestion.

[0347]These FIP JVM embodiments demonstrate trade-offs between possible parameterisations.

[0348]Maximising sharing methods for re-programmable hardware through conventional resource sharing may introduce significant routing overheads. Congestion management is necessary to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More