Operating voltage tuning method for static random access memory

a random access memory and operating voltage technology, applied in static storage, information storage, digital storage, etc., can solve the problems of not providing enough information to shmoo test, designer's difficulty in adjusting corresponding process parameters, and shmoo test also cannot provide information regarding whether, so as to achieve the effect of lowering the operating voltage of the sram

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032]An illustration on the operating voltage tuning method for an SRAM according to the present invention is provided below along with several embodiments accompanied with diagrams for the better comprehension and implementation by those of ordinary skill in the art.

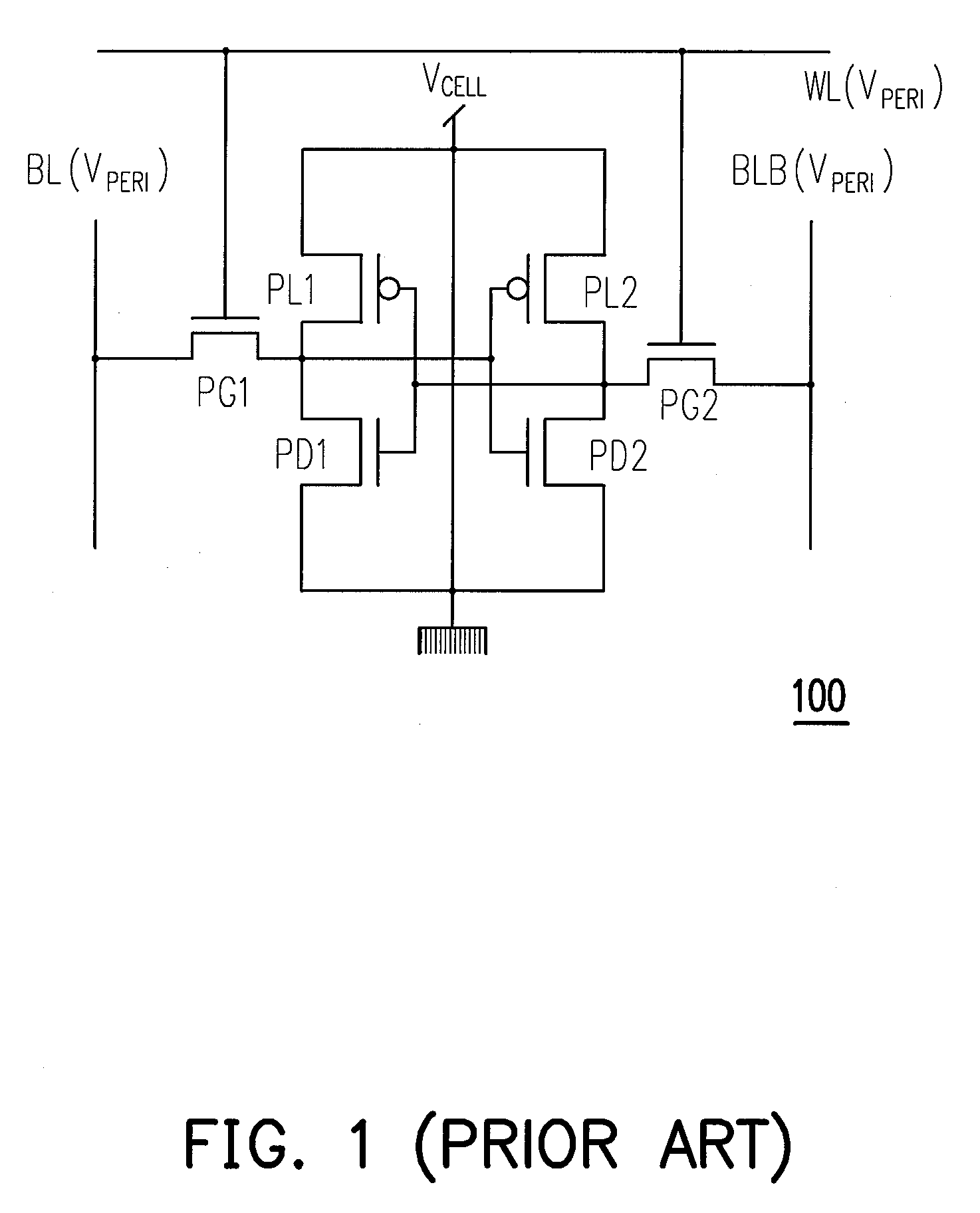

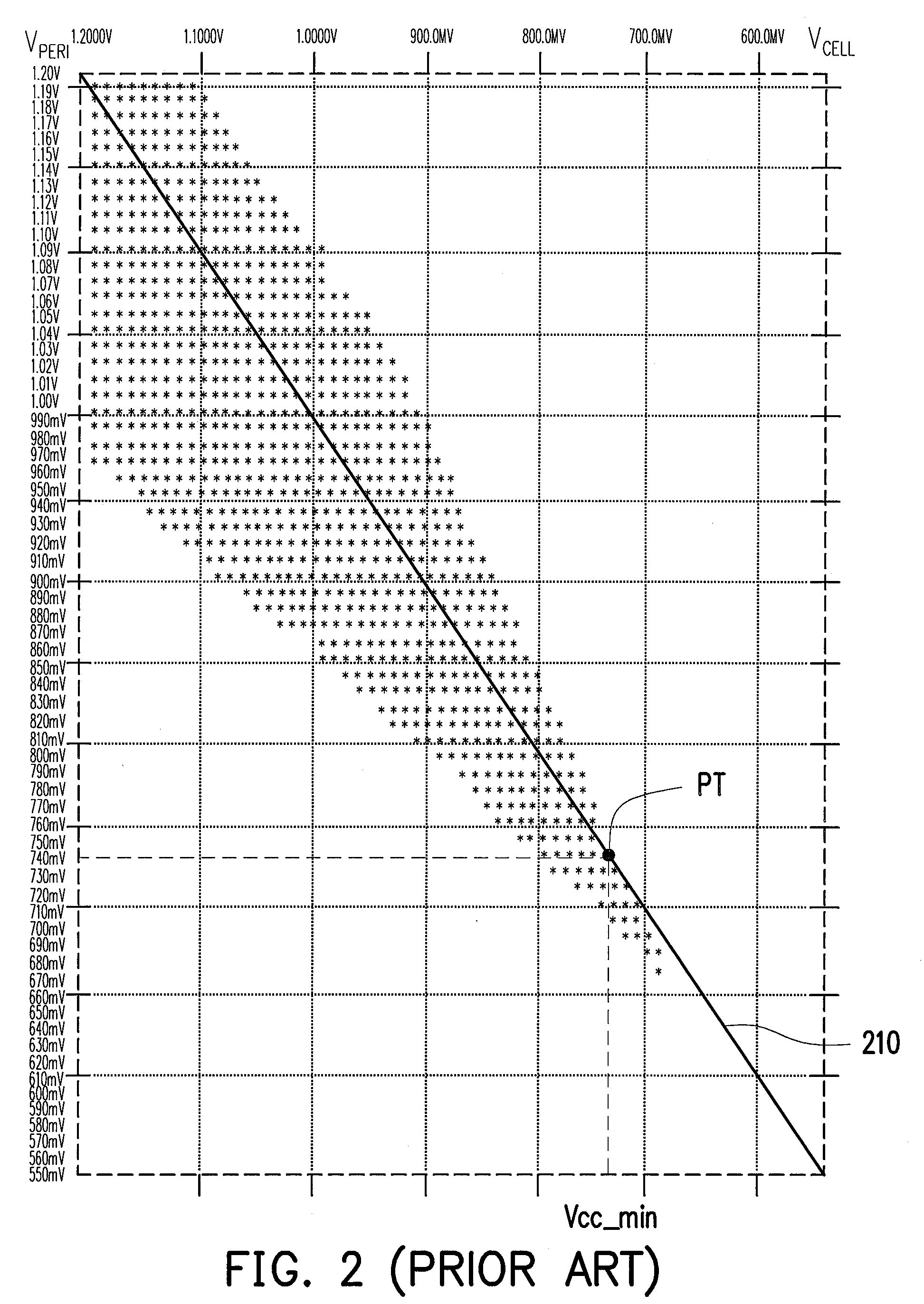

[0033]Referring simultaneously to FIG. 1 and FIG. 3A, FIG. 3A is a flow chart illustrating the operating voltage tuning method for an SRAM according to a first embodiment of the present invention. Although an SRAM 100 is considered as a circuit under test throughout the specification, those of ordinary skill in the art should realize that the SRAM 100 merely represents an SRAM having millions of bits or more. The actual circuit under test may be a combination of SRAM having an arbitrary number of bits.

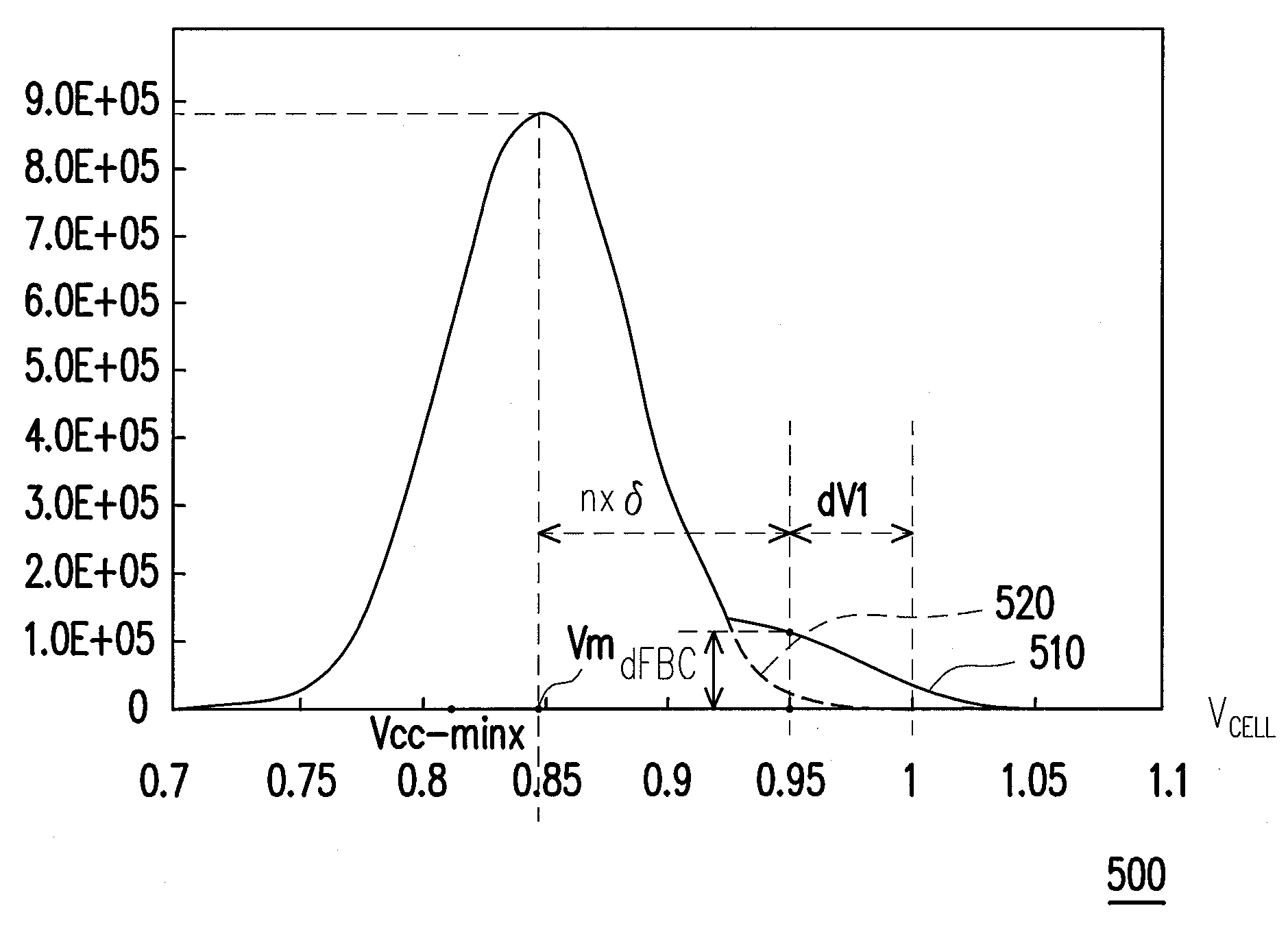

[0034]In the first embodiment, steps of tuning an operating voltage of the SRAM 100 include the following. First, perform a shmoo test (step S320) on the plurality of the SRAM 100 to be tested, wherein the shmoo test perf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More