Integrated Voltage Regulator with Embedded Passive Device(s)

a voltage regulator and passive device technology, applied in the field of integrated circuits, can solve the problems of voltage drop between the voltage regulator and the die that the voltage regulator, and the conventional voltage regulators have slow response times,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

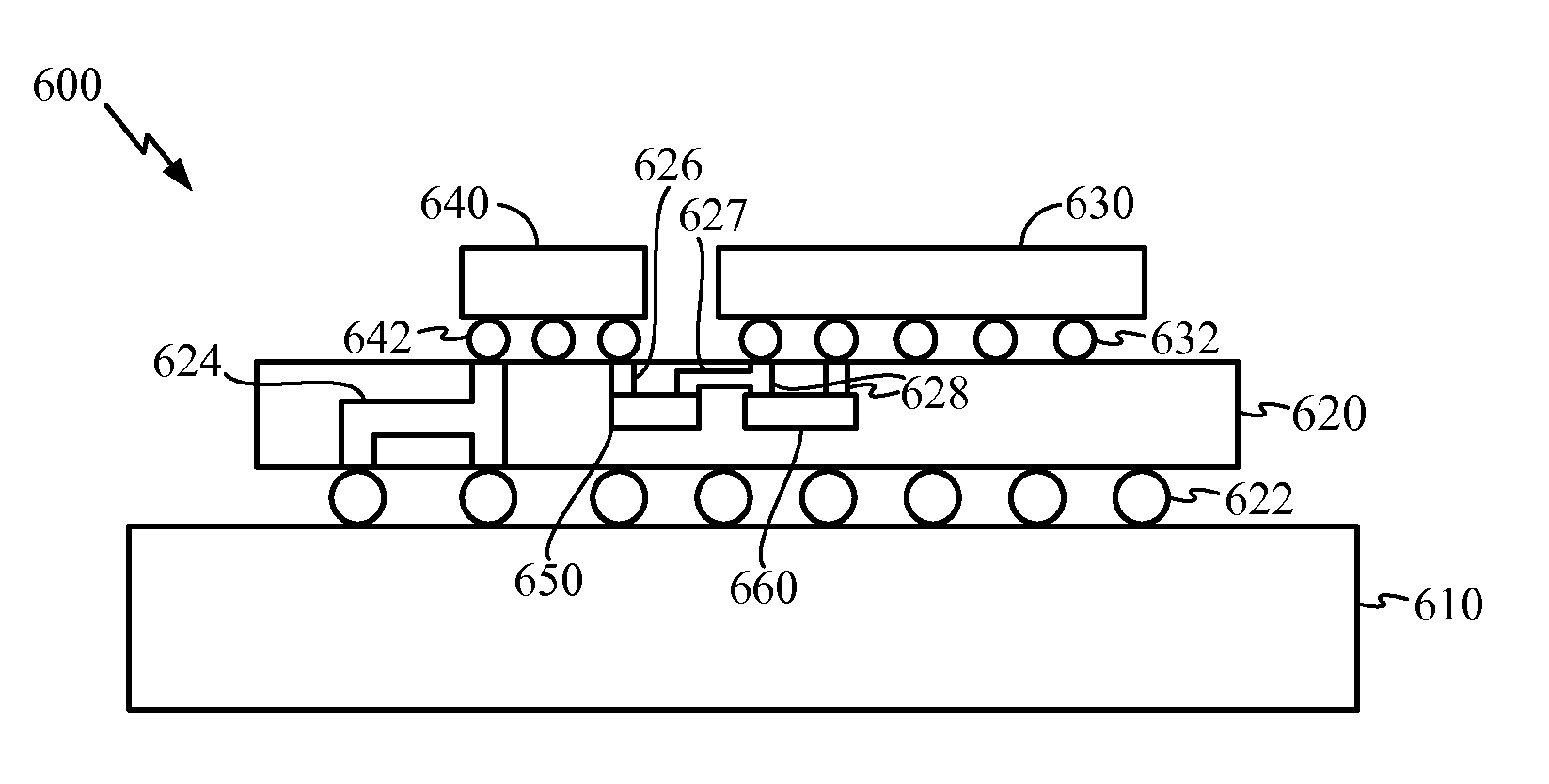

[0035]FIG. 4 is a cross-sectional view illustrating an exemplary voltage regulator on a die according to a An IC product 400 includes a packaging substrate 420 coupled to a PCB 410 through a packaging connection 422 such as bumps or pillars. The packaging substrate 420 includes embedded passive components that may store energy in magnetic or electric form. For example, an embedded inductor 450 and an embedded capacitor 460 are at least partially embedded in the packaging substrate 420. The embedded inductor 450 and / or the embedded capacitor 460 may use embedded die substrate (EDS) technology. In one embodiment, the embedded capacitor 460 may have capacitance values in the hundreds of nanoFarads and provide decoupling capacitance to a die 430. The die 430 is coupled to the packaging substrate 420 through an interconnect structure 432 such as bumps or pillars.

[0036]Manufacturing the embedded inductor 450 and the embedded capacitor 460 in the packaging substrate 420 may use a laminati...

second embodiment

[0039]In an alternative configuration, some of the embedded passive components may be replaced with vias in the packaging substrates. FIG. 5 is a cross-sectional view illustrating an exemplary voltage regulator on a die with an embedded parasitic inductance according to a

[0040]The packaging substrate 420 includes vias 526 having a parasitic inductance used by the active portion of the voltage regulator 440 as inductors for supplying voltage to the die 430. The vias 526 may be through vias, which extend the entire height of the packaging substrate 420. The through vias 526 may be coupled through the packaging connection 422 to through vias 516 in the PCB 410 if a larger inductance is desired than obtained with the through vias 526 alone. The use of parasitic inductance in through vias within the packaging substrate as a passive component simplifies semiconductor manufacturing by reducing a number of processes to embed inductors in the packaging substrate.

[0041]According to a third em...

fifth embodiment

[0046] inductance is provided by wirebonds. FIG. 7B is a cross-sectional view illustrating an exemplary voltage regulator with a wirebond inductance. A wirebond 750 couples the active portion of the voltage regulator 640 to one of the vias 716. The wirebond 750, the vias 716 and the conducting layer 730 provide inductance to the active portion of the voltage regulator 640.

[0047]Embedded passives in which through vias provide inductance for a voltage regulator will now be described in further detail. FIGS. 8A-C are block diagrams illustrating paths through a packaging substrate and PCB that may provide inductance. FIG. 8A is a block diagram illustrating a path 800 through a packaging substrate and PCB according to one embodiment. A top conductive layer 802 and a bottom conductive layer 810 of a packaging substrate are shown. Inner layers 804, 806 of the packaging substrate are also shown. A through via 805, couples the top conductive layer 802 and the bottom conductive layer 810. A p...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| wall voltage | aaaaa | aaaaa |

| wall voltage | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More