Soft pin insertion during physical design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

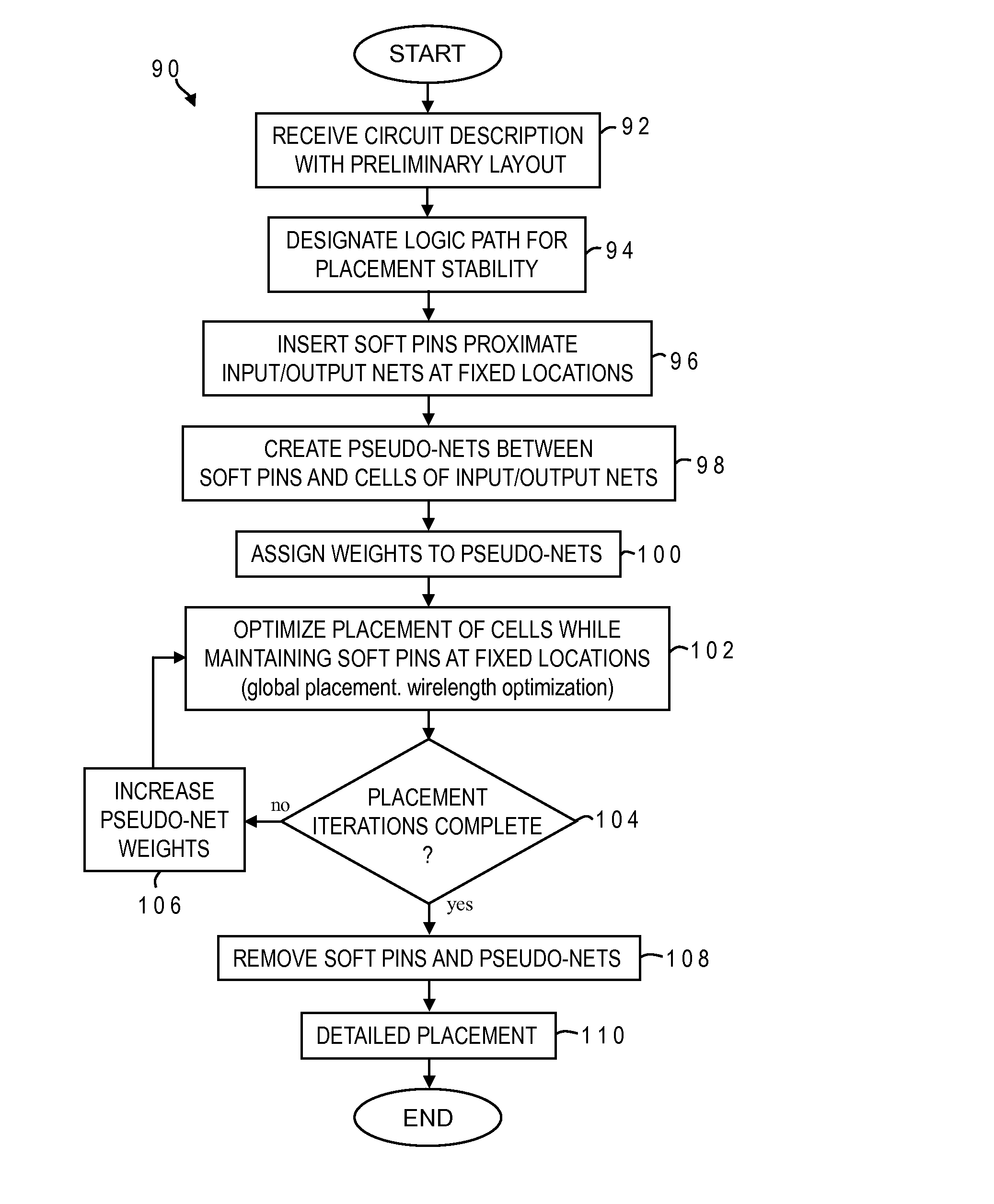

Method used

Image

Examples

Embodiment Construction

)

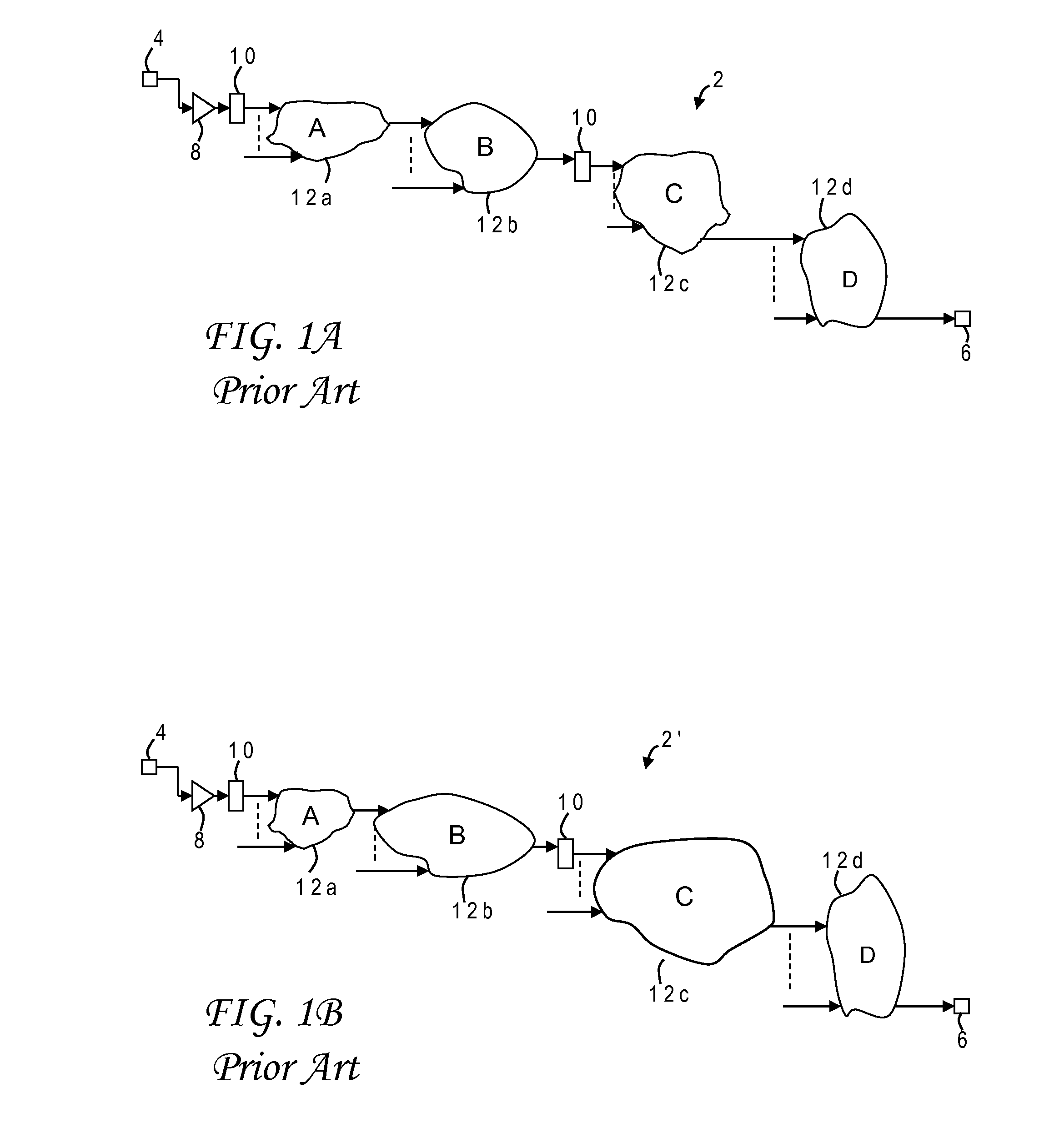

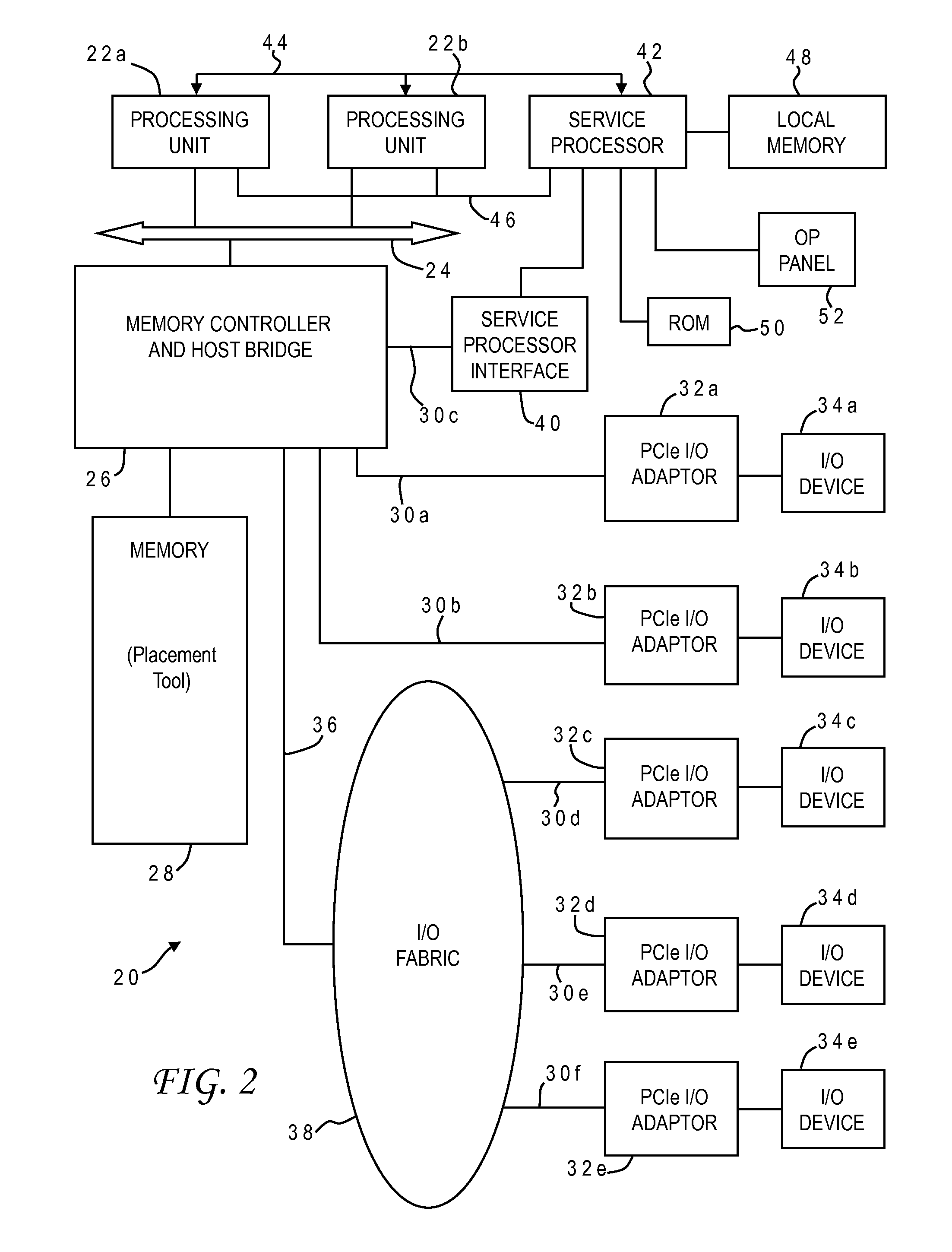

[0020]Current microprocessor trends are integrating traditionally custom designs with random logic macros (RLMs) into very large integrated circuit designs. In some cases, entire microprocessor units are designed using an automated synthesis flow that integrates these traditional custom designs and RLMs. This type of merged synthesis run is referred to as large block synthesis (LBS). The LBS blocks, i.e., sets of cells or logic modules, require handling dataflow designs differently than traditional RLMs. In particular, as the size of the designs grow, it takes significant effort to make synthesis generate architecturally correct placement solutions due to placement instability as problems with timing and congestion are incrementally solved. Slight changes to the assertions in the circuit design can drastically modify the placement solution, creating new timing problems that where not there before. Balanced timing is often not achieved until the product development phase becomes sta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More