Wiring board

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

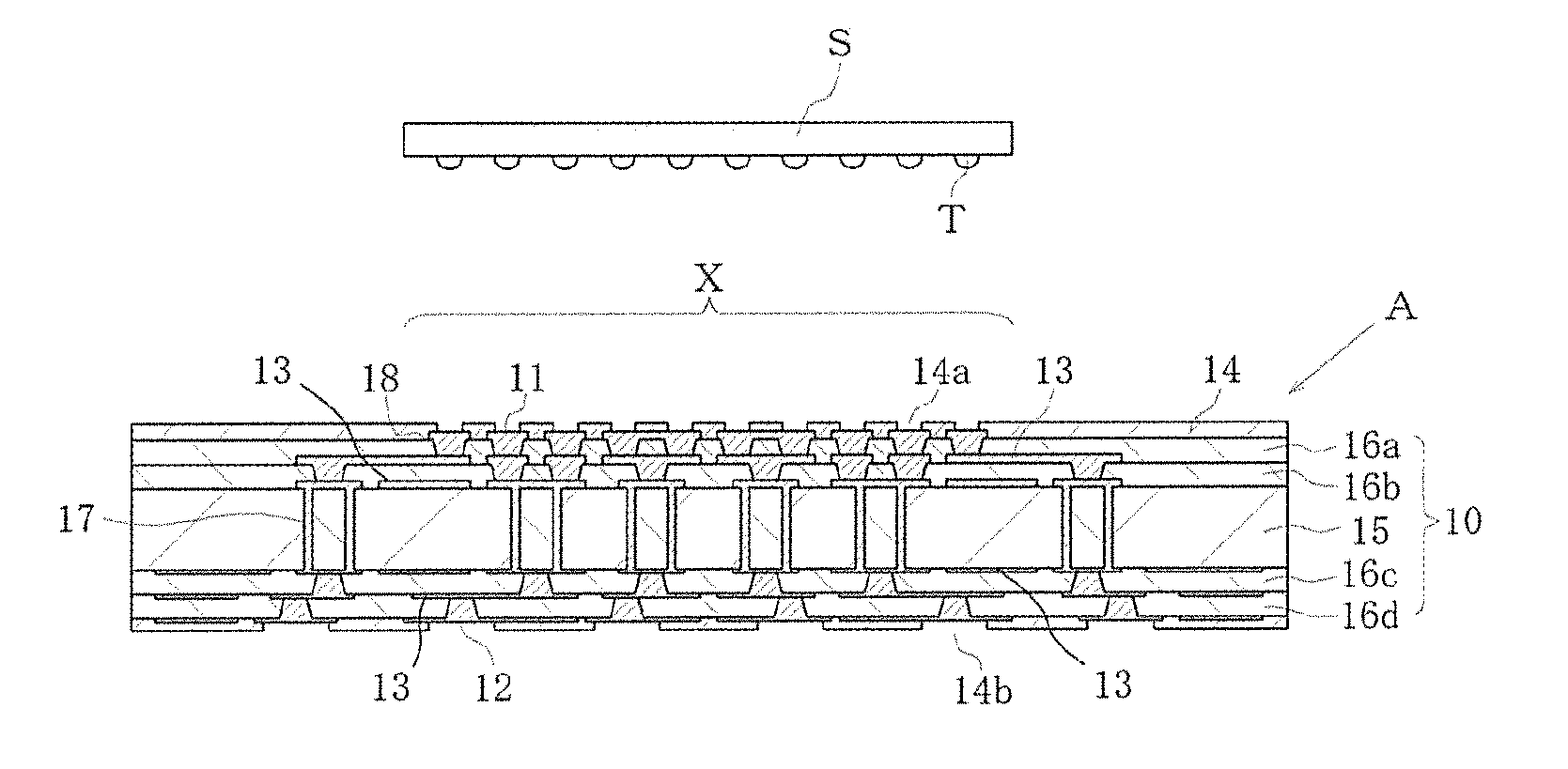

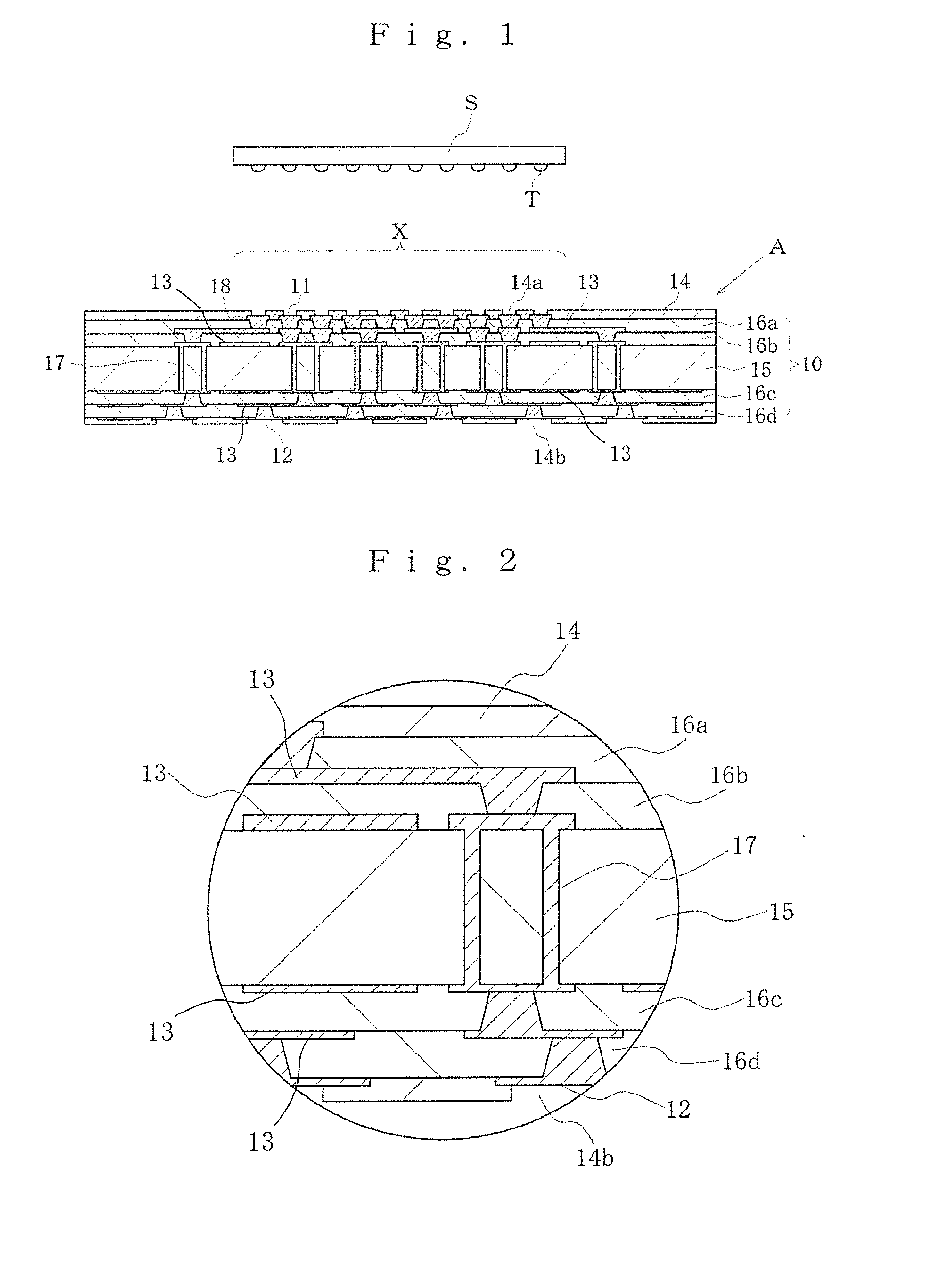

[0019]A wiring board according to the one embodiment is described with reference to FIG. 1. The wiring board A shown in FIG. 1 includes an insulating substrate 10, a conductor layer 13, and a solder resist layer 14.

[0020]The insulating substrate 10 is obtained by laminating insulating layers 16a and 16b on an upper surface of a core substrate 15, and insulating layers 16c and 16d on a lower surface of the core substrate 15. The insulating substrate 10 has a mounting portion X for mounting a semiconductor element S at a central portion on an upper surface thereof. The core substrate 15 is formed of an electrical insulating material obtained by, for example, impregnating a glass cloth with epoxy resin, bismaleimide triazine resin, or the like, followed by curing.

[0021]The core substrate 15 has a plurality of through holes 17. The conductor layer 13 is deposited on upper and lower surfaces of the core substrate 15 and in the through holes 17. The through holes 17 are formed by, for exa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More