Advanced Control Circuit for Switched-Mode DC-DC Converter

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023]The preferred embodiments of the present invention provide significant advantages over DC-DC voltage converters of the prior art as will become evident from the following detailed description.

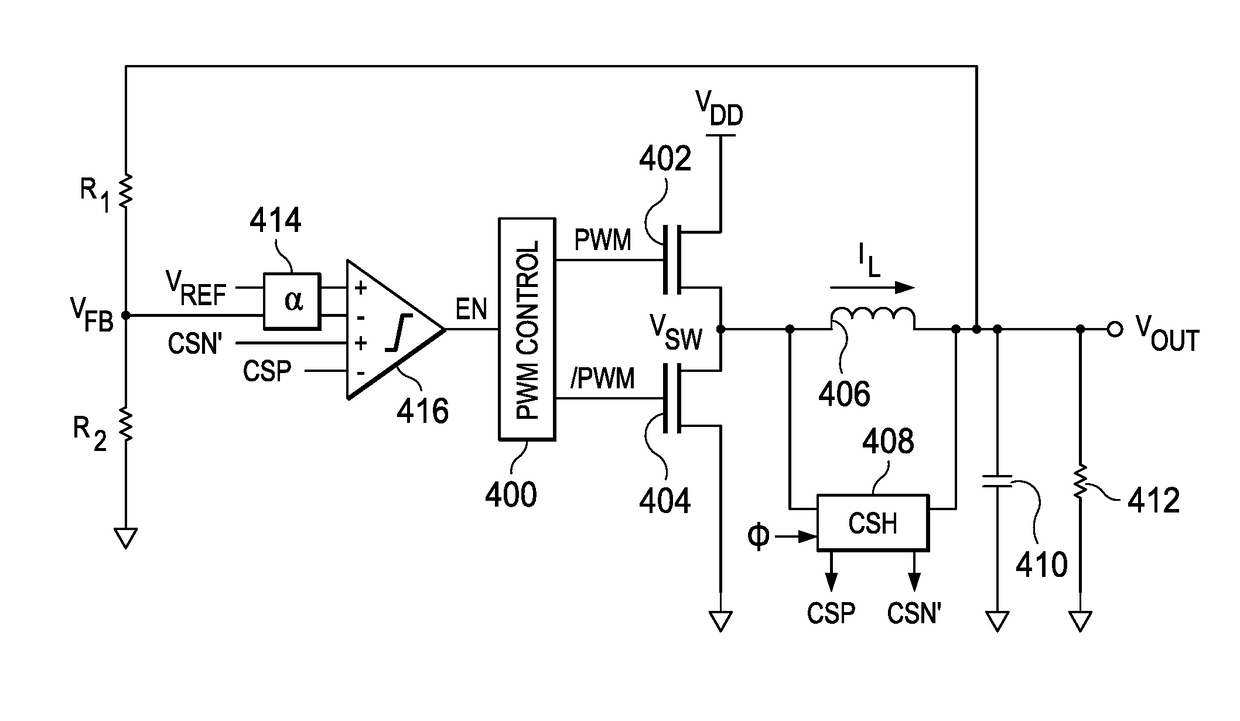

[0024]Referring to FIG. 4, there is a DC-DC voltage regulator circuit of the present invention. Here and in the following discussion, the same reference numerals are used in various drawing figures to indicate the same circuit elements. The voltage regulator includes a pulse width modulation (PWM) control circuit 400 that produces control signal PWM and complementary control signal / PWM. In some embodiments of the present invention, complementary control signal / PWM may be omitted. N-channel transistor 402 has a current path coupled between supply voltage VDD and voltage terminal VSW controlled by PWM. N-channel transistor 404 has a current path coupled between voltage terminal VSW and reference supply voltage terminal VSS. The current path of n-channel transistor 404 is controlled by / PW...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More