Patents

Literature

70results about How to "Power dissipation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Power system

ActiveUS20100084918A1Reduce power consumptionImprove the level ofCircuit authenticationNear-field transmissionEngineeringElectrical and Electronics engineering

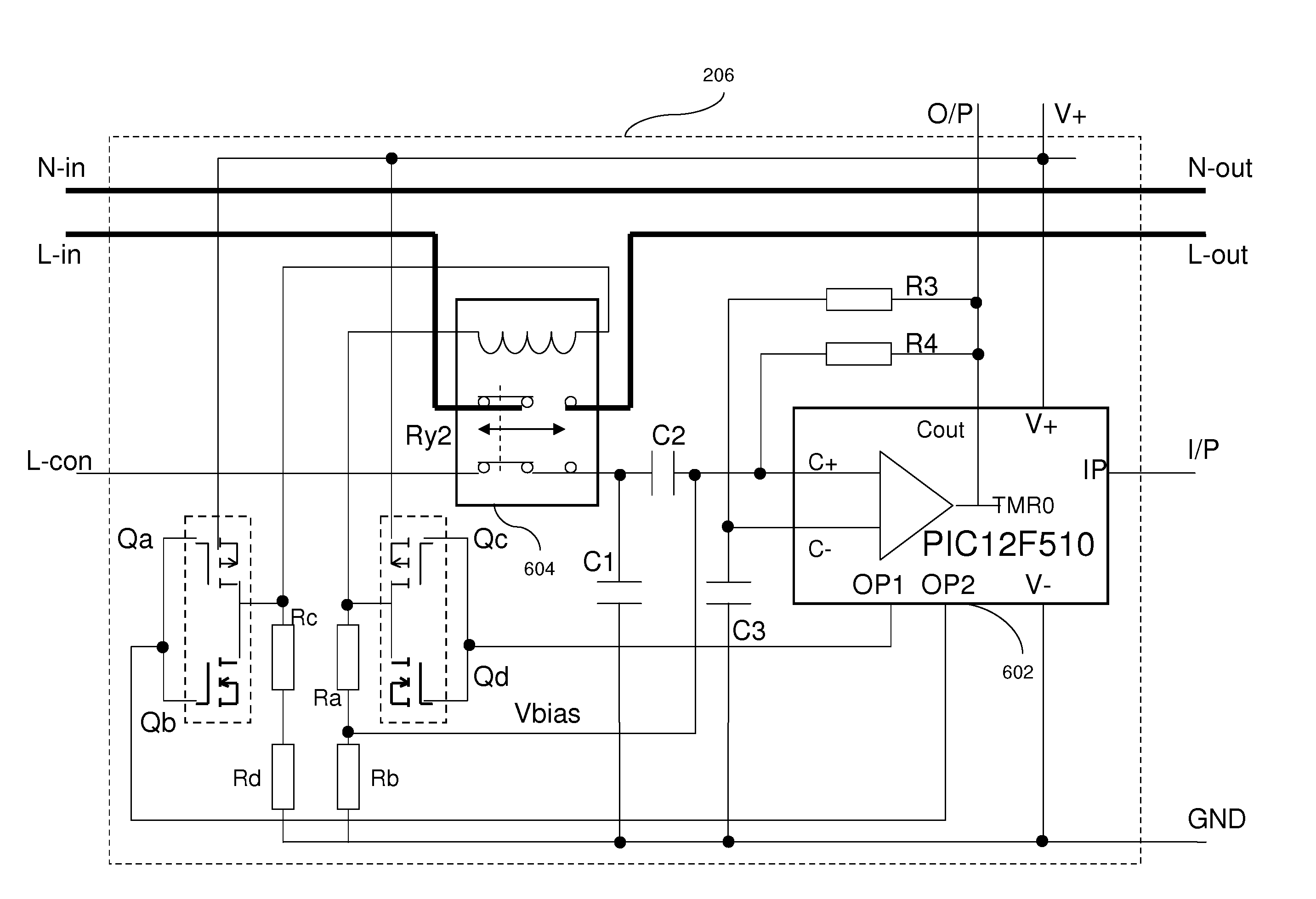

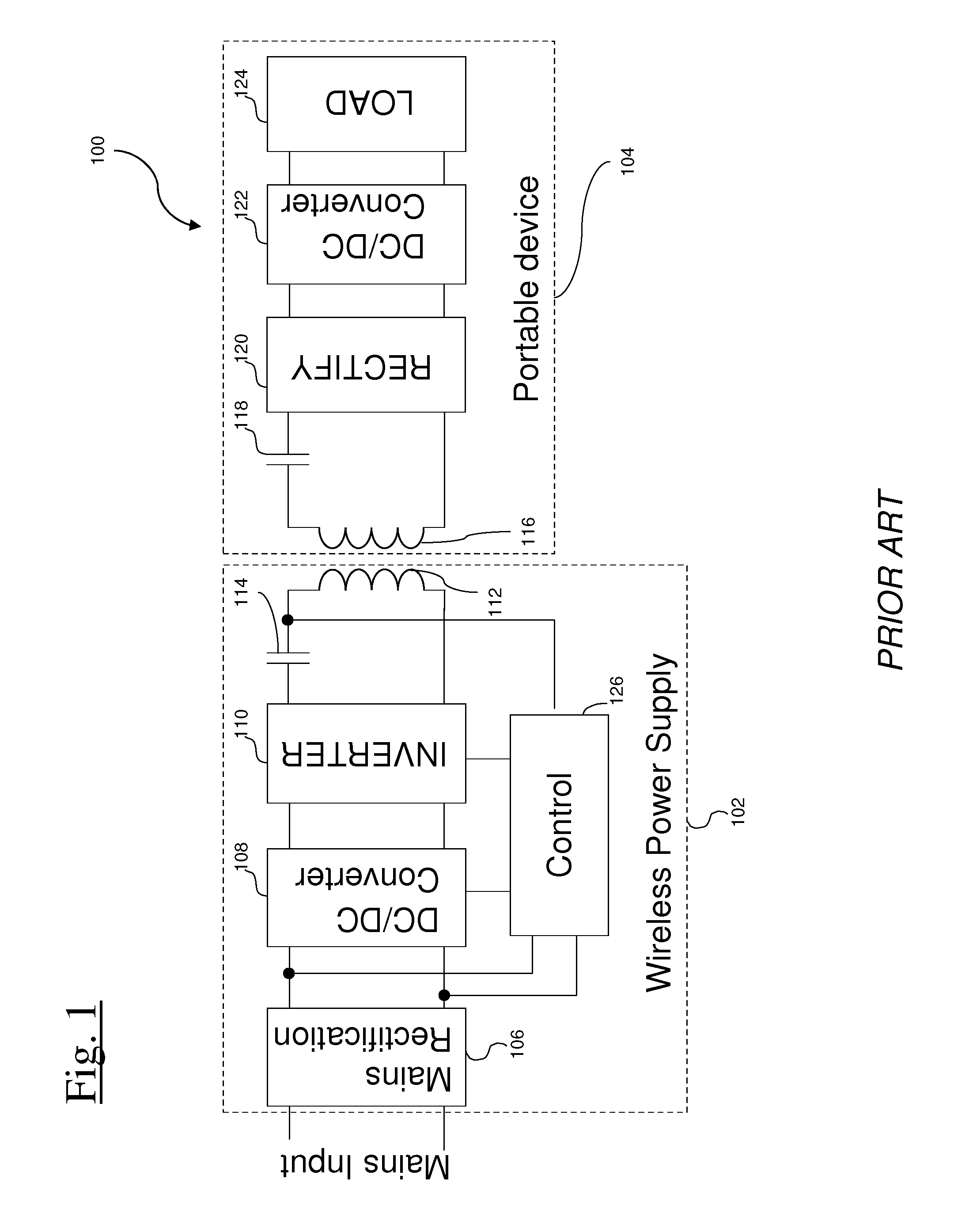

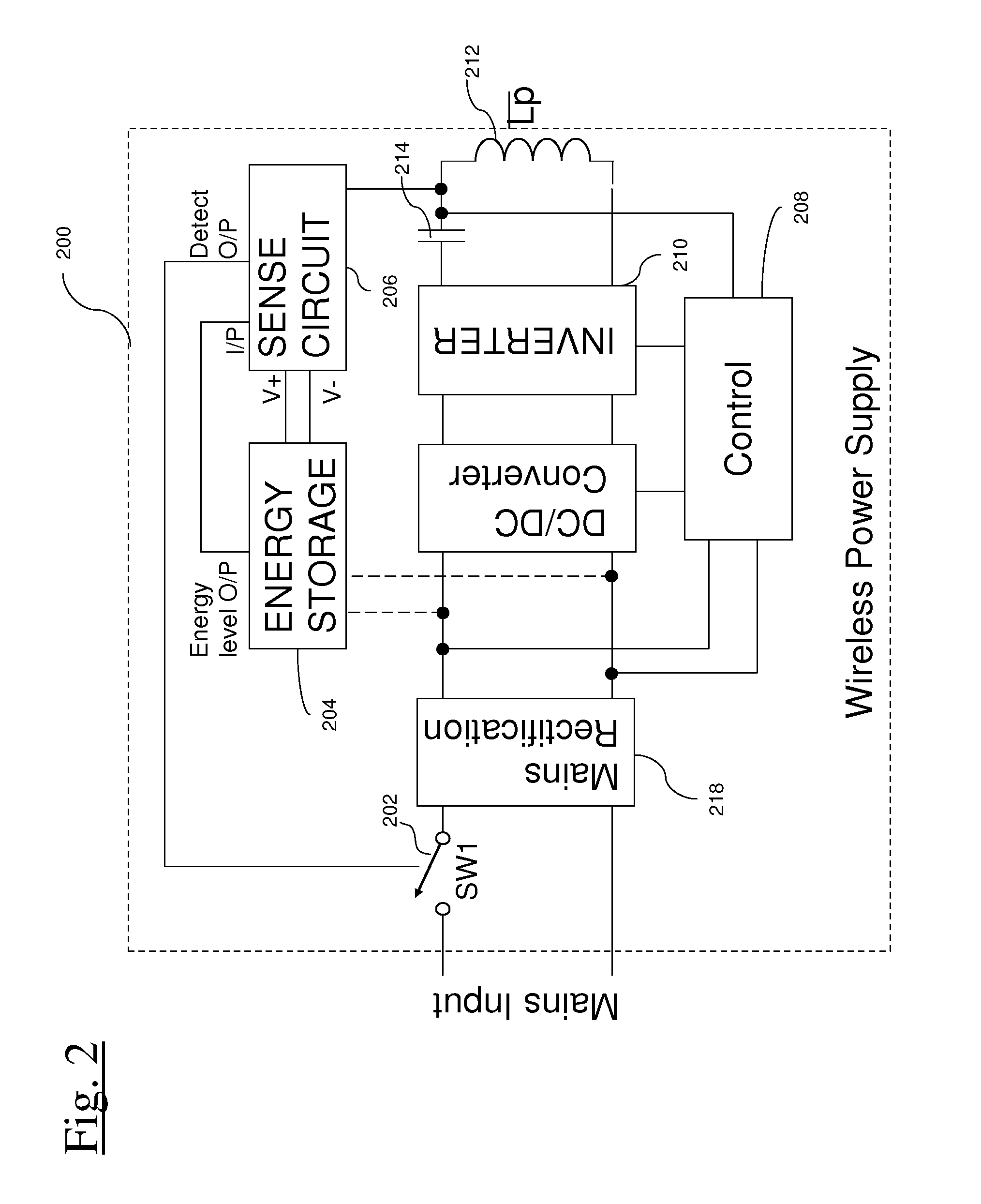

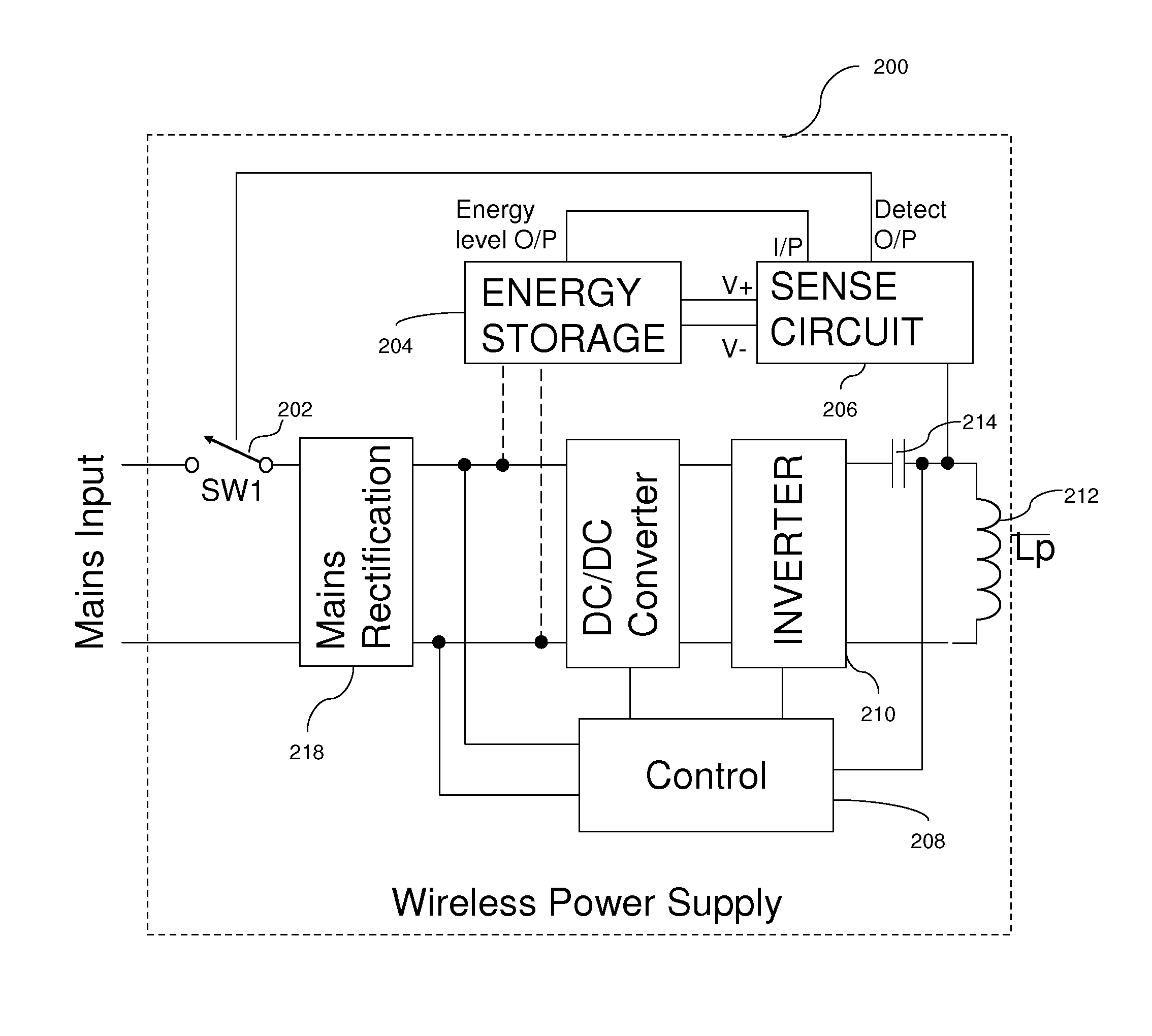

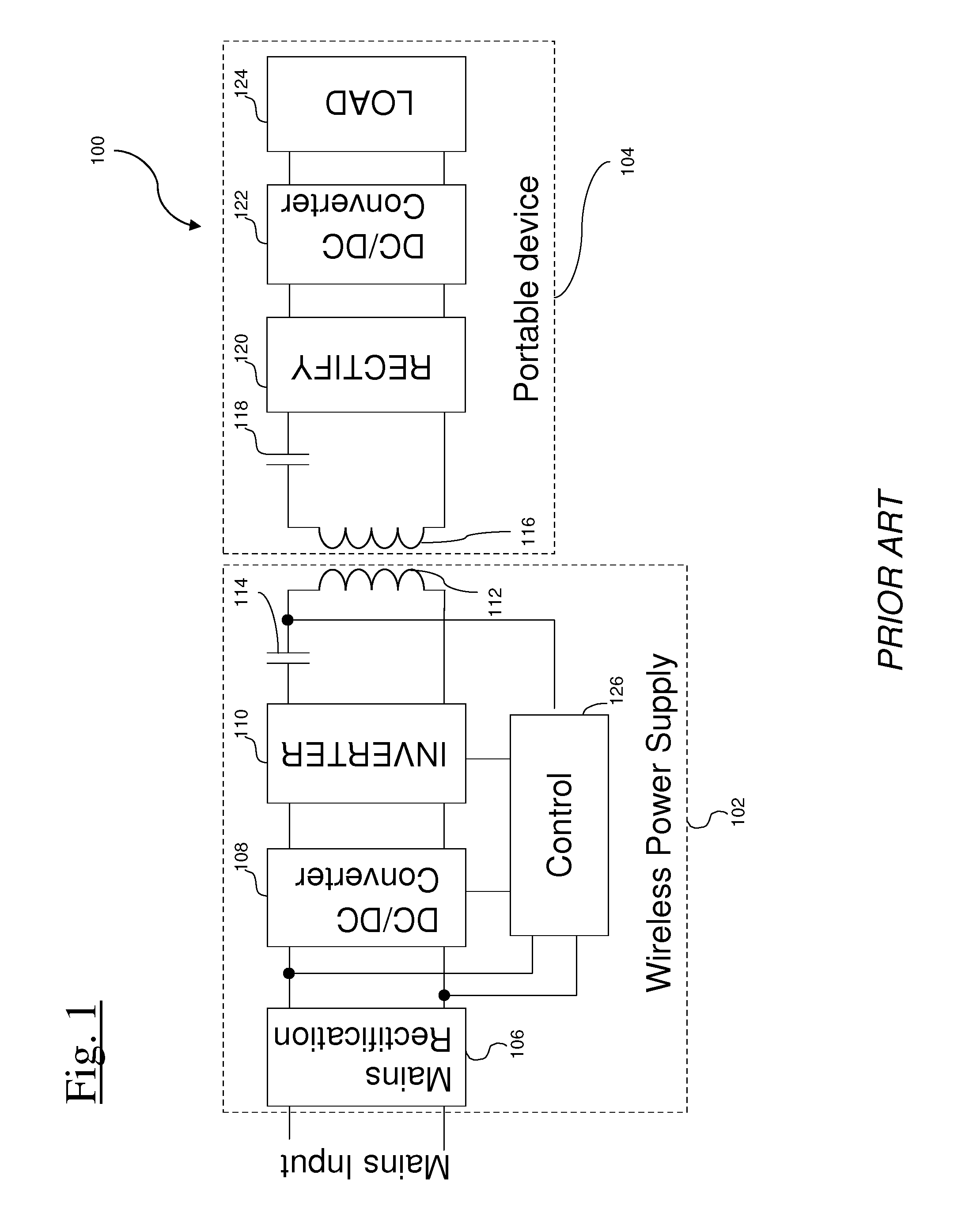

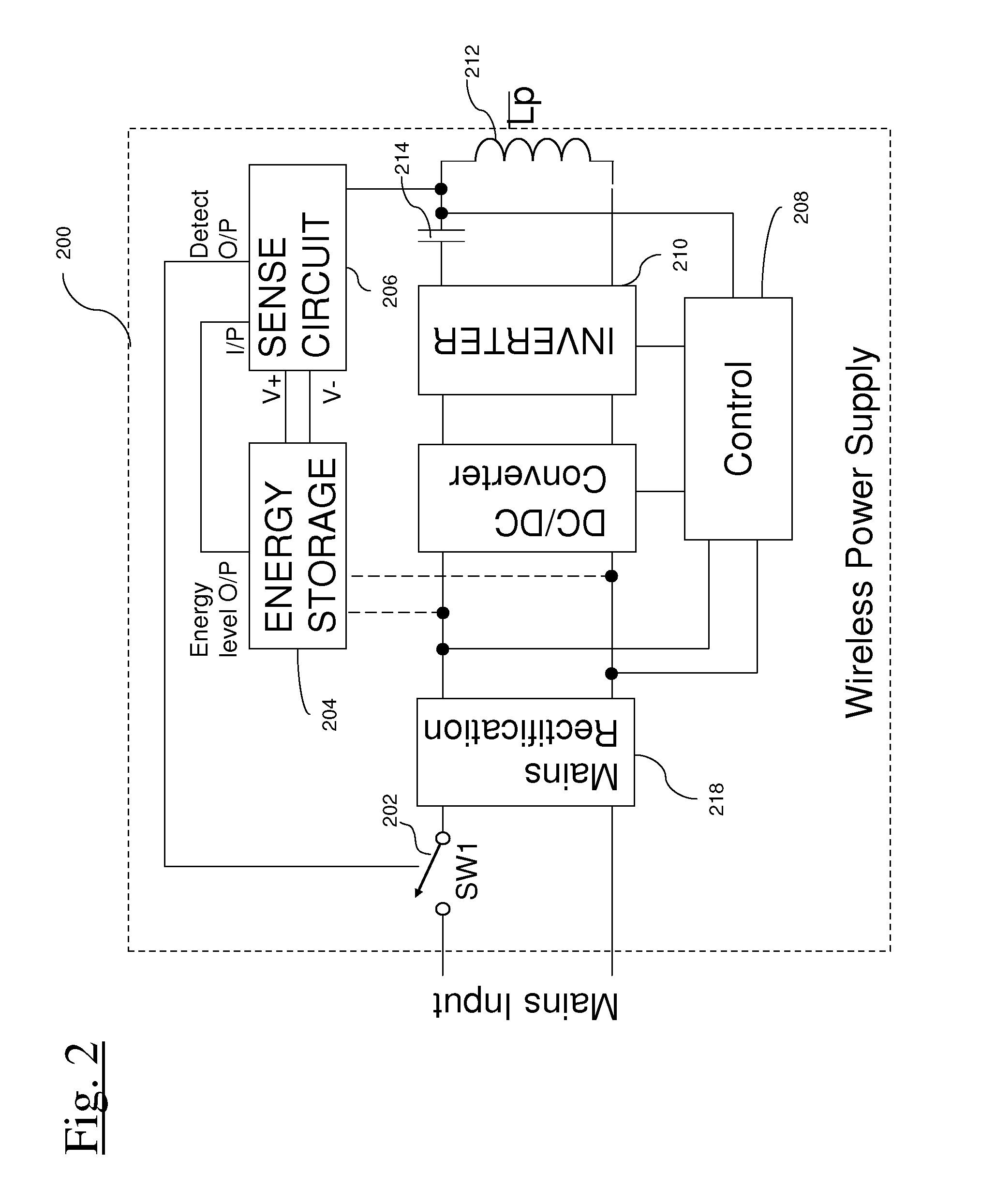

The present invention provides methods and apparatus for reducing power consumption. One method includes detecting the presence of an object, identifying whether the object is a valid device and restricting power if its not a valid device. Another method includes temporarily applying a low amount of power to the primary unit to detect a load, supplying more power to determine if its a valid secondary device, and restricting power if its not. An apparatus for reducing power consumption includes two power inputs, where the lower power input powers a sense circuit. A switch selectively decouples the higher power input from the primary subcircuit during detection mode and couples the higher power input to the primary subcircuit during power supply mode.

Owner:PHILIPS IP VENTURES BV

Power system

ActiveUS8446046B2Reduce power consumptionReduce the required powerCircuit authenticationDc network circuit arrangementsEngineeringHigher Power

The present invention provides methods and apparatus for reducing power consumption. One method includes detecting the presence of an object, identifying whether the object is a valid device and restricting power if its not a valid device. Another method includes temporarily applying a low amount of power to the primary unit to detect a load, supplying more power to determine if its a valid secondary device, and restricting power if its not. An apparatus for reducing power consumption includes two power inputs, where the lower power input powers a sense circuit. A switch selectively decouples the higher power input from the primary subcircuit during detection mode and couples the higher power input to the primary subcircuit during power supply mode.

Owner:PHILIPS IP VENTURES BV

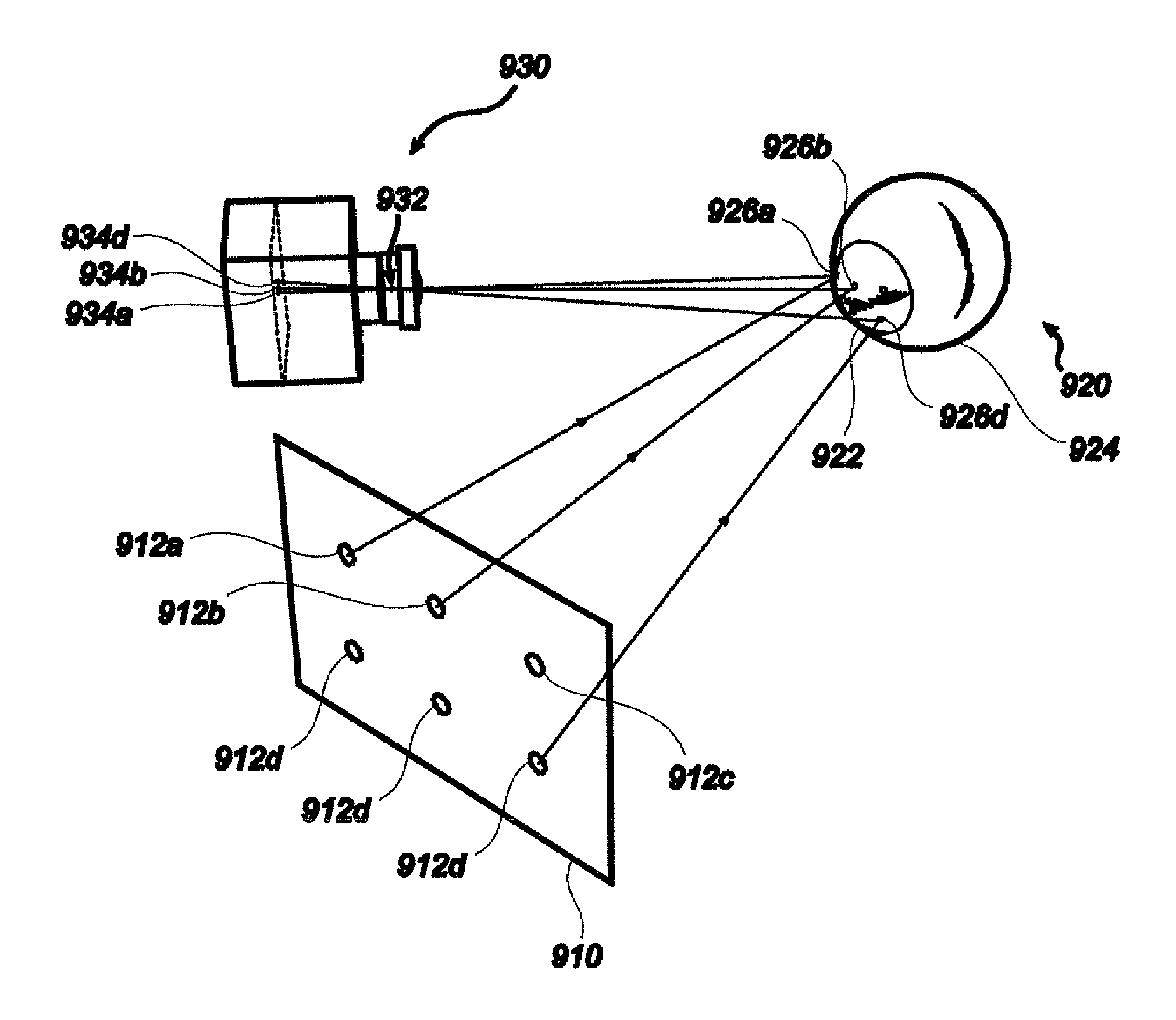

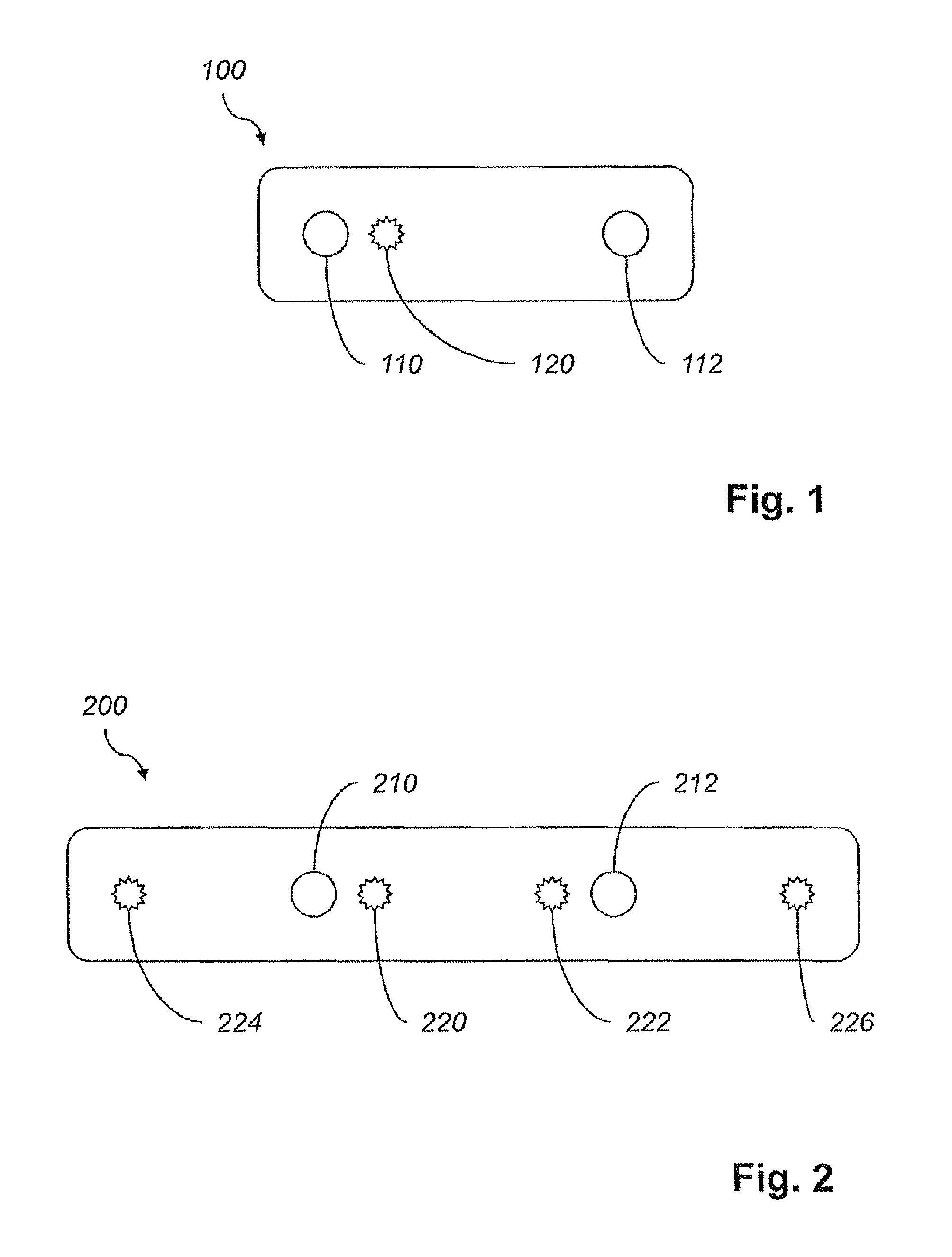

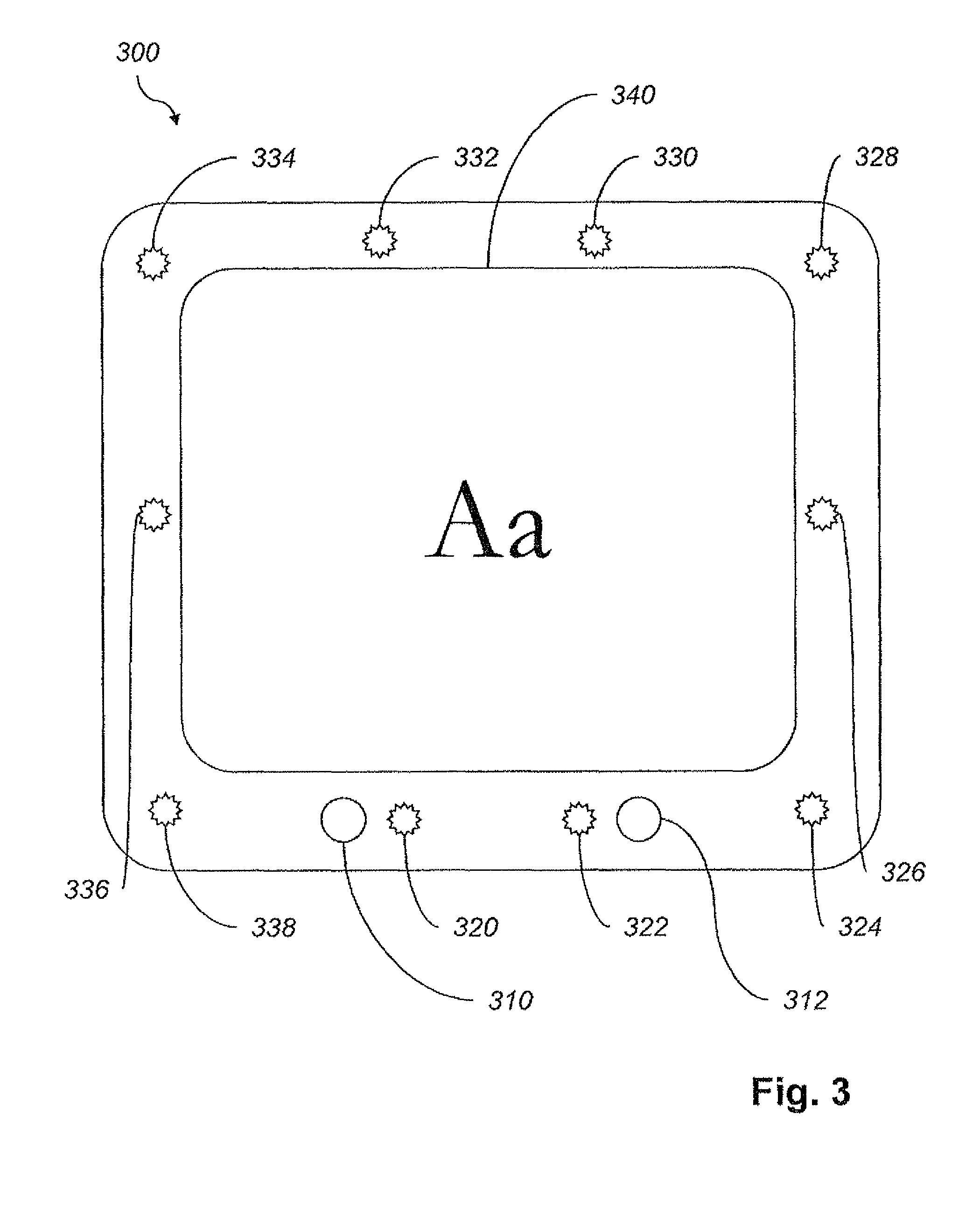

Adaptive camera and illuminator eyetracker

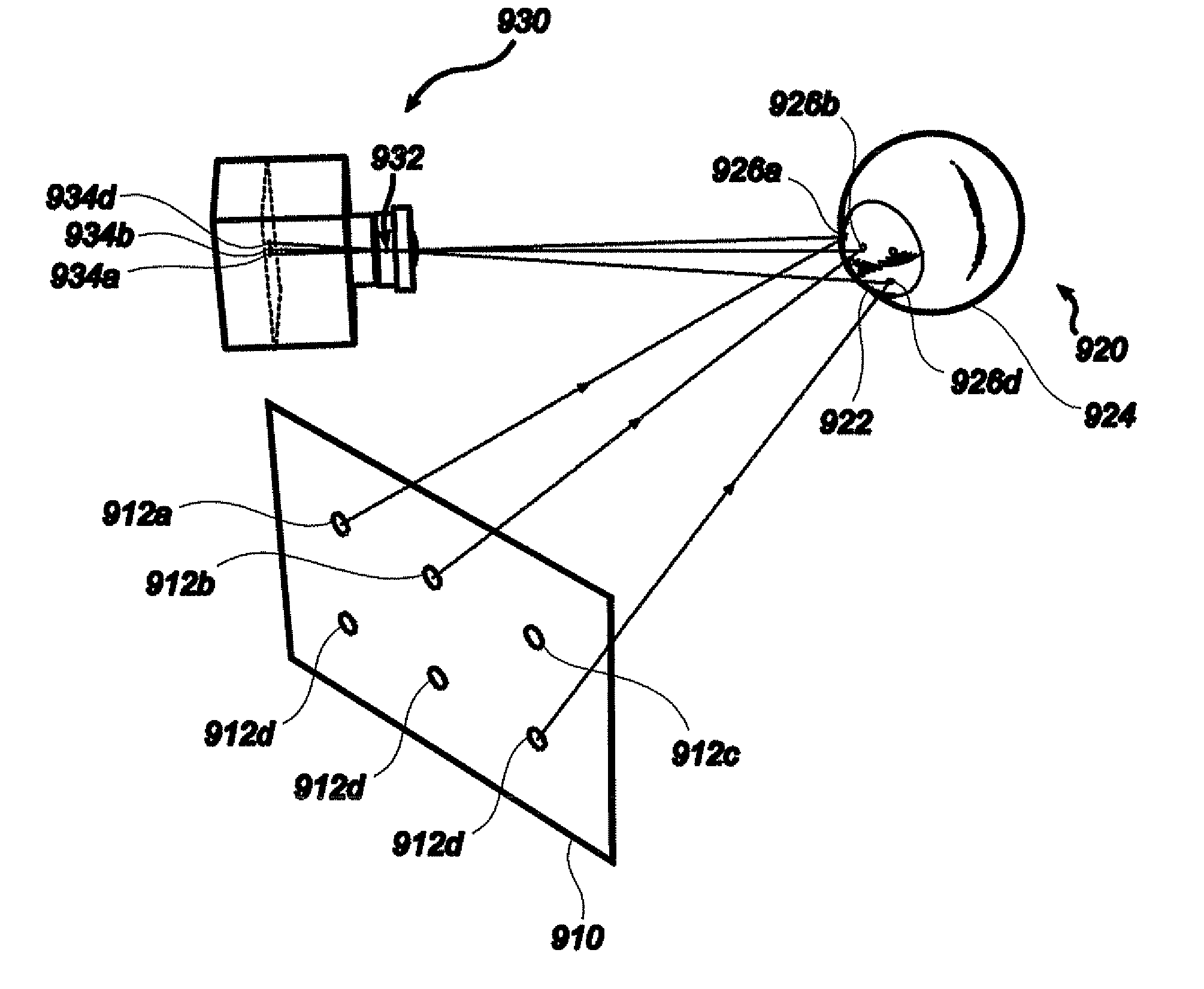

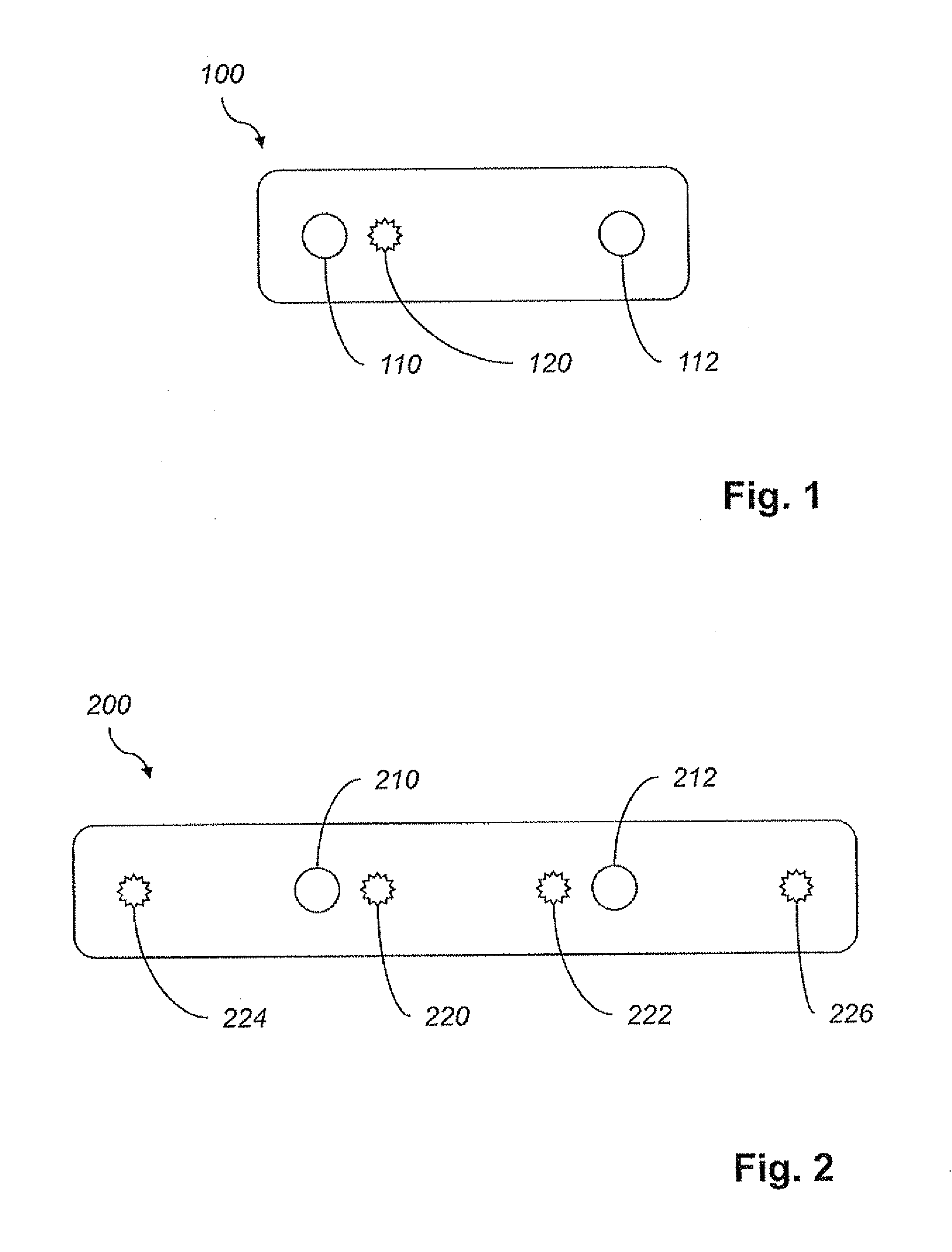

ActiveUS20100328444A1Minimize timeIncrease probabilityPrintersProjectorsImaging qualityActive camera

An eye tracker includes at least one illuminator for illuminating an eye, at least two cameras for imaging the eye, and a controller. The configuration of the reference illuminator(s) and cameras is such that, at least one camera is coaxial with a reference illuminator and at least one camera is non-coaxial with a reference illuminator. The controller is adapted to select one of the cameras to be active to maximize an image quality metric and avoid obscuring objects. The eye tracker is operable in a dual-camera mode to improve accuracy. A method and computer-program product for selecting a combination of an active reference illuminator from a number of reference illuminators, and an active camera from a plurality of cameras are provided.

Owner:TOBII TECH AB

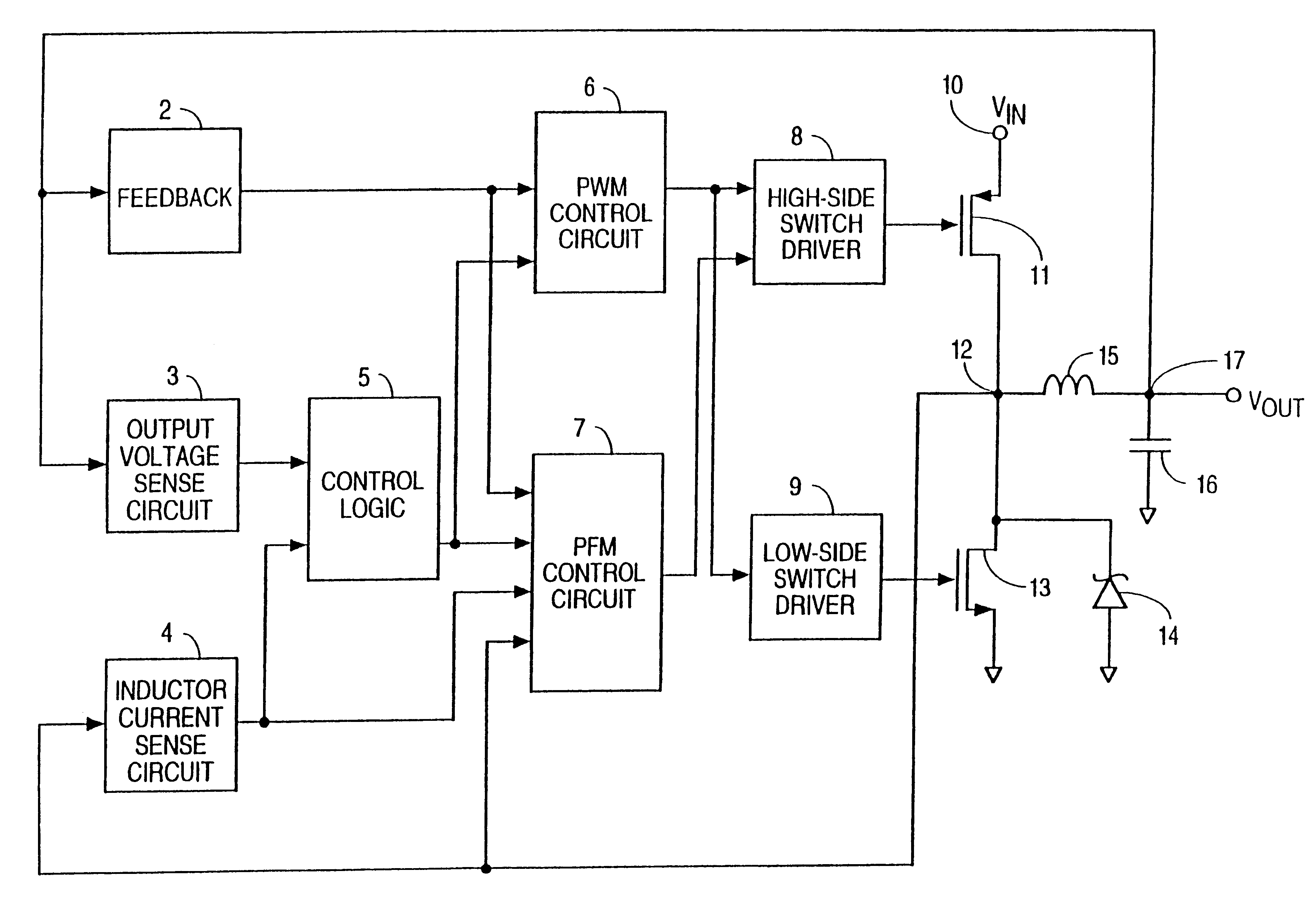

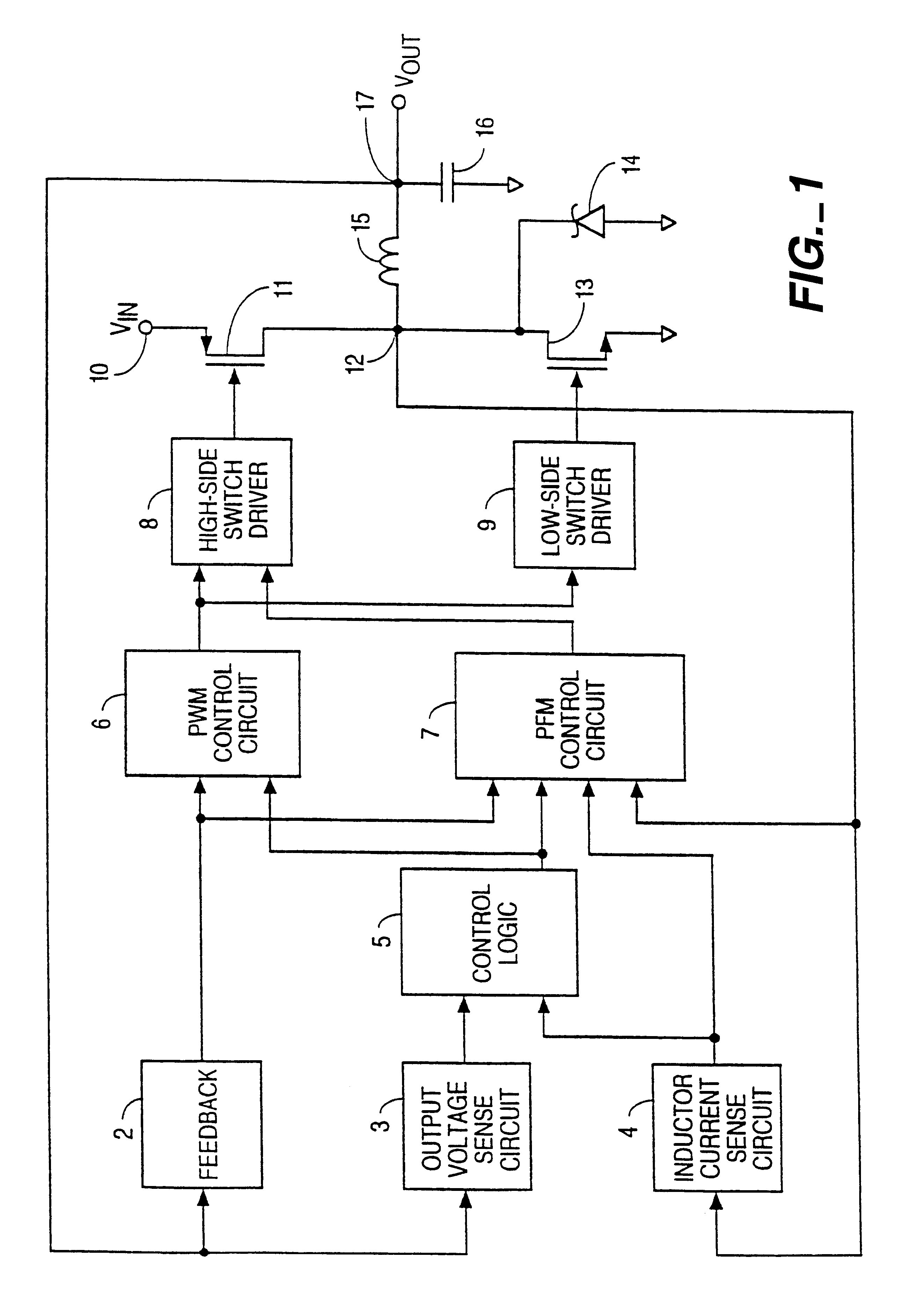

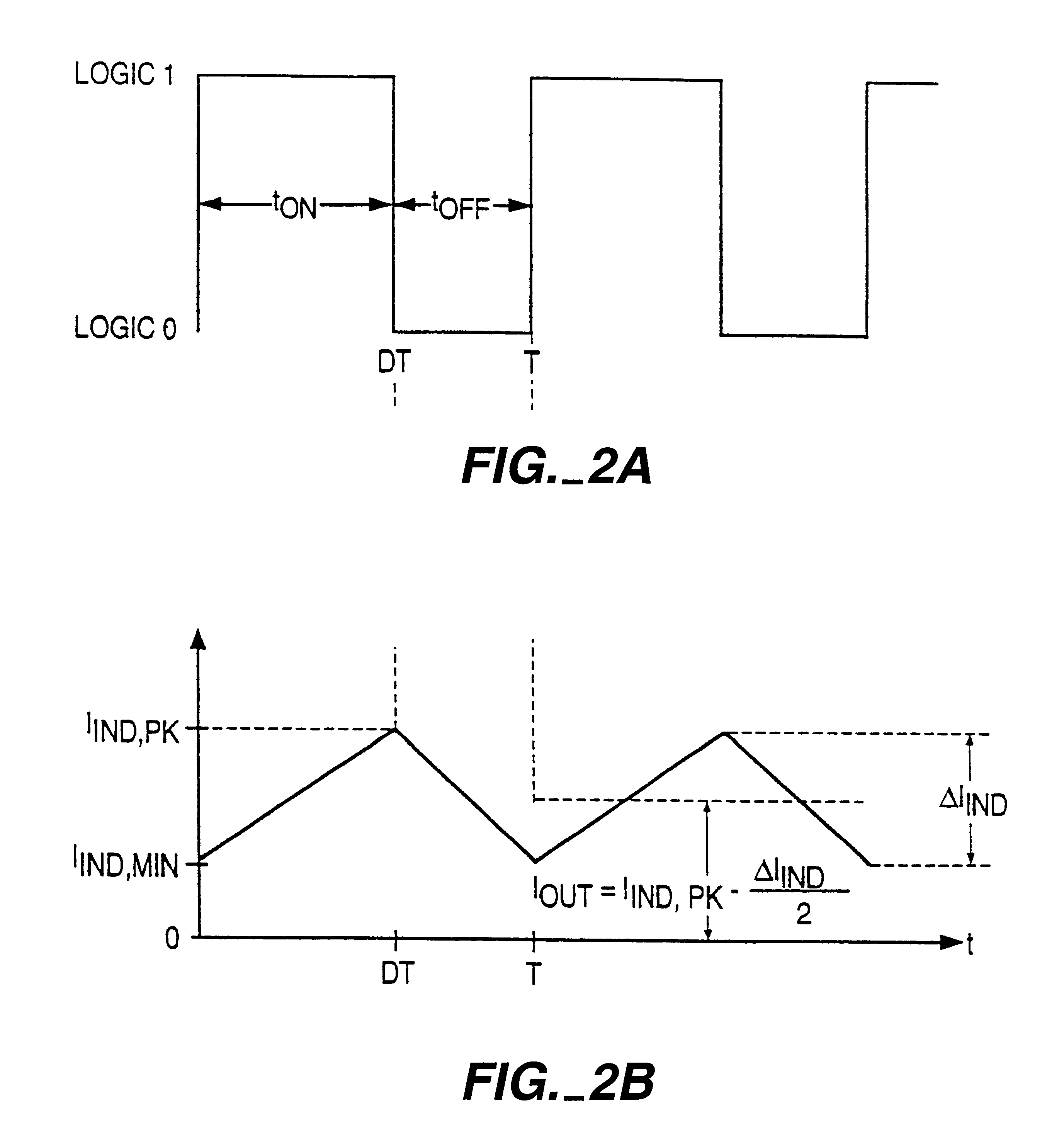

Voltage regulator that operates in either PWM or PFM mode

InactiveUSRE37609E1Improve efficiencyPower dissipationEfficient power electronics conversionApparatus without intermediate ac conversionVoltage regulationEngineering

A switching voltage regulator achieves high efficiency by automatically switching between a pulse frequency modulation (PFM) mode and a pulse-width modulation (PWM) mode. Switching between the modes of voltage regulation is accomplished by monitoring the output voltage and the output current, wherein the regulator operates in PFM mode at small output currents and in PWM mode at moderate to large output currents. PFM mode maintains a constant output voltage by forcing the switching device to skip cycles when the output voltage exceeds its nominal value. In PWM mode, a PWM signal having a variable duty cycle controls the switching device. A constant output voltage is maintained by feedback circuitry which alters the duty cycle of the PWM signal according to fluctuations in the output voltage.

Owner:MICREL

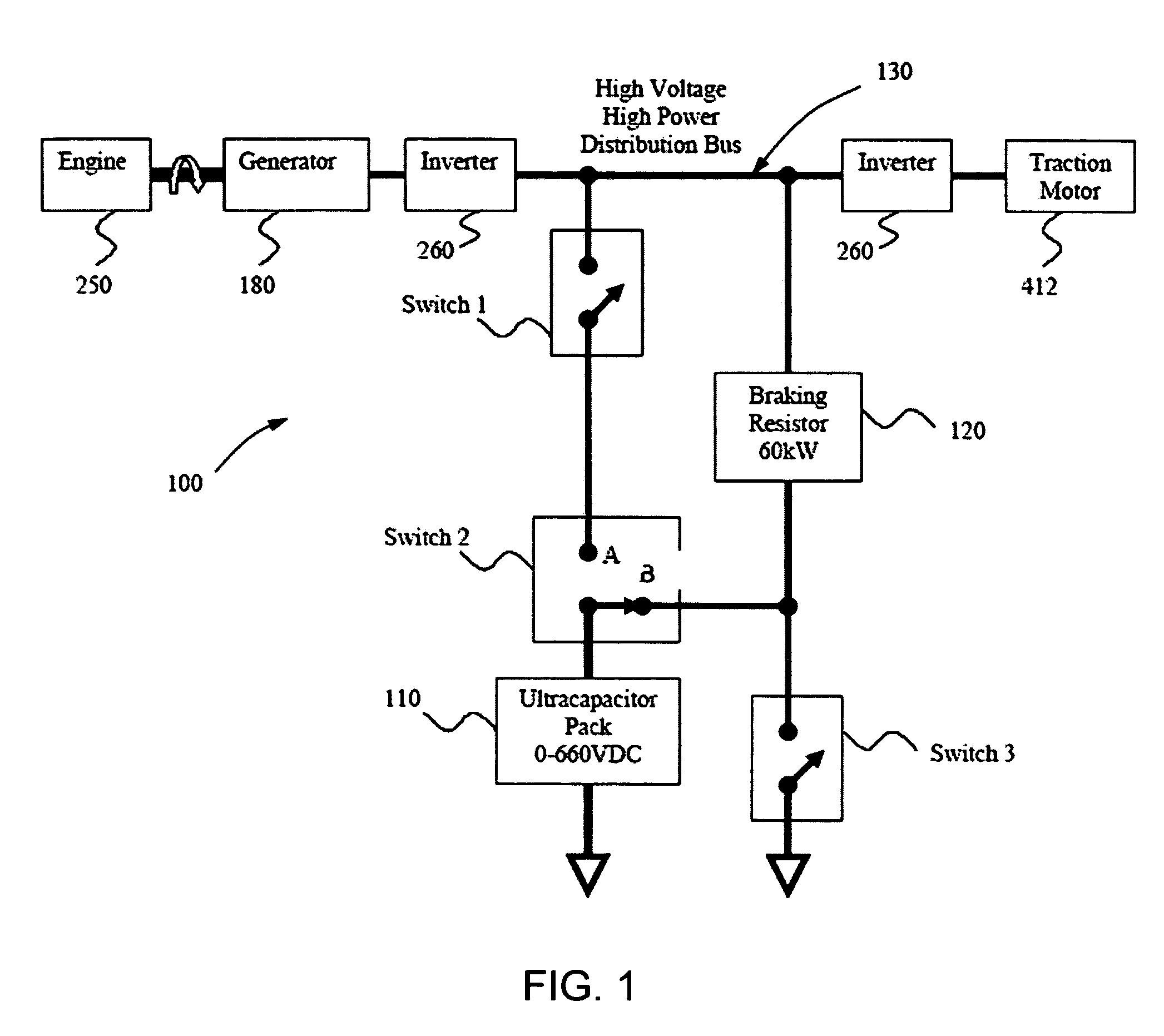

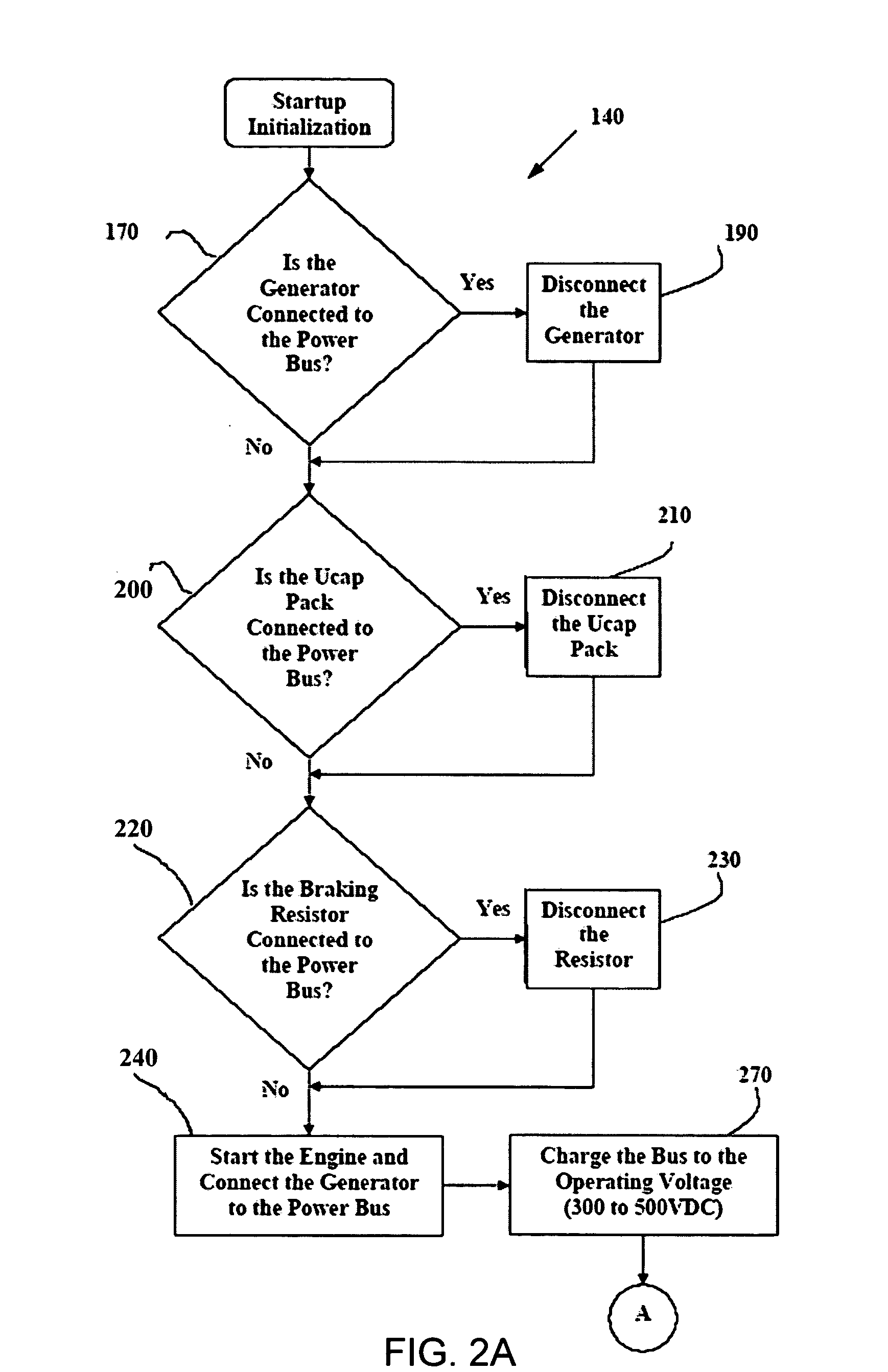

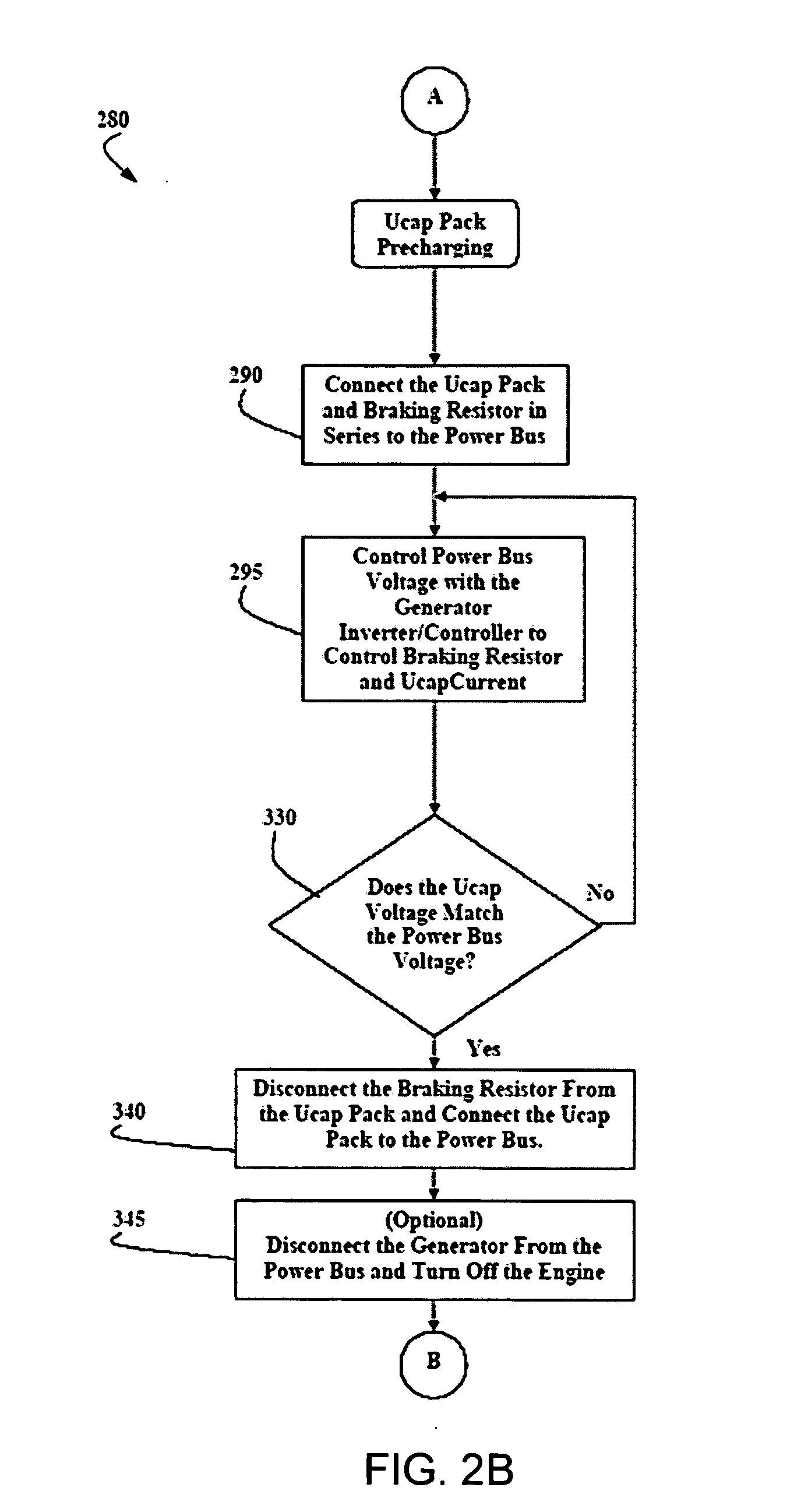

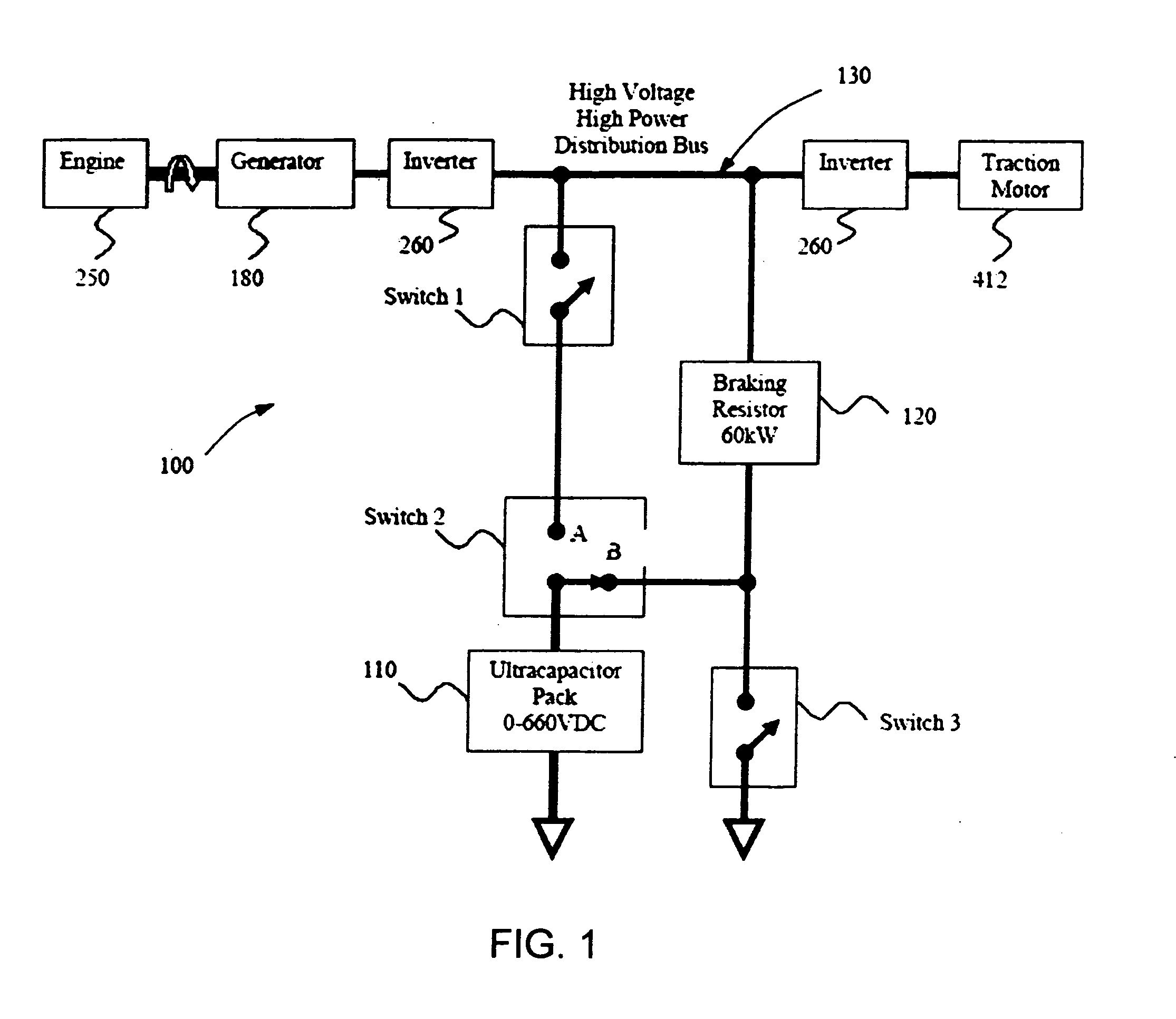

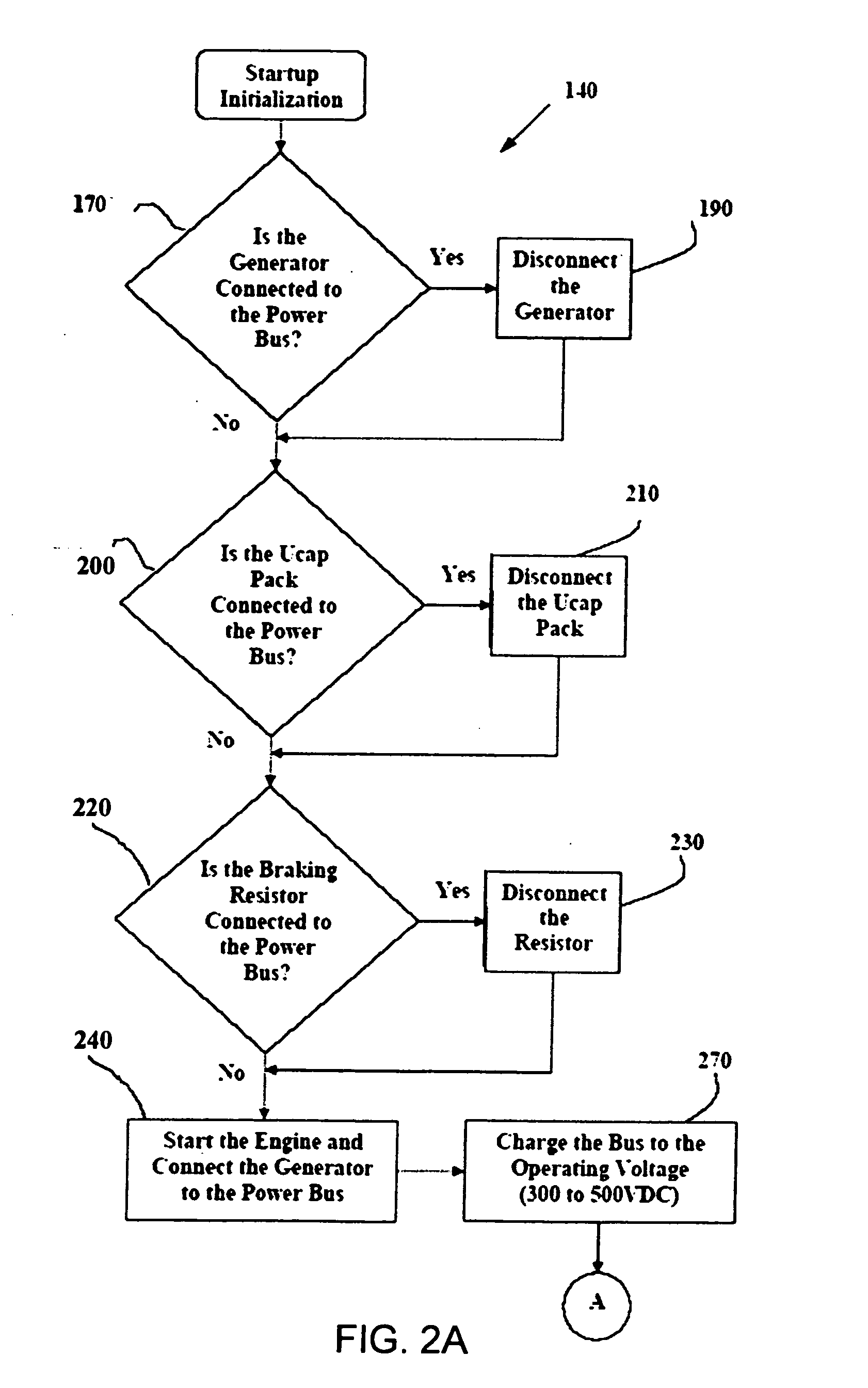

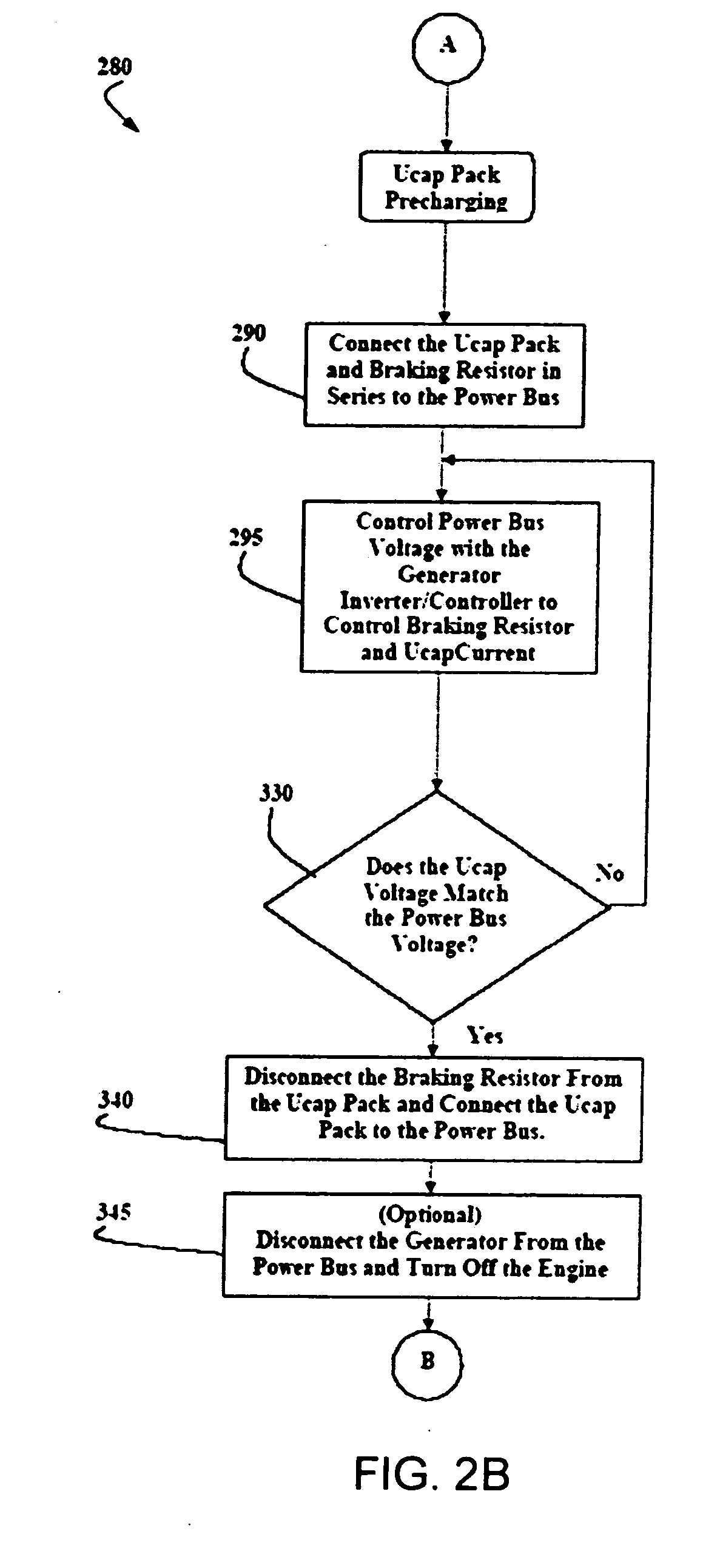

System and method for precharging and discharging a high power ultracapacitor pack

InactiveUS20060103358A1Fast equalizationEasy dischargeBatteries circuit arrangementsDc motor stoppersSwitchgearResistor

This invention is a system and a method that uses the braking resistor, commonly used and available in electrically or hybrid-electrically propelled vehicles, to limit the precharge current during the startup of a high power ultracapacitor pack energy storage device and / or safely and rapidly discharge an ultracapacitor pack for maintenance work or storage to lengthen the life of the individual ultracapacitor cells and, correspondingly, the whole pack. The use of the braking resistor for precharging an ultracapacitor energy storage pack is an effective and less expensive method compared to other methods such as a separate DC-to-DC converter. This method includes the control logic sequence to activate and deactivate switching devices that perform the connections for the charging and discharging current paths.

Owner:SHEPPARD MULLIN RICHTER & HAMPTON

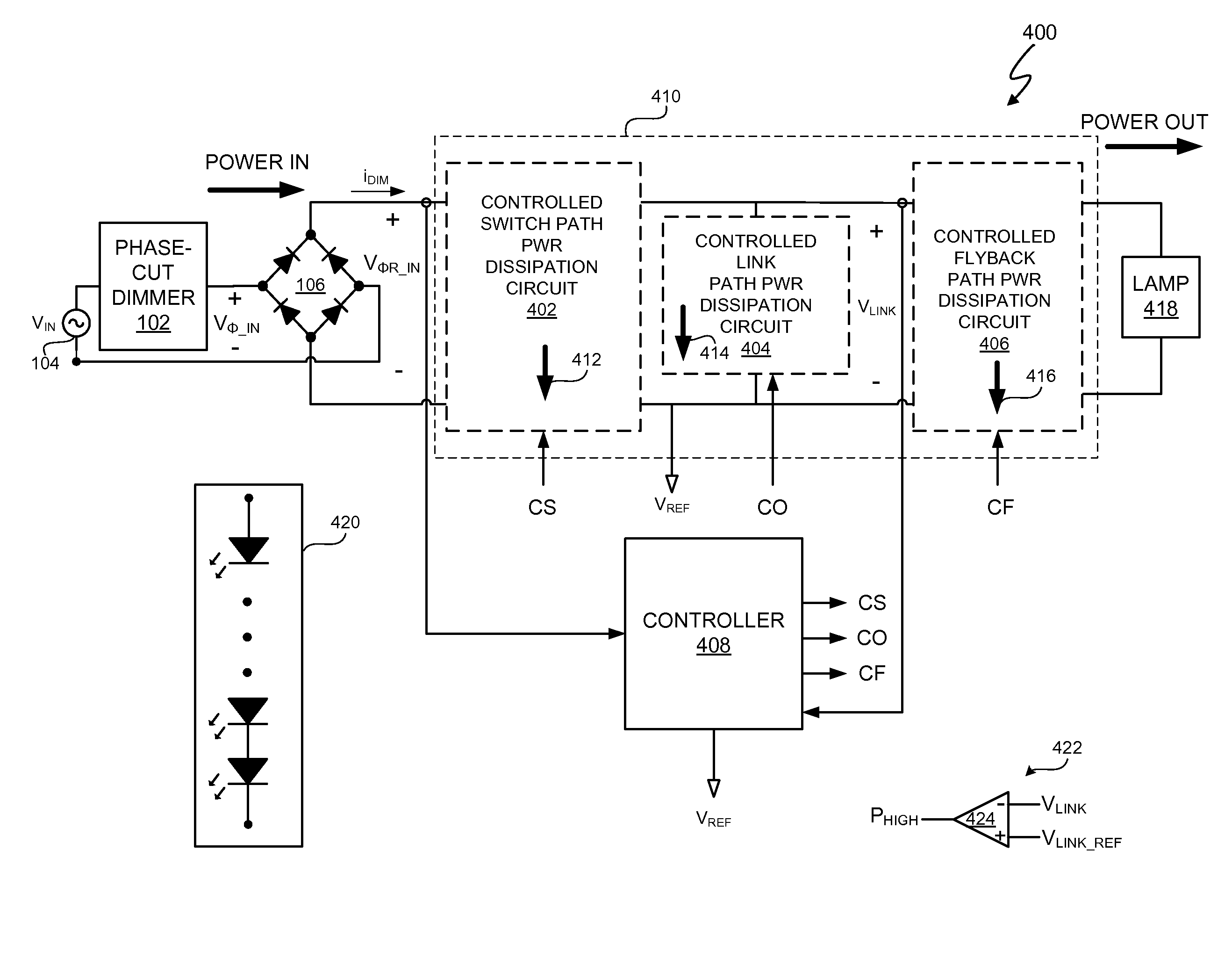

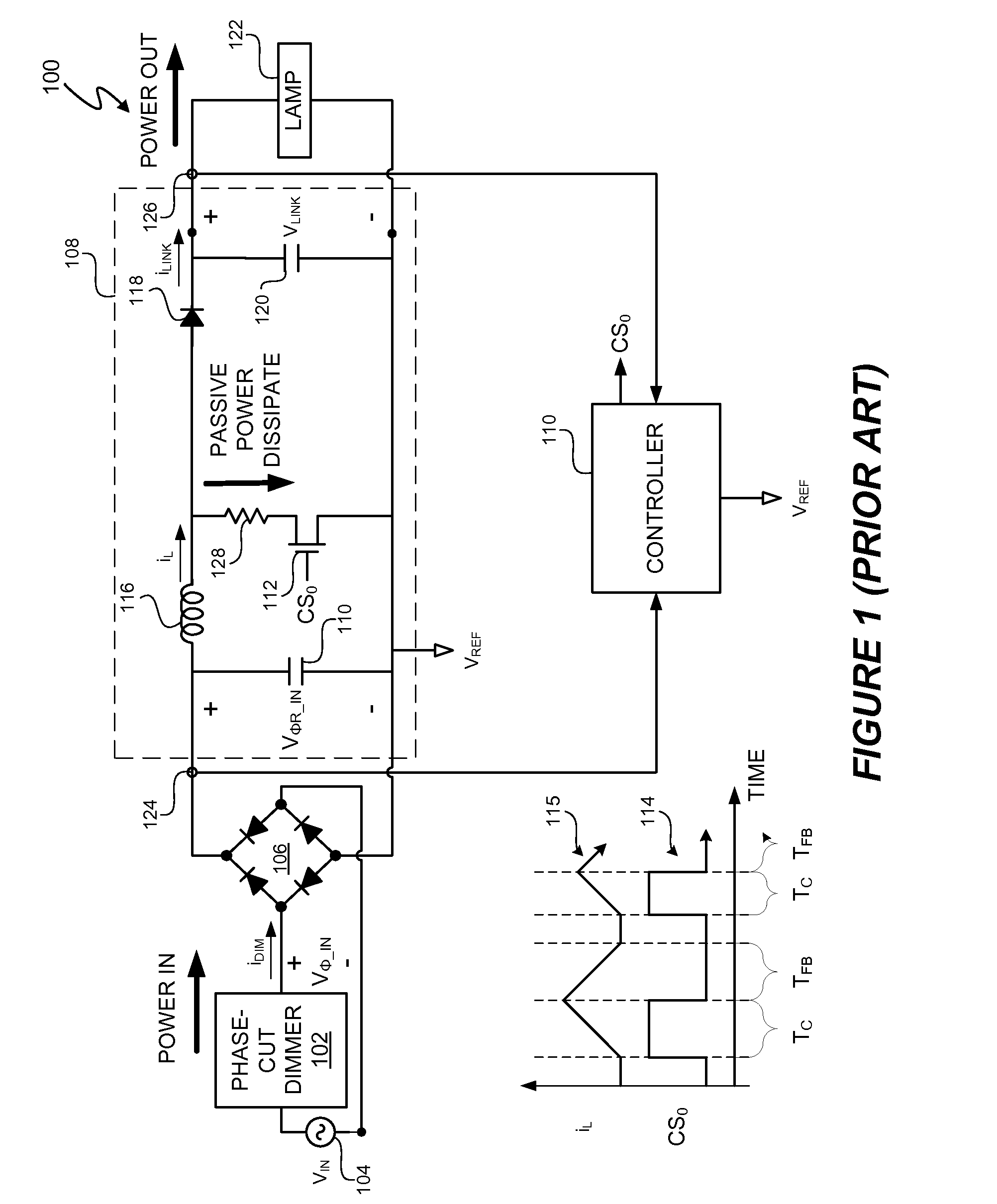

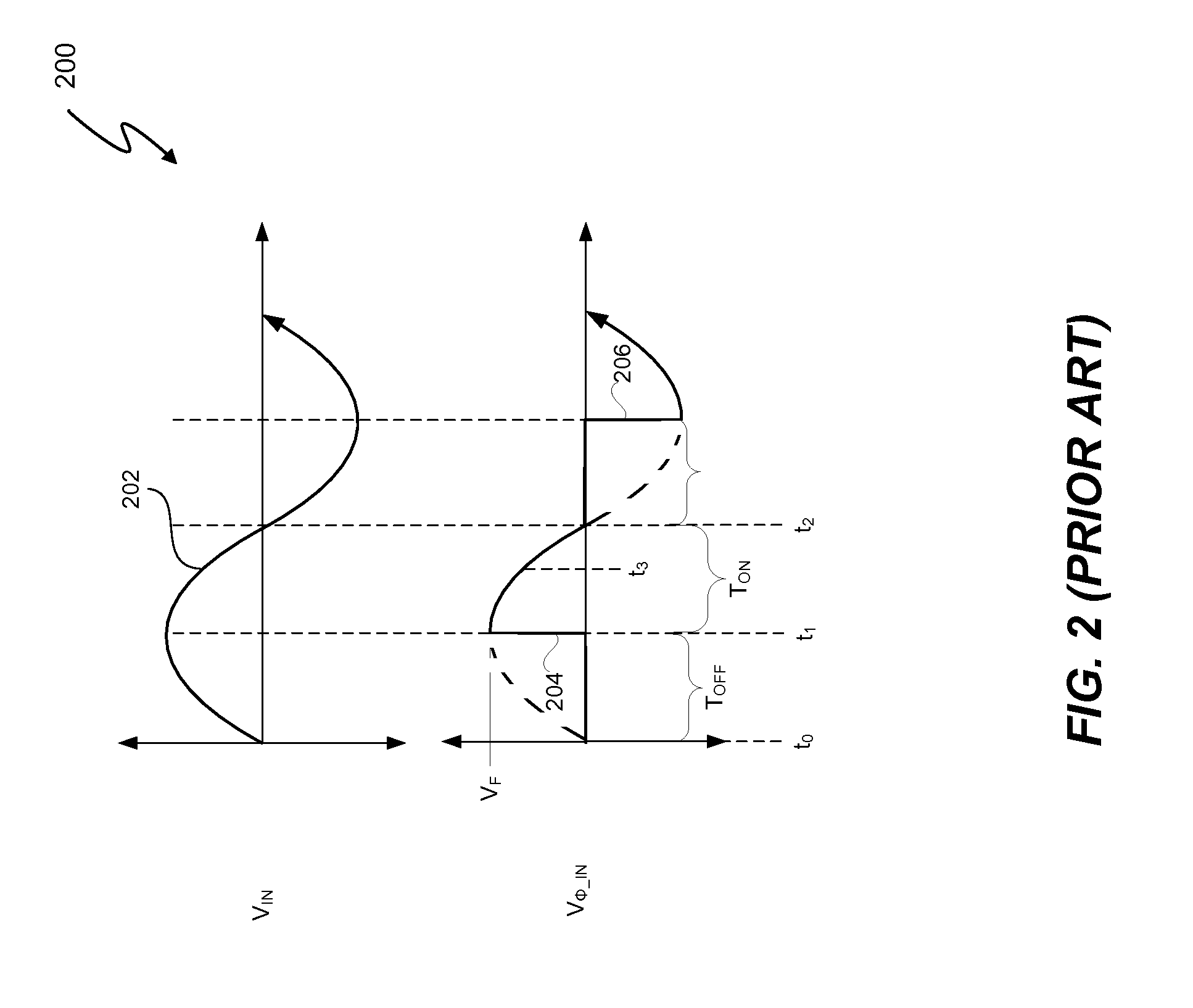

Controlled Power Dissipation In A Switch Path In A Lighting System

InactiveUS20120286684A1Minimize power consumptionIncrease energy dissipationEfficient power electronics conversionElectroluminescent light sourcesLeading edgeControl power

A lighting system includes one or more methods and systems to control dissipation of excess power in the lighting system when the power into a switching power converter from a leading edge, phase-cut dimmer is greater than the power out of the switching power converter. In at least one embodiment, the lighting system includes a controller that controls dissipation of excess energy in the lighting system to prevent a premature disconnection of the phase-cut dimmer. In at least one embodiment, the controller actively controls power dissipation by generating one or more signals to actively and selectively control power dissipation in the lighting system. By actively and selectively controlling power dissipation in the lighting system, the controller intentionally dissipates power when the power into the lighting system should be greater than the power out to a lamp of the lighting system. In at least one embodiment, the controller creates one or more intermixed and / or interspersed power dissipation phases with one or more switching power converter charging and / or flyback phases.

Owner:SIGNIFY HLDG BV

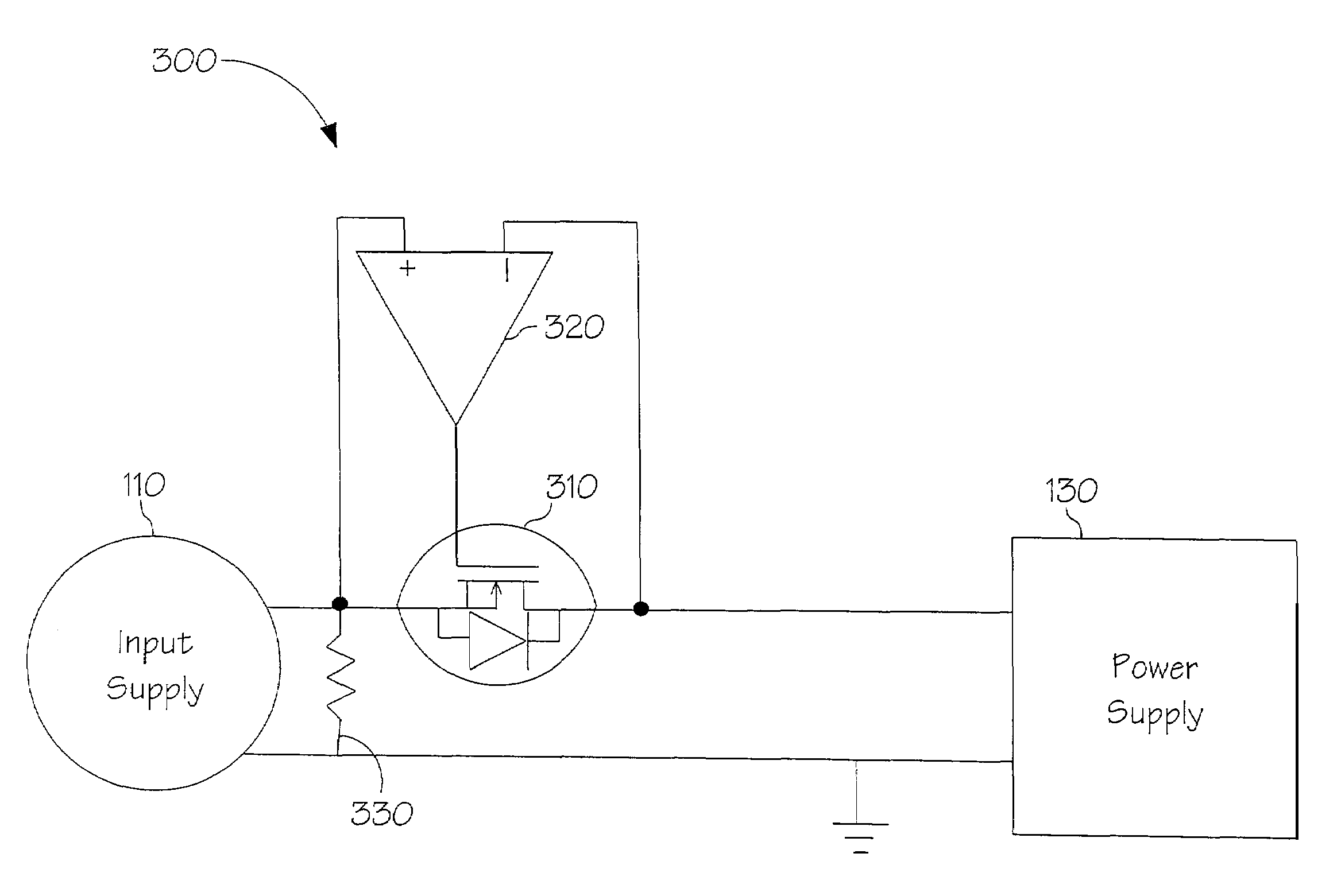

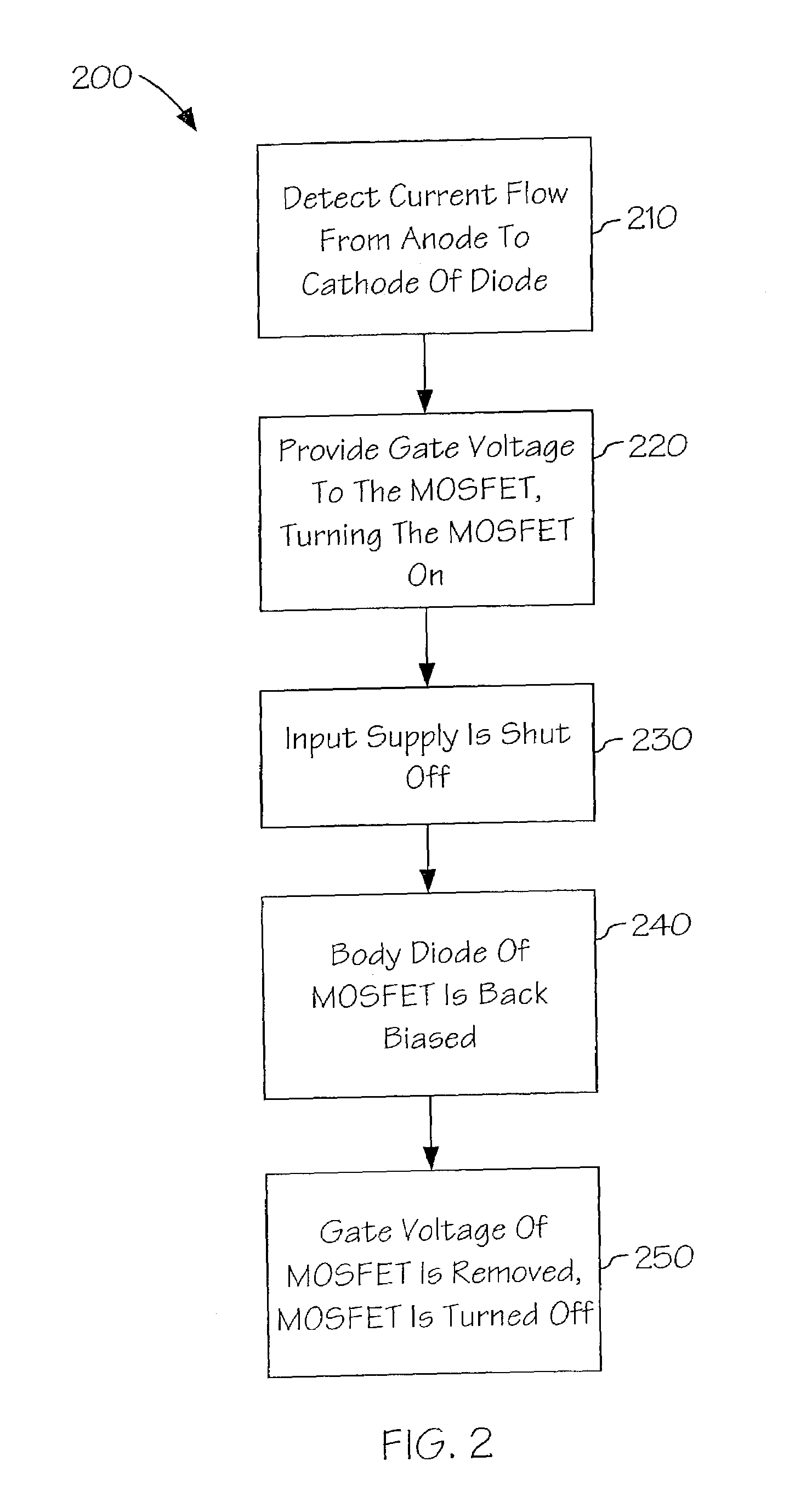

Input and output isolating diode for power dissipation reduction of power supplies

InactiveUS7379282B1Minimize power consumptionPower dissipationTransistorDc network circuit arrangementsMOSFETTime delays

The present invention is a method and system for providing improved isolation for power supplies while minimizing power dissipation. A body diode of a MOSFET may be utilized with a comparator circuit. The comparator circuit may detect current flow across the MOSFET and may turn the MOSFET on. This may shunt the diode with a low drain to source resistance limiting power dissipation across the diode to an amount of the drain to source current squared (Ids2) times the drain to source resistance of the MOSFET when on (RDSon). Use of the comparator circuitry may reduce the time delay associated with turning the MOSFET off to prevent a high reverse inrush current within a power supply.

Owner:NETWORK APPLIANCE INC

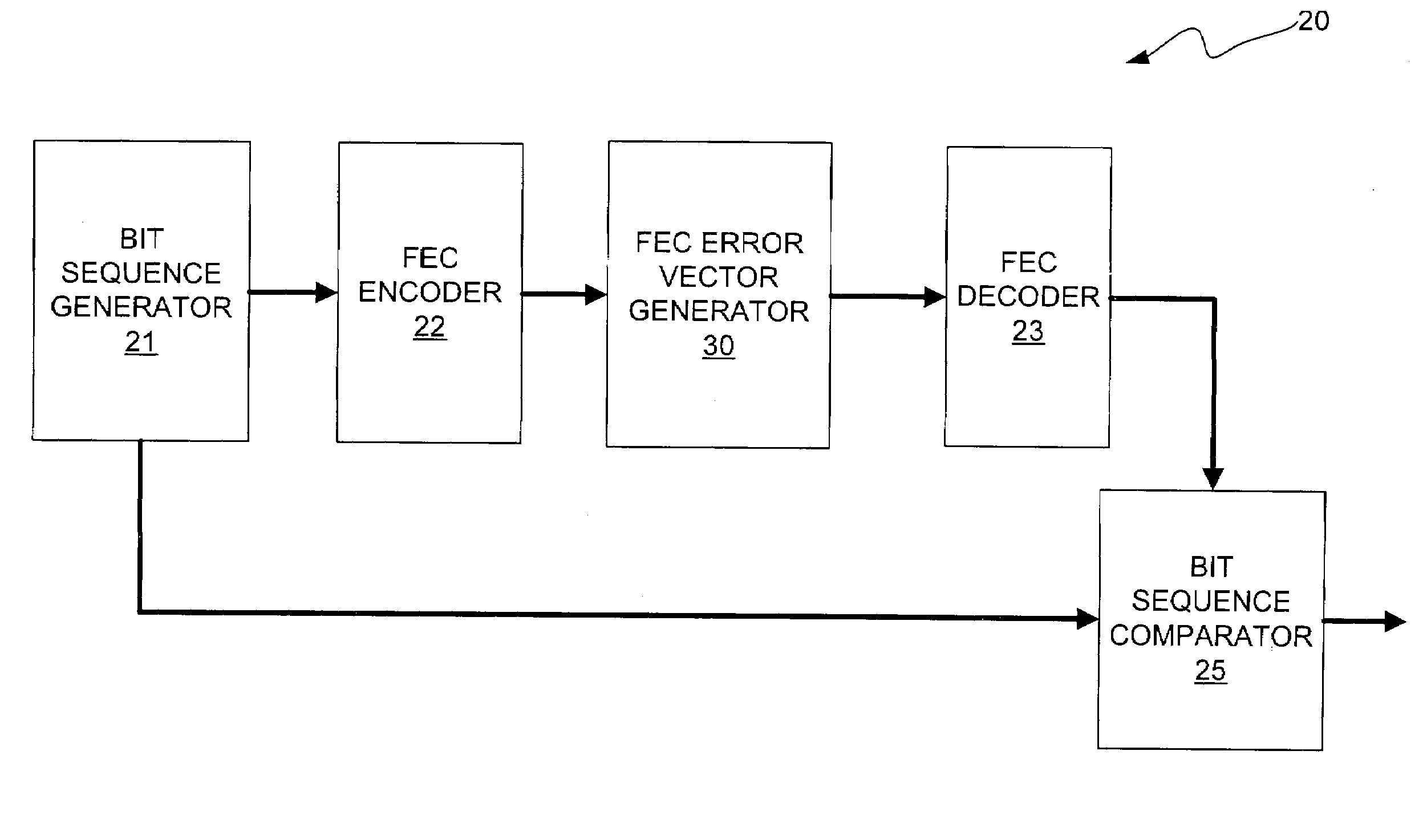

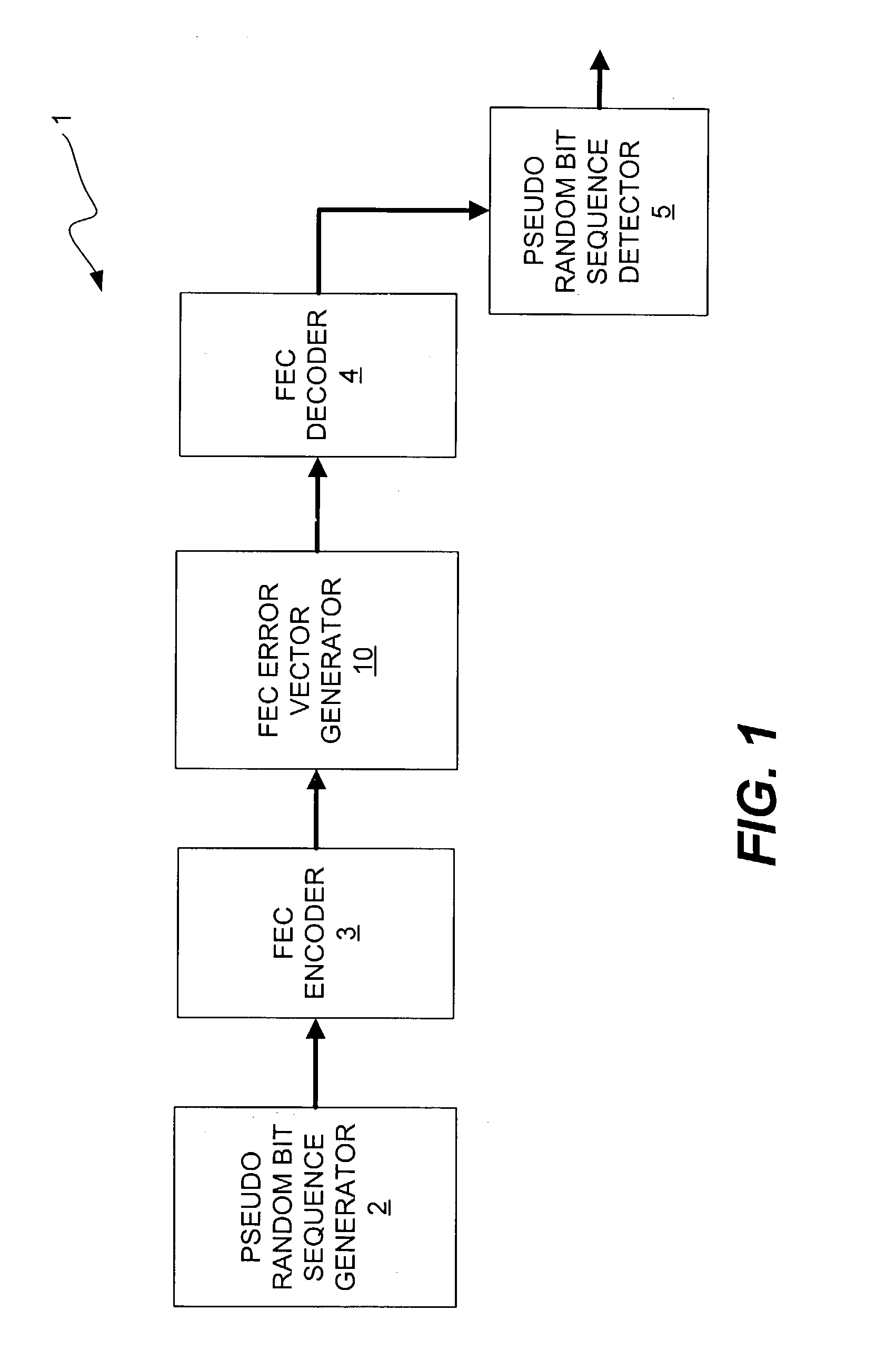

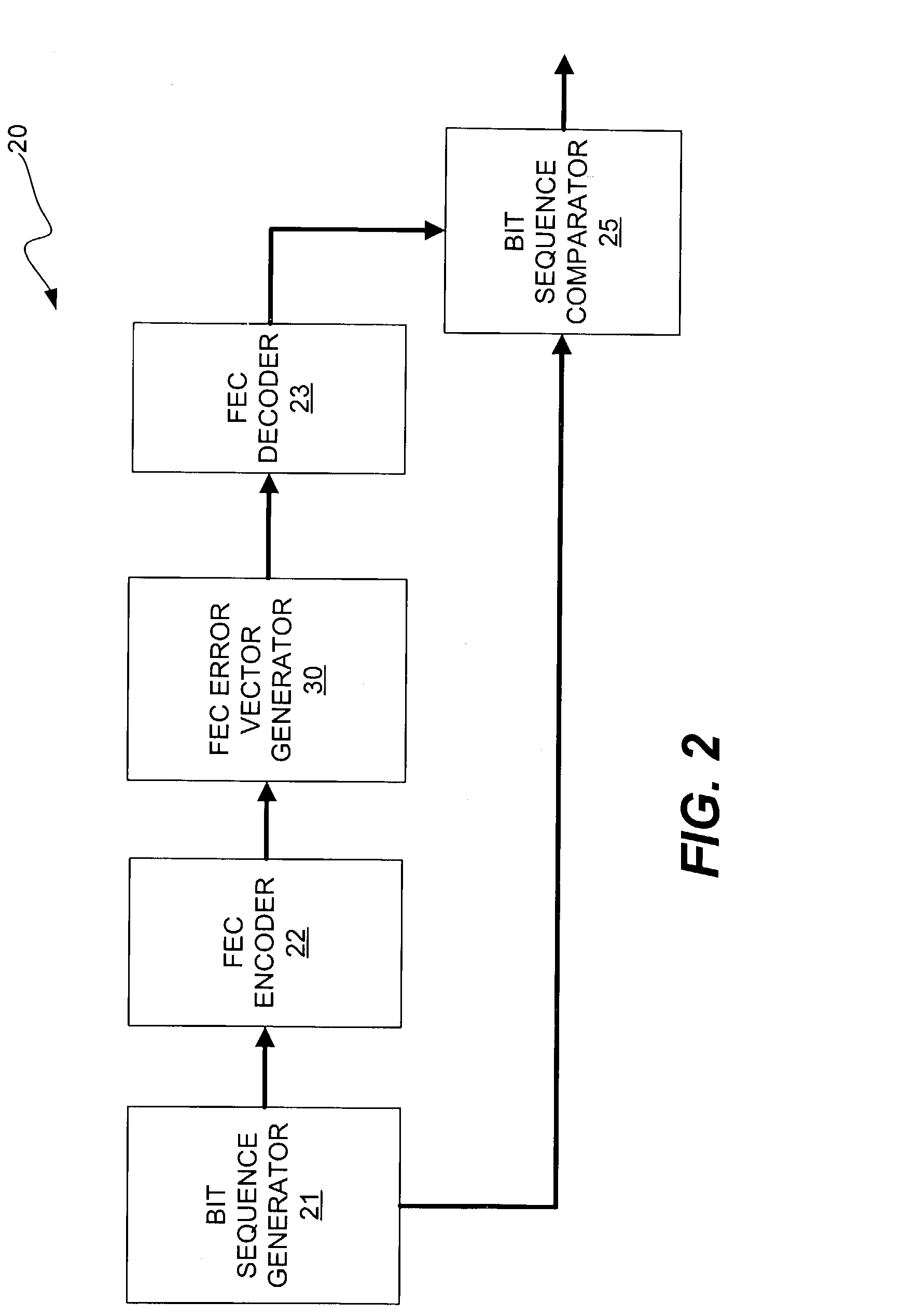

Method and apparatus for generating bit errors in a forward error correction (FEC) system to estimate power dissipation characteristics of the system

ActiveUS7073117B1Precision productionPower dissipationData representation error detection/correctionCode conversionFir systemForward error correction

A method and apparatus for generating and inserting bit errors in data words that have been encoded in a forward error correction (FEC) system in order to estimate power dissipation. In accordance with the present invention, it has been determined that a burst error generator that is capable of erroring the maximum number of correctable data bits in every FEC encoded frame, which allows the designer to accurately produce test vectors that are suitable for use in commercially available power estimation tools. In addition, after the IC is produced, the burst error generator of the present invention can be enabled to provide real-time FEC power dissipation data for use in system thermal modeling, thus obviating the need to use costly external devices that emulate a given error rate. Furthermore, the power dissipation data obtained in real-time may be used to refine the initial design power estimate, which will then allow the designer to develop a more accurate prediction of power consumption for future IC designs. Thus, the burst error generator of the present invention is capable of reducing iterations of IC designs by accurately estimating the worst-case power dissipation of FEC decoders.

Owner:CIENA

Adaptive camera and illuminator eyetracker

ActiveUS8339446B2Increase probabilityPower dissipationPrintersProjectorsImaging qualityActive camera

Owner:TOBII TECH AB

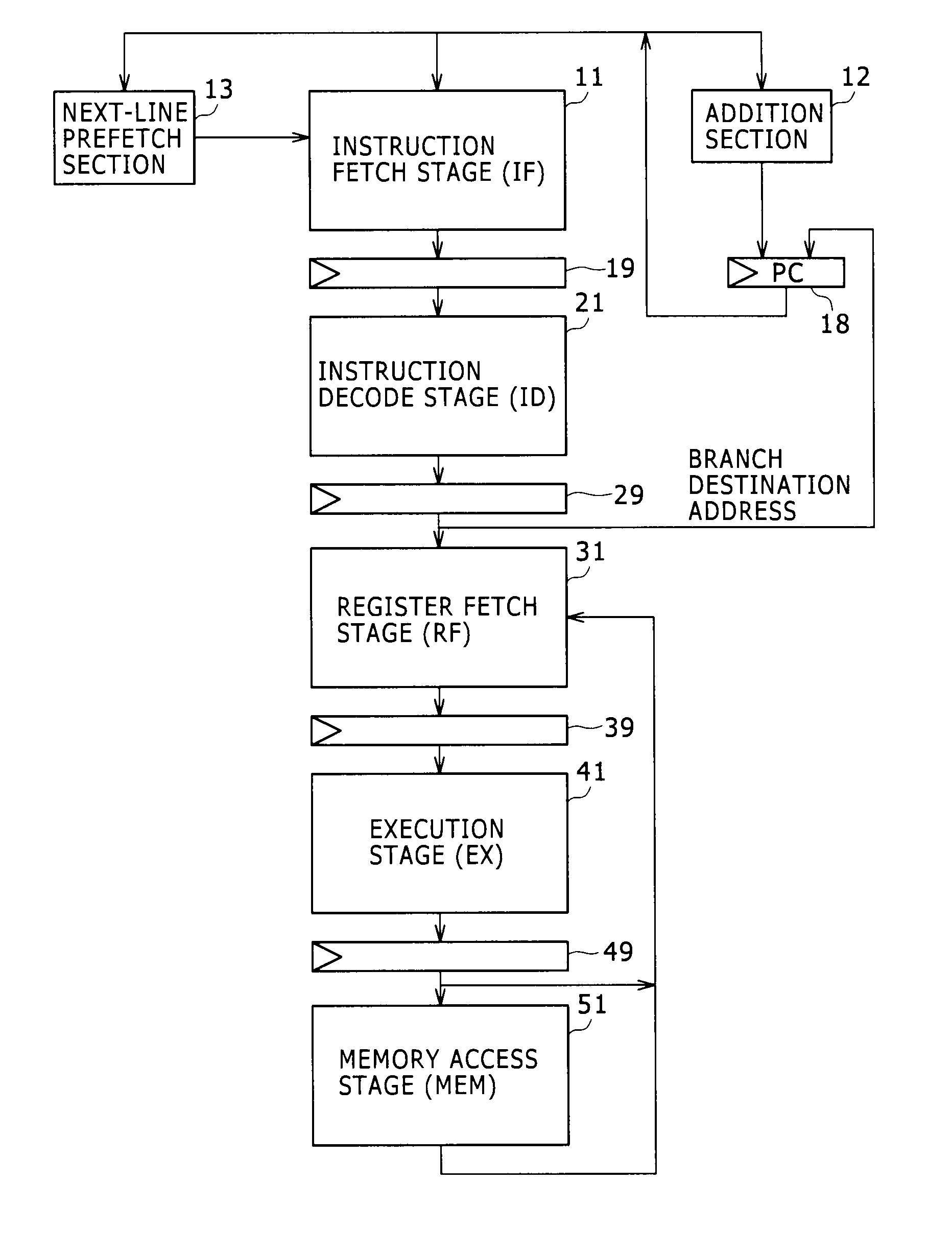

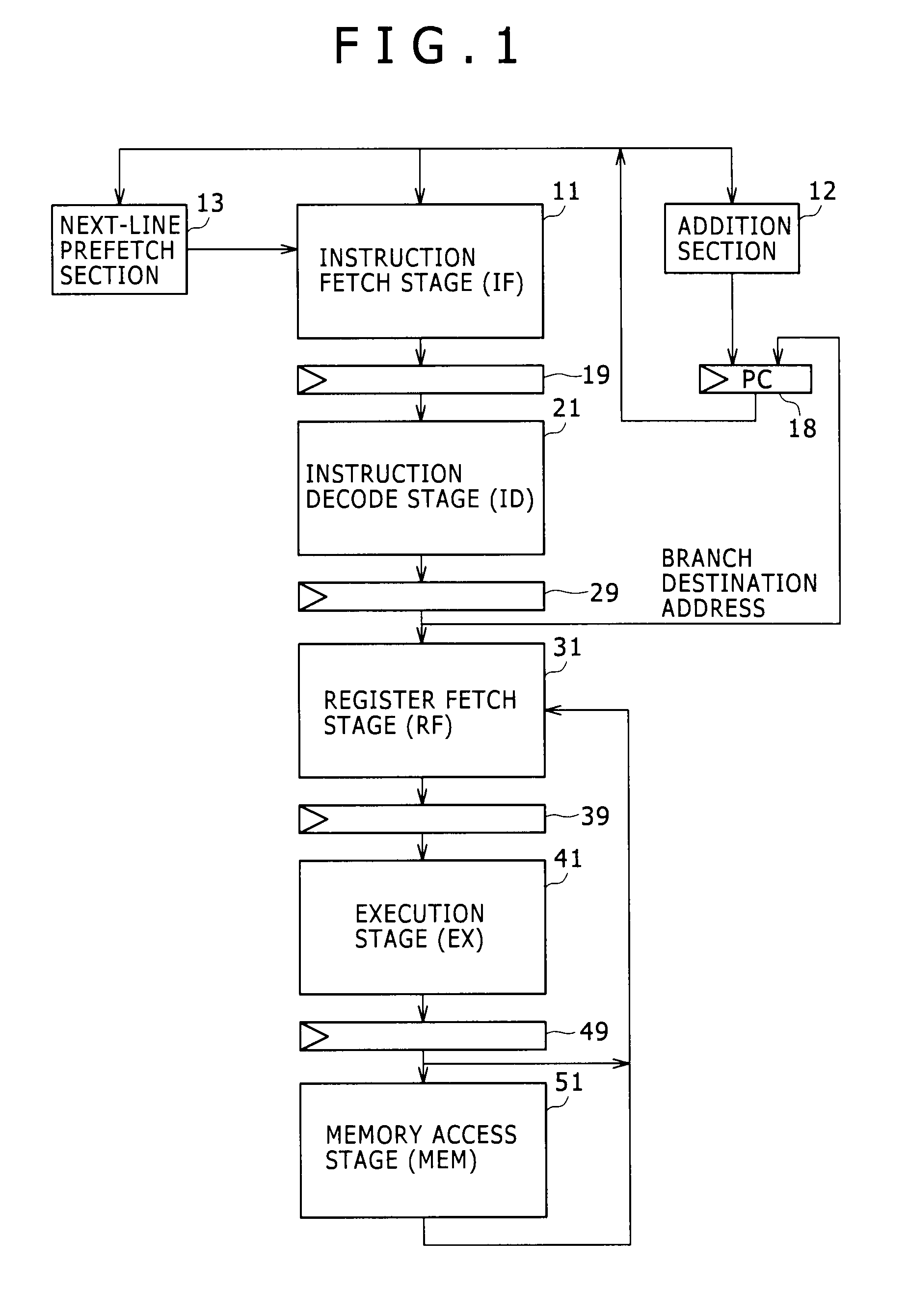

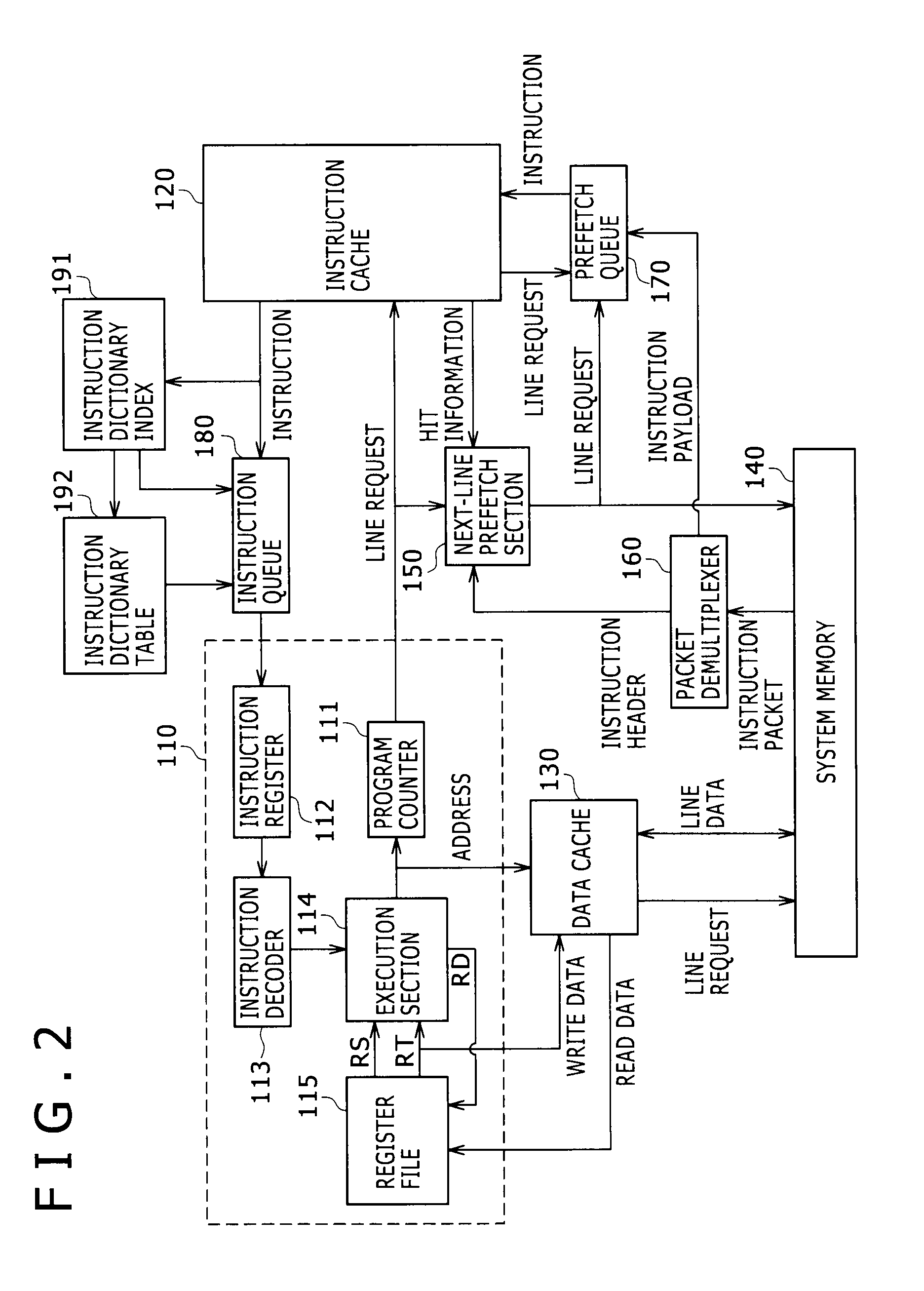

Instruction fetch apparatus and processor

InactiveUS20110238953A1Minimizing penaltyEasy accessDigital computer detailsMemory systemsParallel computingInstruction prefetch

An instruction fetch apparatus is disclosed which includes: a detection state setting section configured to set the execution state of a program of which an instruction prefetch timing is to be detected; a program execution state generation section configured to generate the current execution state of the program; an instruction prefetch timing detection section configured to detect the instruction prefetch timing in the case of a match between the current execution state of the program and the set execution state thereof upon comparison therebetween; and an instruction prefetch section configured to prefetch the next instruction upon detection of the instruction prefetch timing.

Owner:SONY CORP

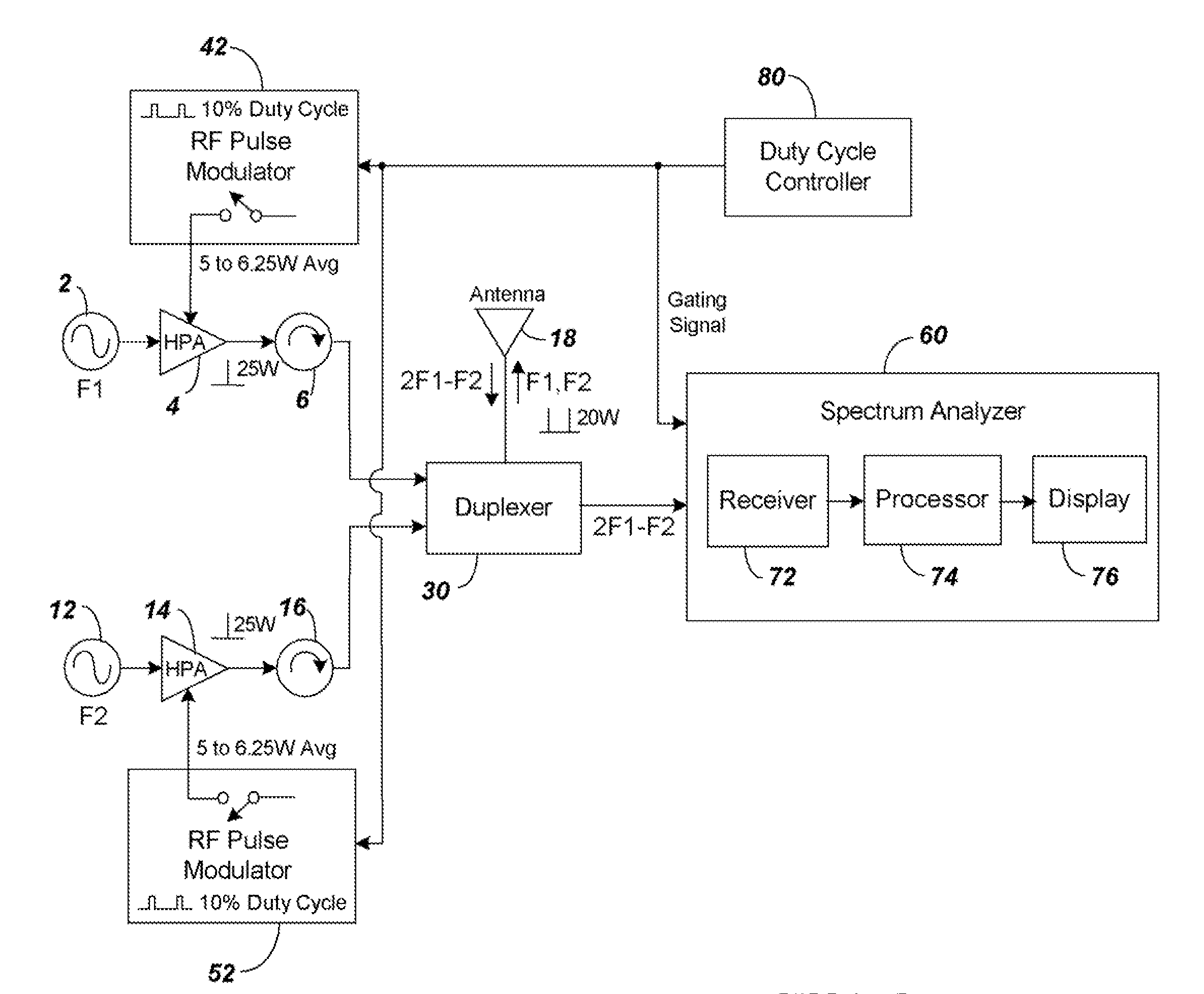

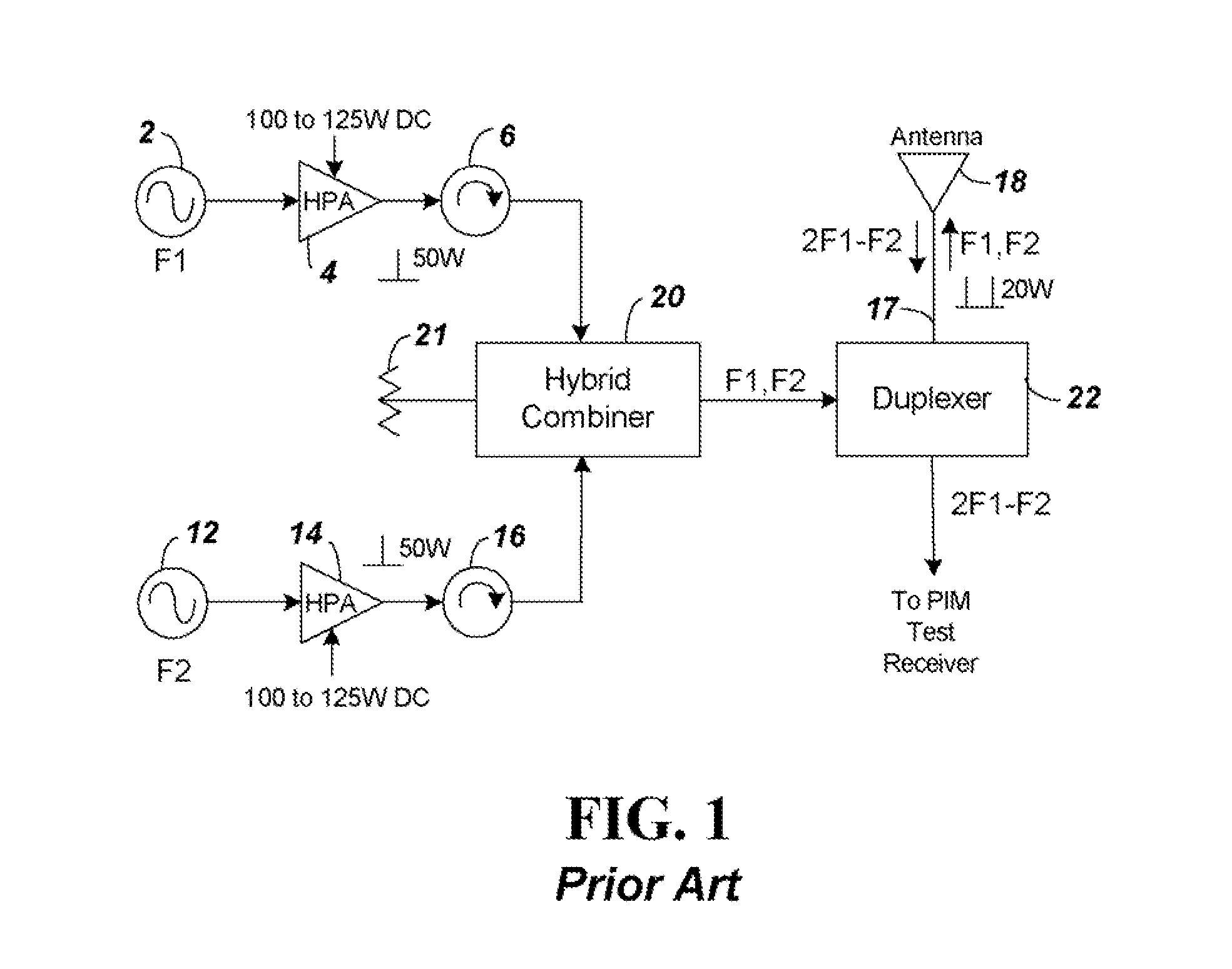

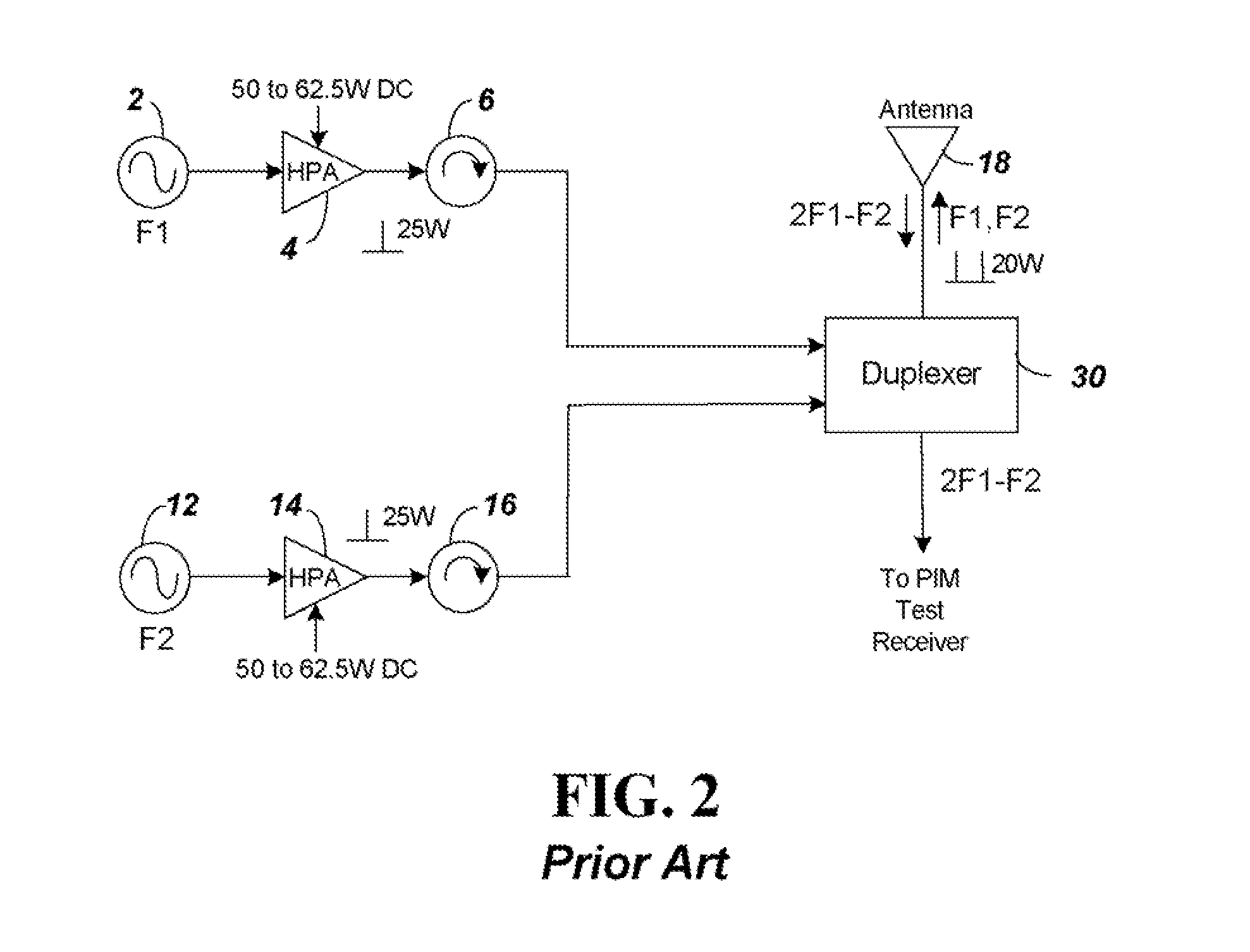

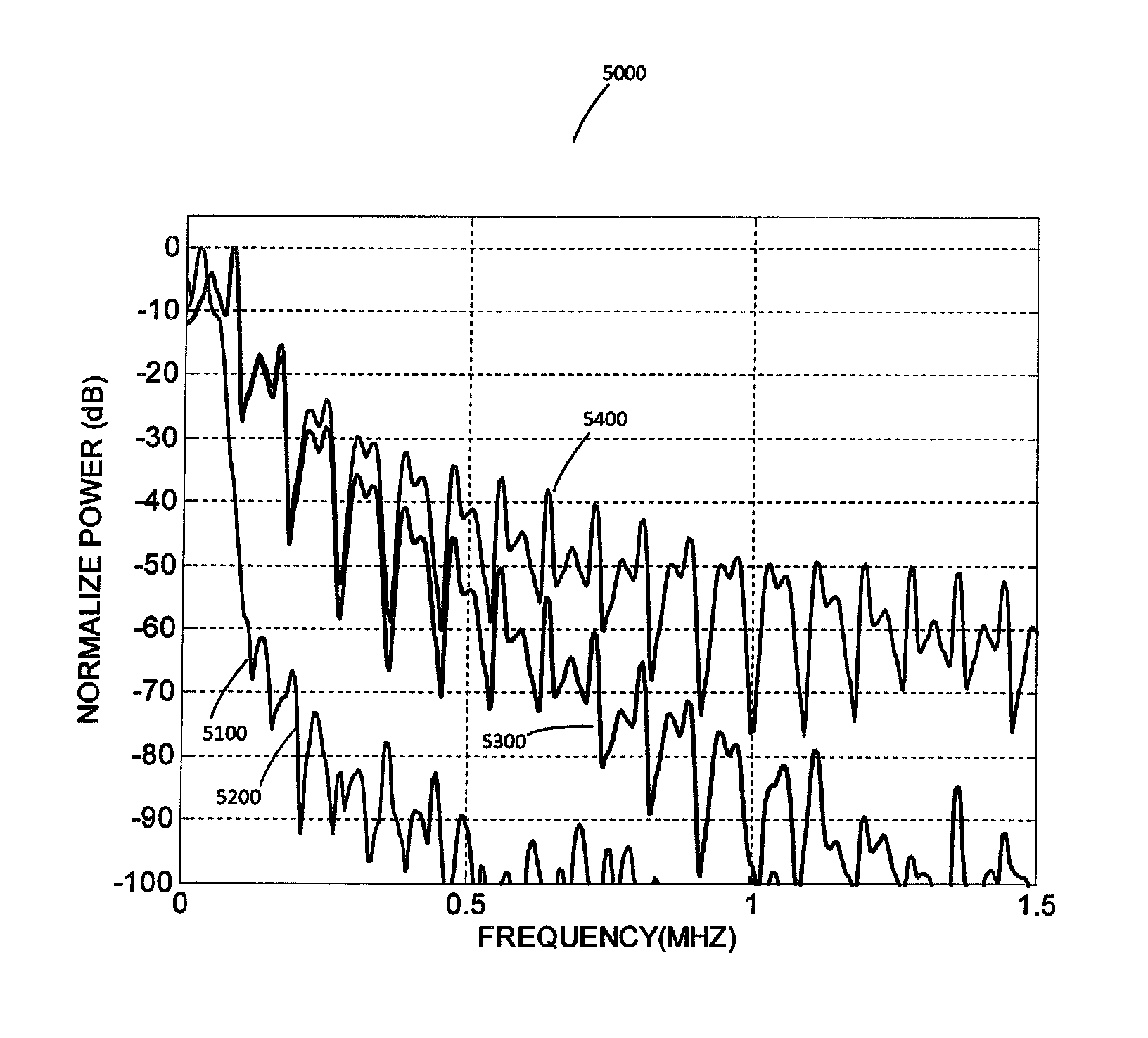

Pulse modulated PIM measurement instrument

ActiveUS8760148B1Reduced Power RequirementsMinimal sized partDynamo-electric motor metersMeasurement through mechanical displacementAudio power amplifierAnalog signal

A device to measure a passive intermodulation (PIM) creating component is provided that uses minimal average power. For a PIM measurement, two separate signals F1 and F2 are generated to simulate signals, such as from two different types of cell phone operating bands being transmitted in the same area or two different transmit frequencies within one cell phone operating band. PIMs are measured to assure interference is not created on one of the cell phone bands. Minimal power is used by connecting pulse width modulators (PWM) to provide DC power to the high power amplifiers (HPA) creating the signals F1 and F2. By controlling the duty cycle of the PWM to limit ON time of the HPAs to approximately 10%, significant average power savings occur. Size is also reduced with reduced power consumption because heat sinks and other cooling components are not required.

Owner:ANRITSU CO

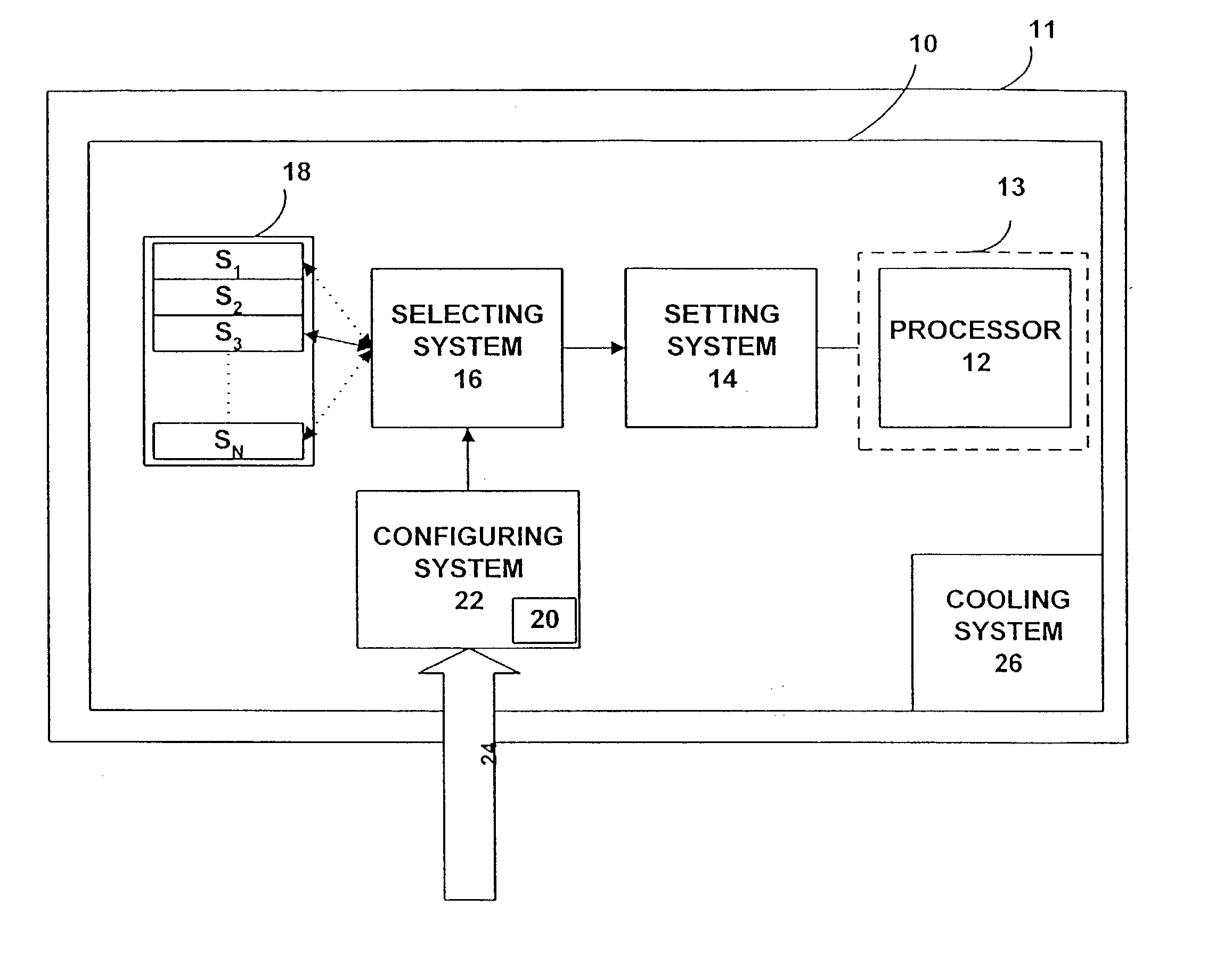

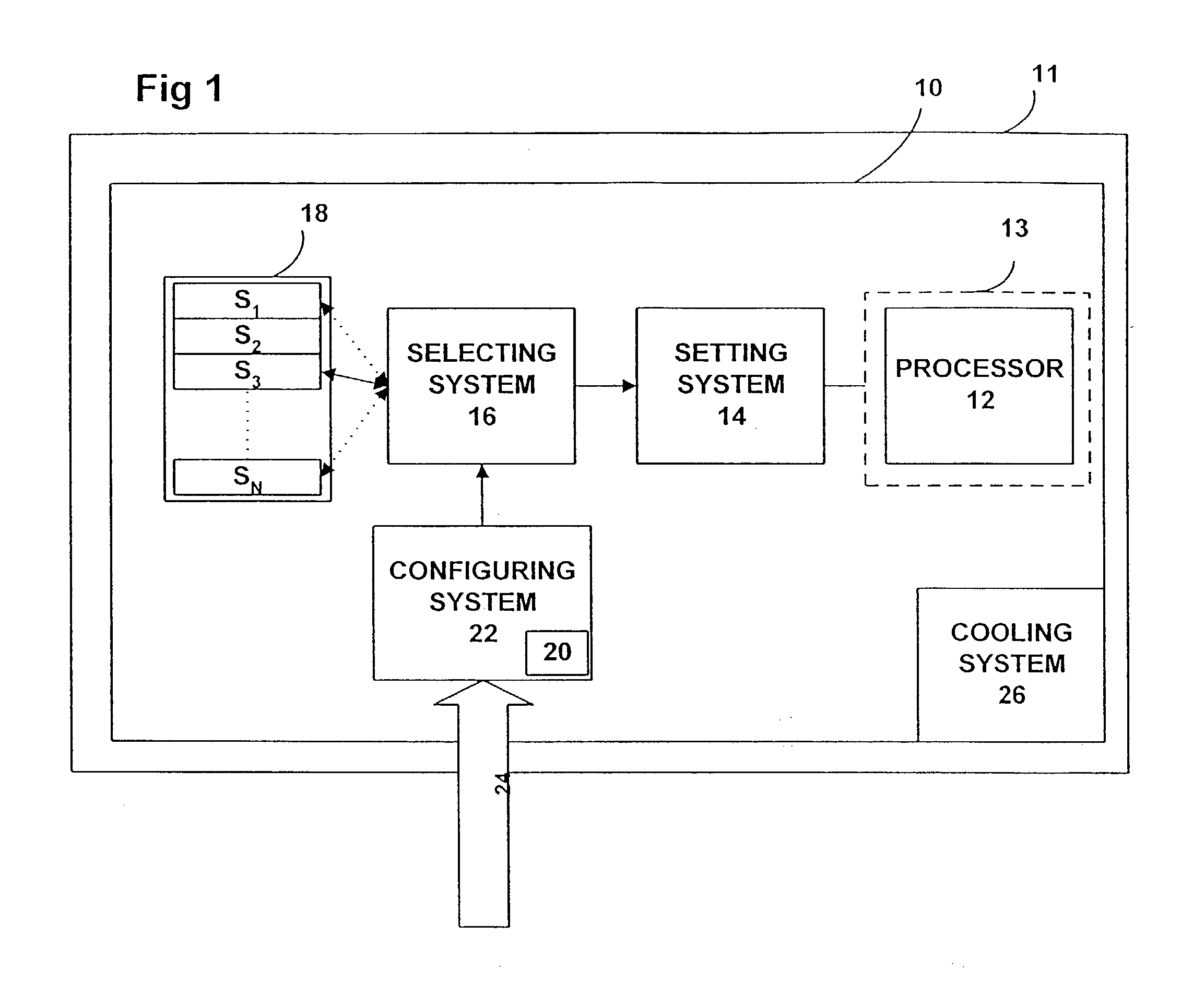

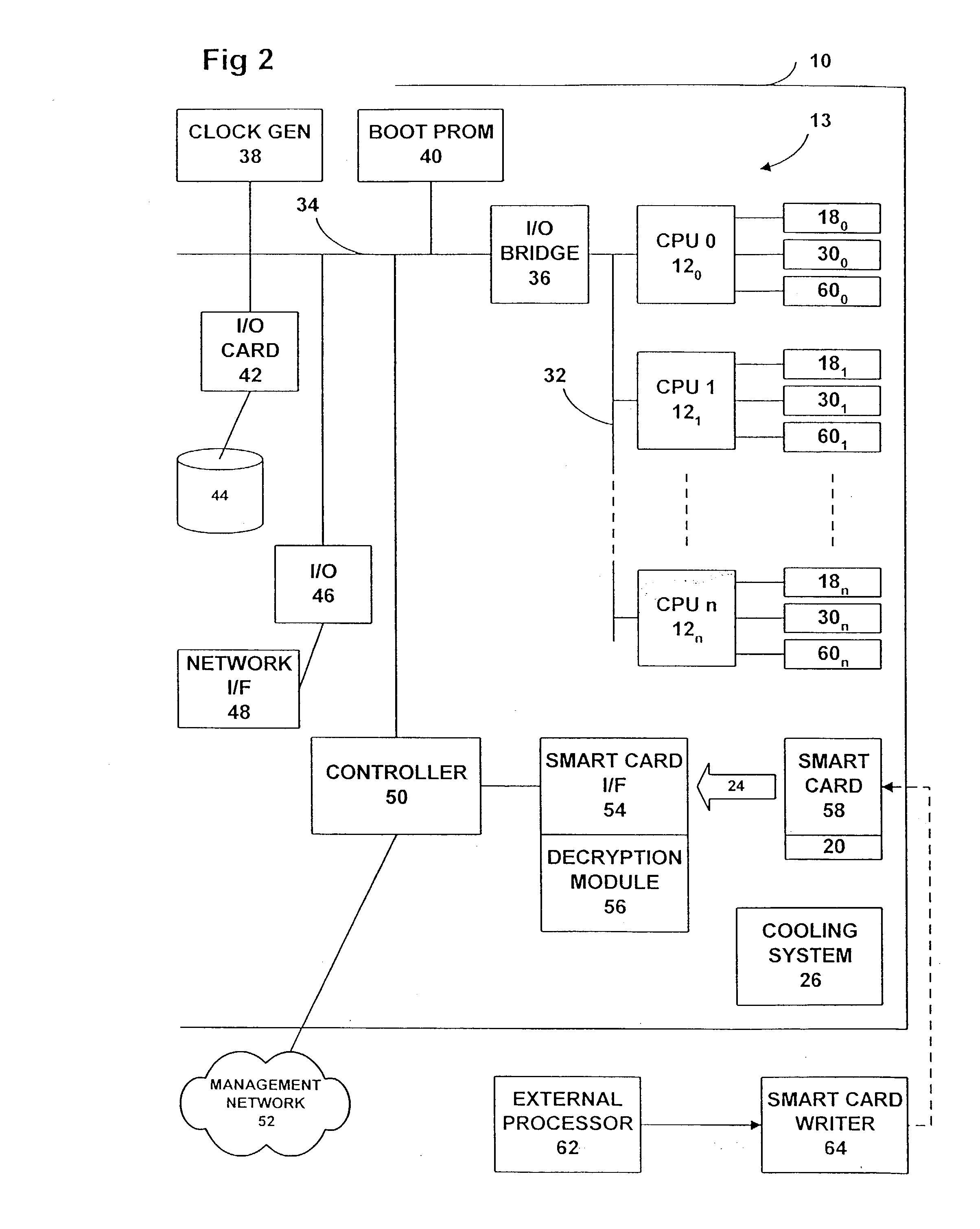

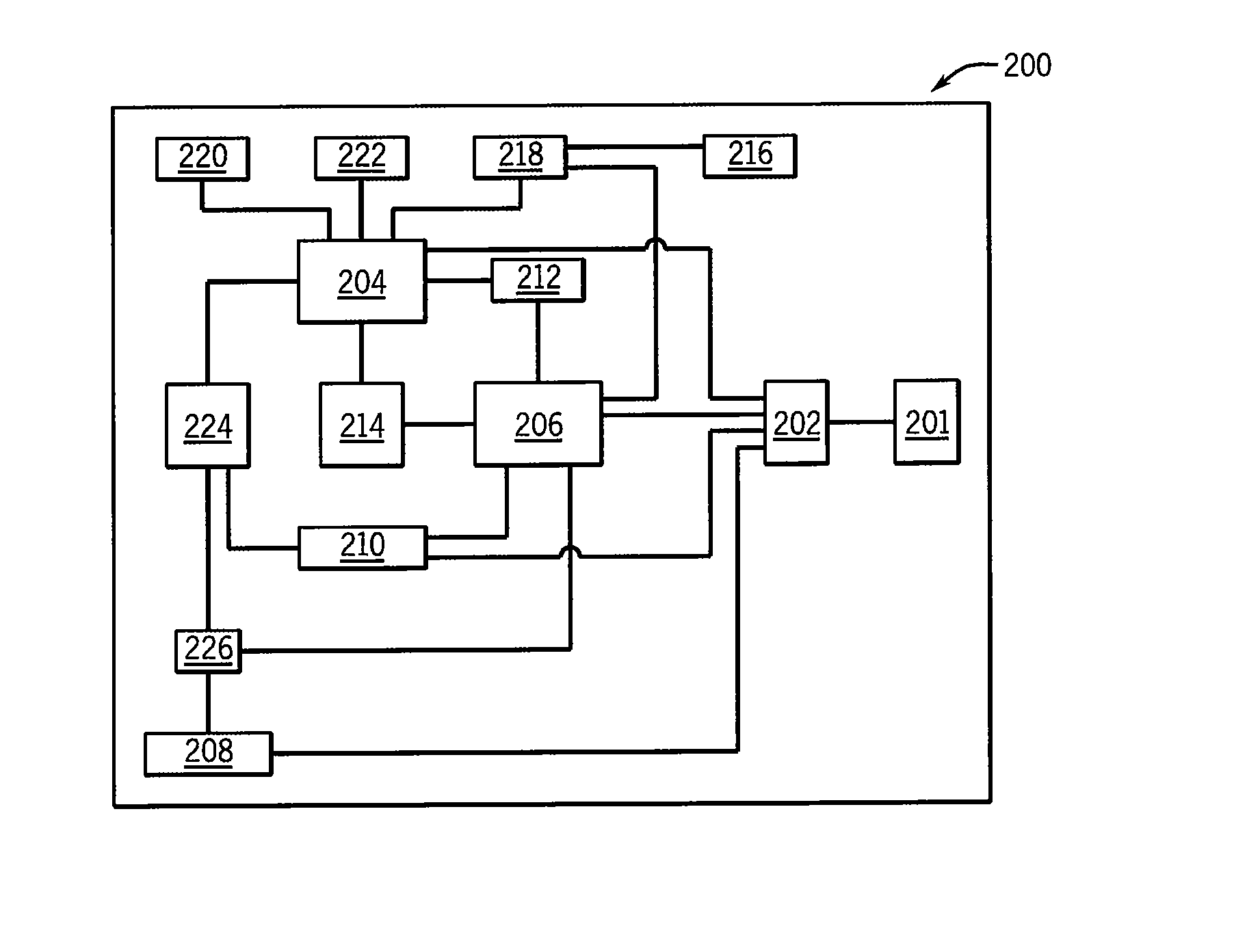

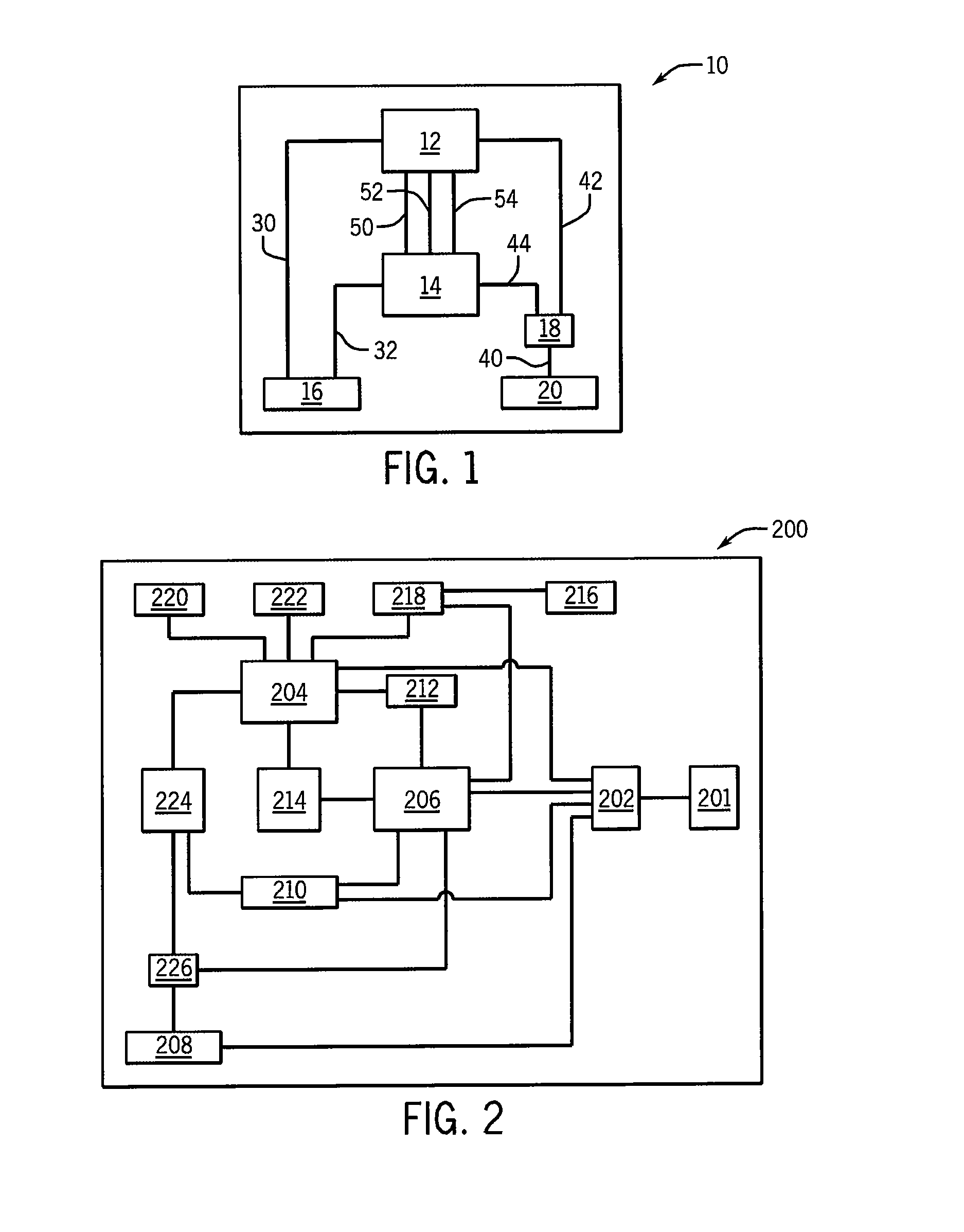

Configuring computer systems

ActiveUS20030229814A1Power dissipationReduce power consumptionDigital computer detailsData resettingOperating voltageComputerized system

A computer system 10 with one or more processors 12 can be configured to operate in any one of a number of thermal environments. A setting system 14 sets operating parameters of the computer system such as processor operating voltage and frequency. A selecting system 16 selects values of operating parameters for use in setting by responding to an input of configuring data 20 to select a set of parameter values from a parameter value storage memory 18. The configuring data 20 may be input by the insertion of a smart card 58. Such configuring is useful in adapting computer systems during manufacture for compliance with desired specifications without hardware modification.

Owner:ORACLE INT CORP

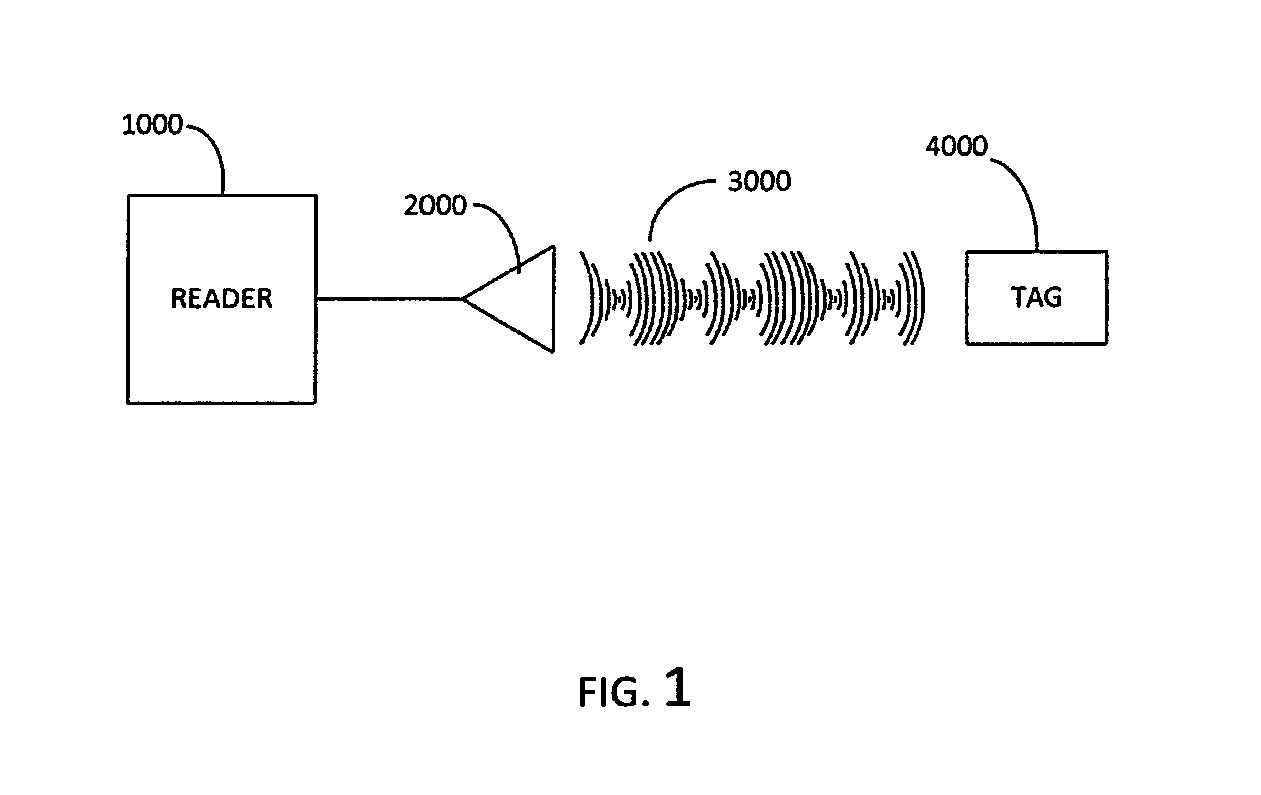

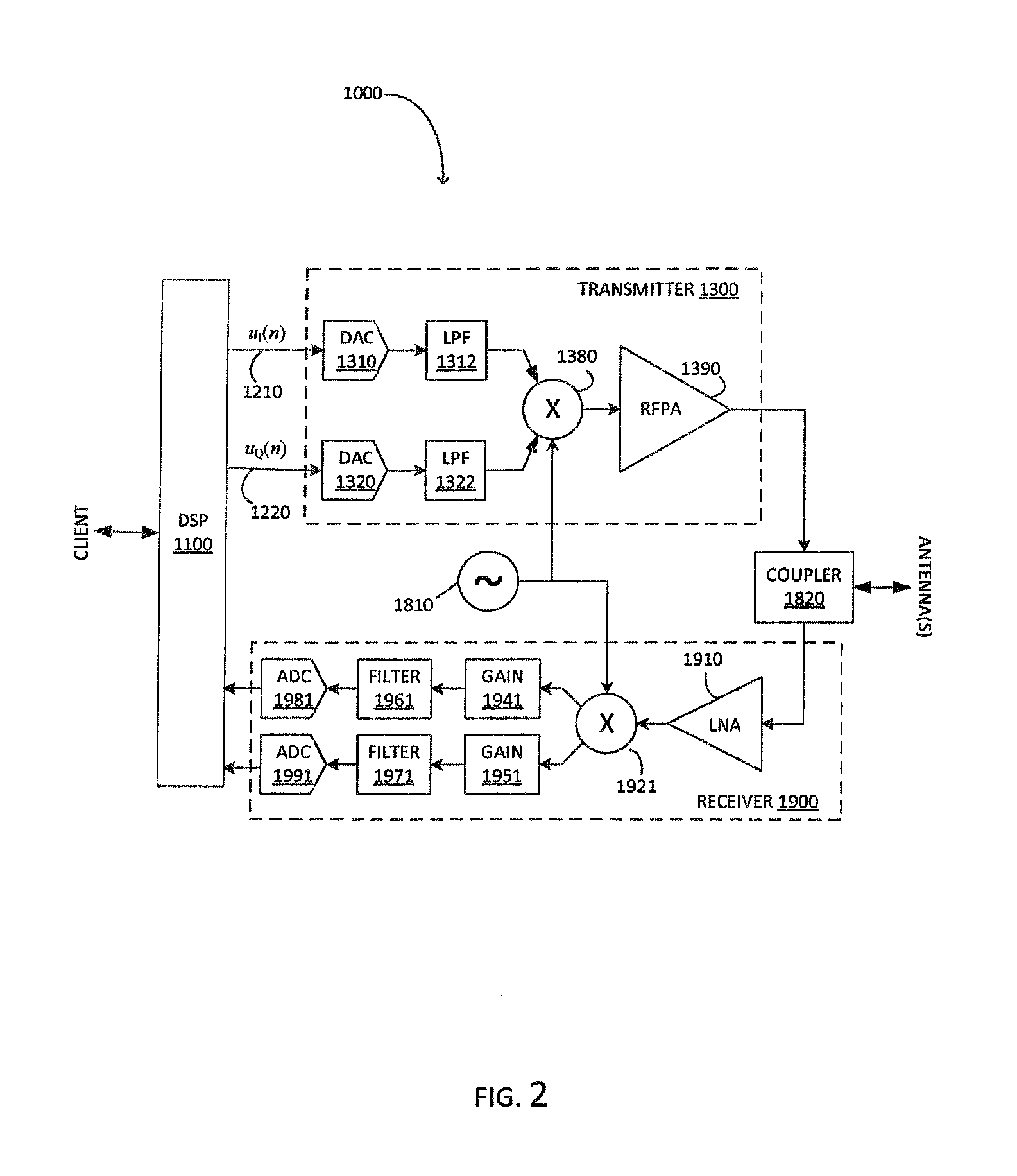

Polar transmitter for RFID reader

ActiveUS20170012675A1Low costImprove power efficiencyNear-field in RFIDAmplitude-modulated carrier systemsVIT signalsPhase modulation

A polar transmitter for an RFID reader and a system using the polar transmitter are disclosed. An RFID system according to at least some embodiments of the invention includes a polar transmitter employing a switch mode power amplifier. The system can also include a receiver to receive responses from RFID tags and a coupler connected to the polar transmitter, the receiver and one or more antennas. In at least some embodiments, the polar transmitter of the RFID system includes an envelope amplifier connected to the switch mode power amplifier to provide an envelope signal and a phase modulator connected to the switch mode power amplifier to phase modulate the switch mode power amplifier using a phase signal. In at least some embodiments, the polar transmitter of the RFID system transmits OPR-ASK signals to reduce AM modulation depth and provide a continuous phase signal for the phase modulator.

Owner:CLAIRVOYANT TECH INC

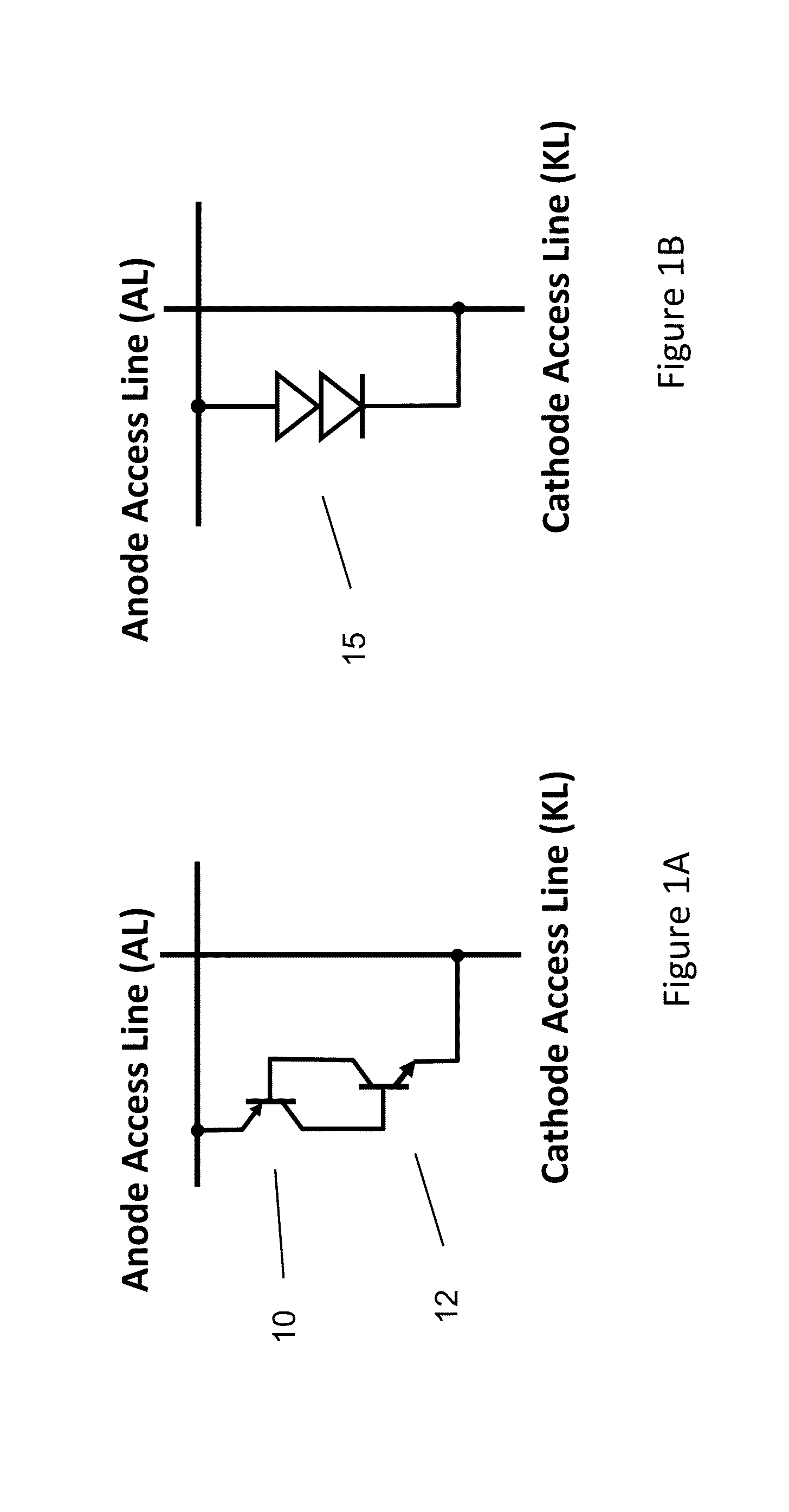

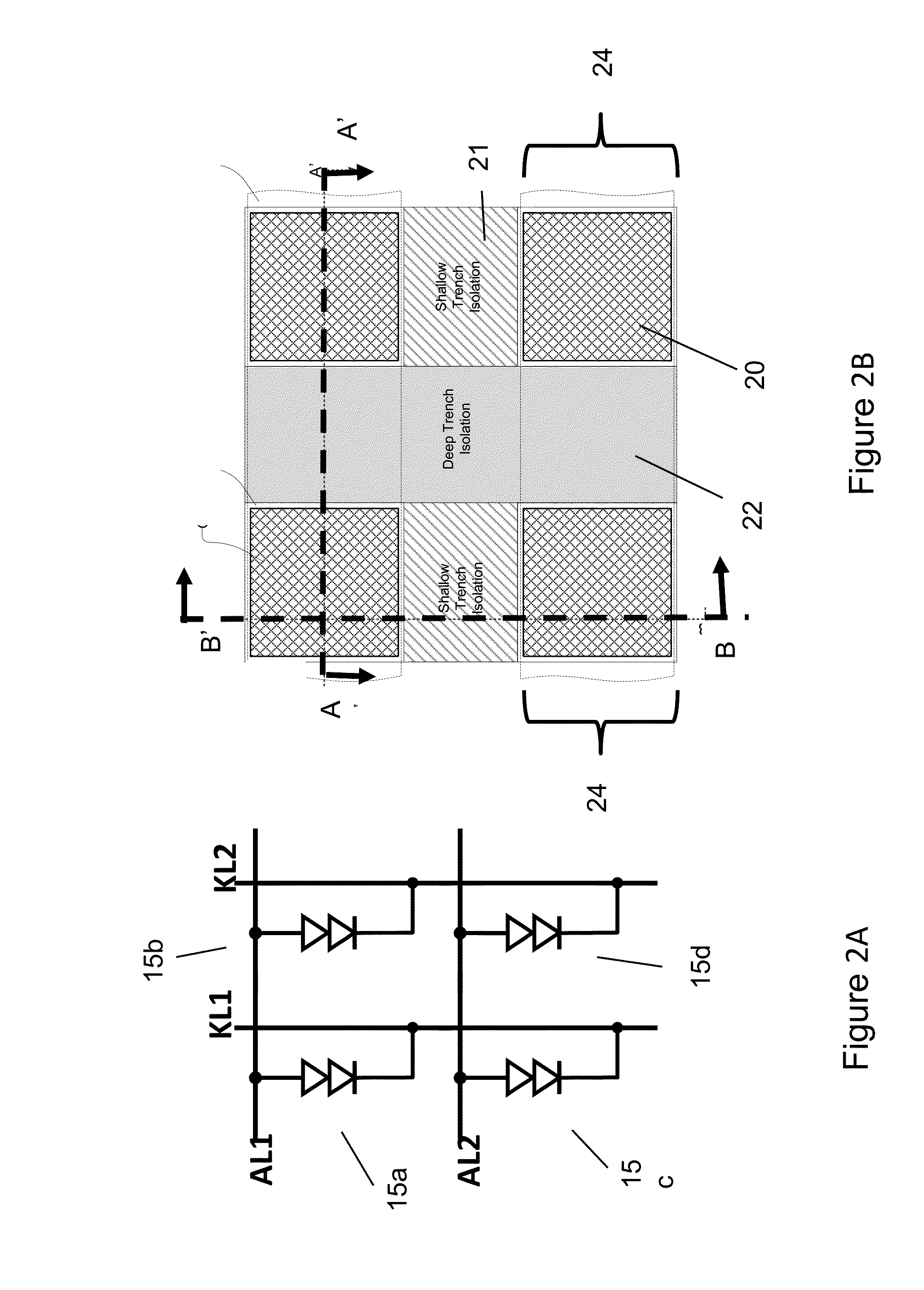

Thyristor Volatile Random Access Memory and Methods of Manufacture

InactiveUS20160093624A1Power dissipationControl power consumptionTransistorThyristorVolatile memoryThyristor

A volatile memory array using vertical thyristors is disclosed together with methods of fabricating the array.

Owner:SYNOPSYS INC

System and method for precharging and discharging a high power ultracapacitor pack

InactiveUS20060176028A1Increase powerEffective and low-cost and safeBatteries circuit arrangementsCharging stationsSwitchgearResistor

Owner:SHEPPARD MULLIN RICHTER & HAMPTON

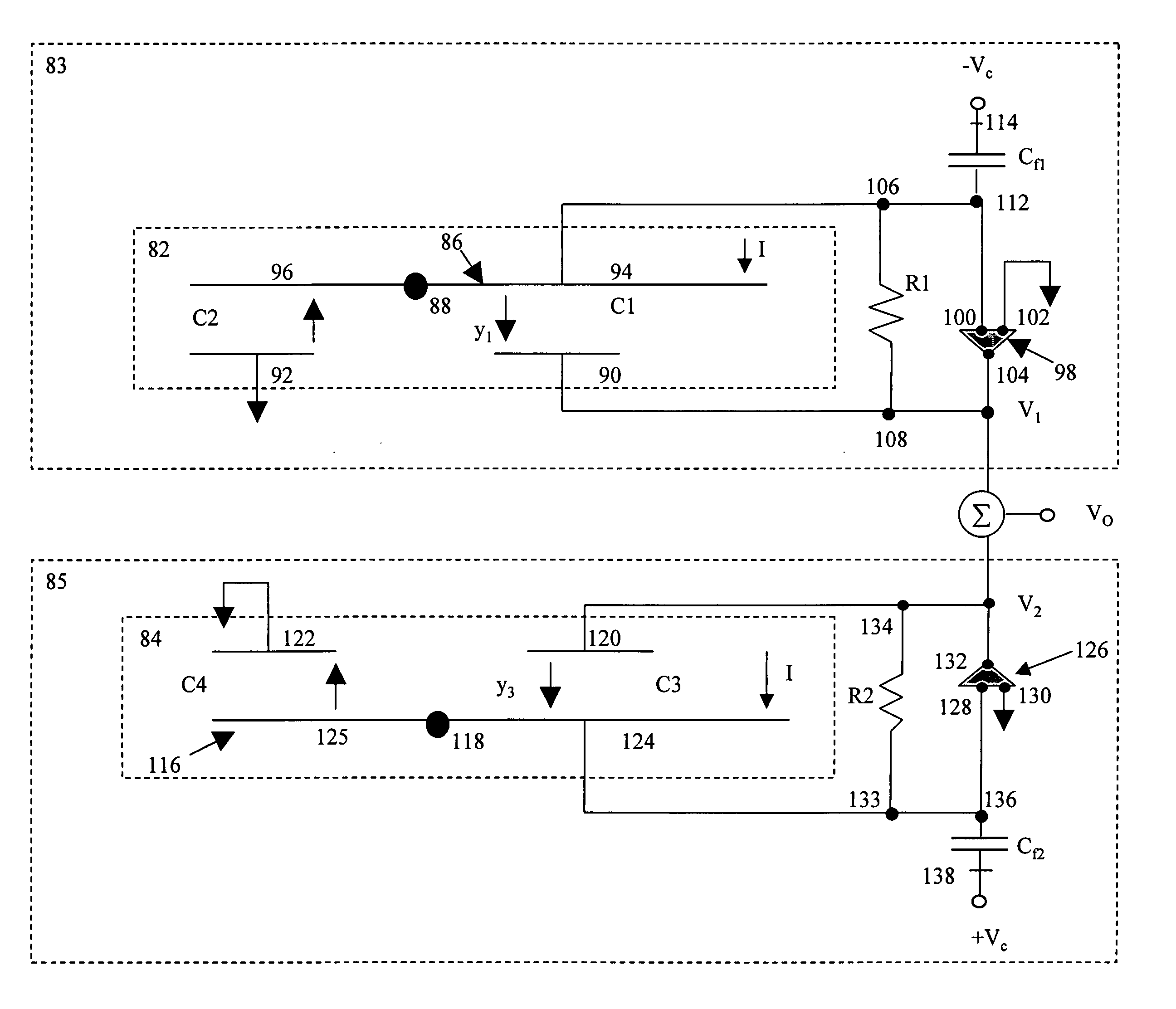

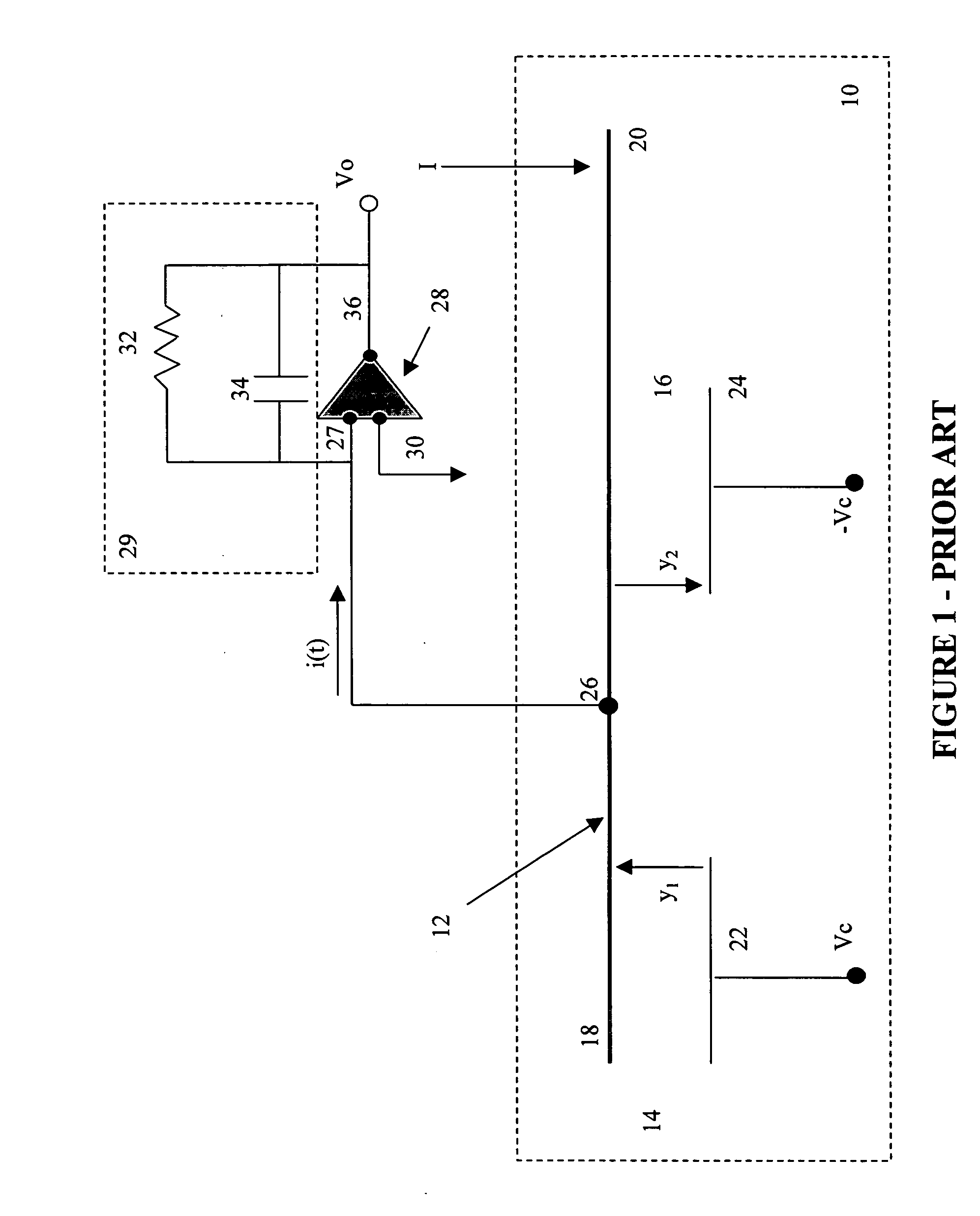

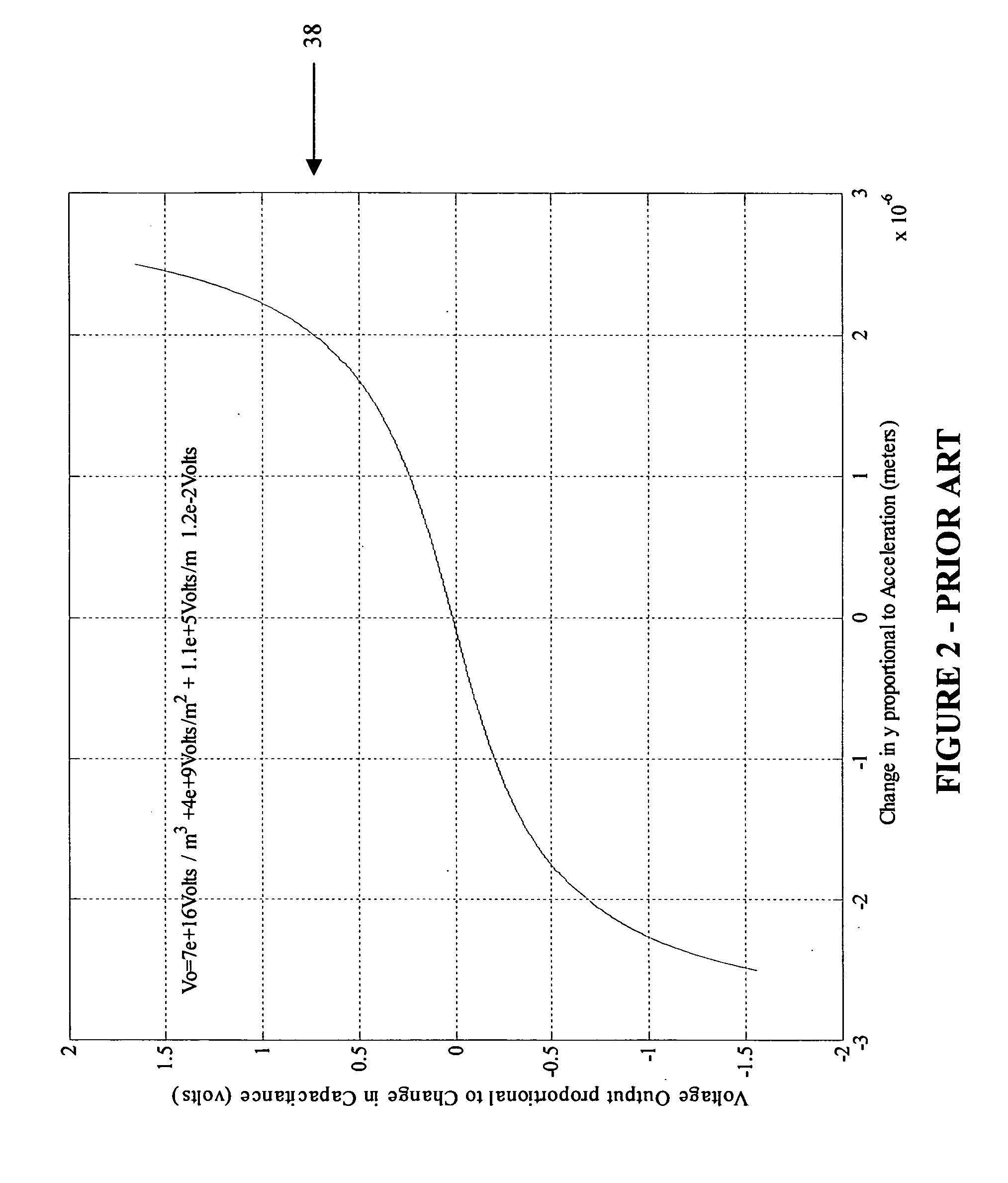

Apparatus for and method of sensing a measured input

ActiveUS20050145030A1Reduce capacitanceLimited bandwidthAcceleration measurement using interia forcesResistance/reactance/impedenceElectricityCapacitance

Apparatus is used in sensing a measured input. The apparatus includes a capacitor with a capacitance that varies non-linearly in response to the measured input, and a circuitry that derives, from the capacitance, a signal that varies substantially linearly with the measured input. The capacitor includes a first electrode, a second electrode, and a gap defined by a space between the electrode. The circuitry includes an amplifier with a first input terminal in electrical communication with the first electrode, a second input terminal, and an output terminal in electrical communication with the second electrode. The capacitance of the capacitor varies as an inverse of the gap of the capacitor, the gap of the capacitor varies in response to changes in the measured input, and the signal is derived from an output of the amplifier.

Owner:CHARLES STARK DRAPER LABORATORY

Sensory Stream Analysis Via Configurable Trigger Signature Detection

ActiveUS20140215235A1Optimum power conservationLow powerVolume/mass flow measurementBiological neural network modelsReconfigurable antennaGeneral purpose

The present inventors have recognized that proper utilization of reconfigurable event driven hardware may achieve optimum power conservation in energy constrained environments including a low power general purpose primary processor and one or more electronic sensors. Aspects of neurobiology and neuroscience, for example, may be utilized to provide such reconfigurable event driven hardware, thereby achieving energy-efficient continuous sensing and signature reporting in conjunction with the one or more electronic sensors while the primary processor enters a low power consumption mode. Such hardware is event driven and operates with extremely low energy requirements.

Owner:WISCONSIN ALUMNI RES FOUND

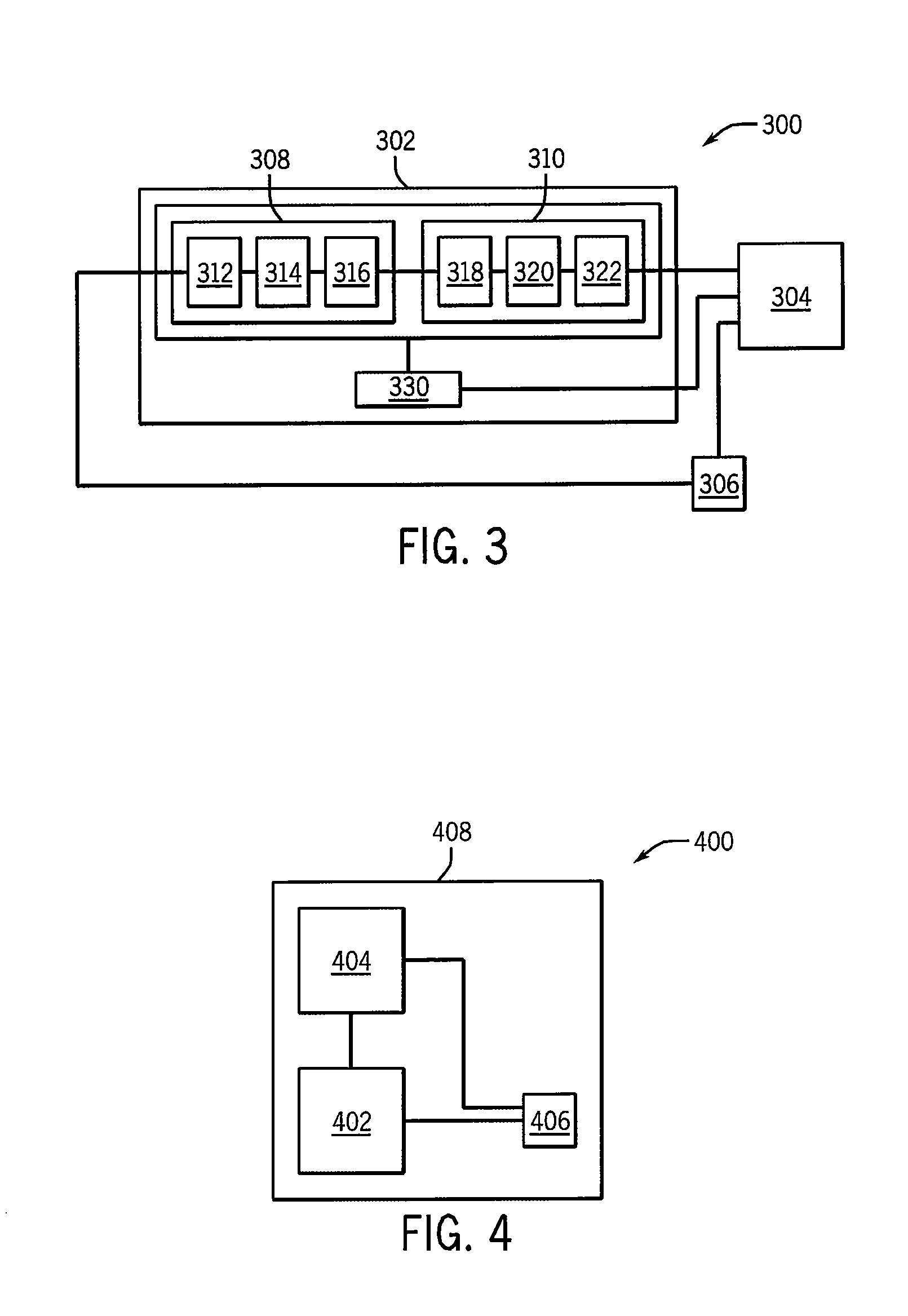

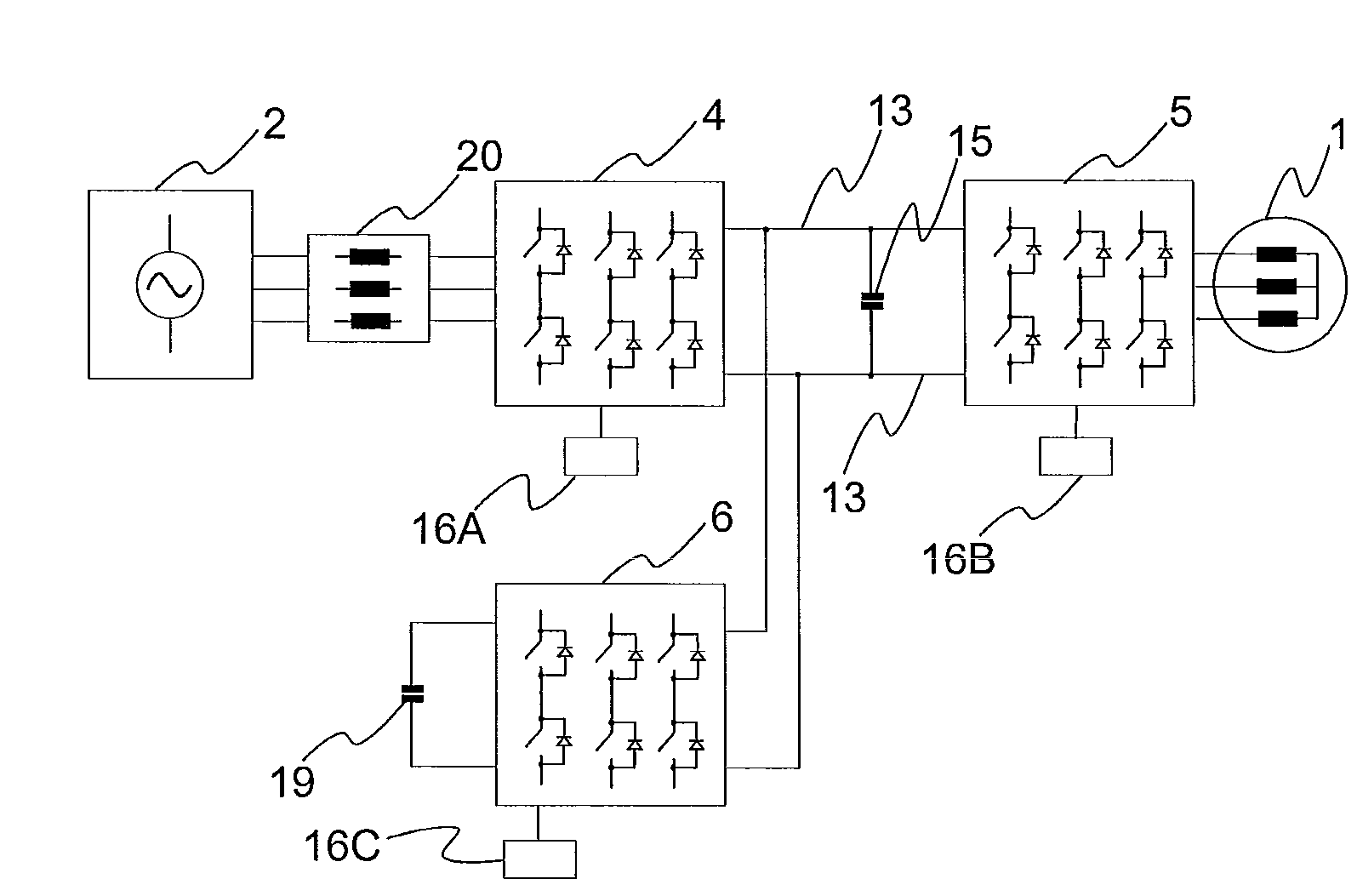

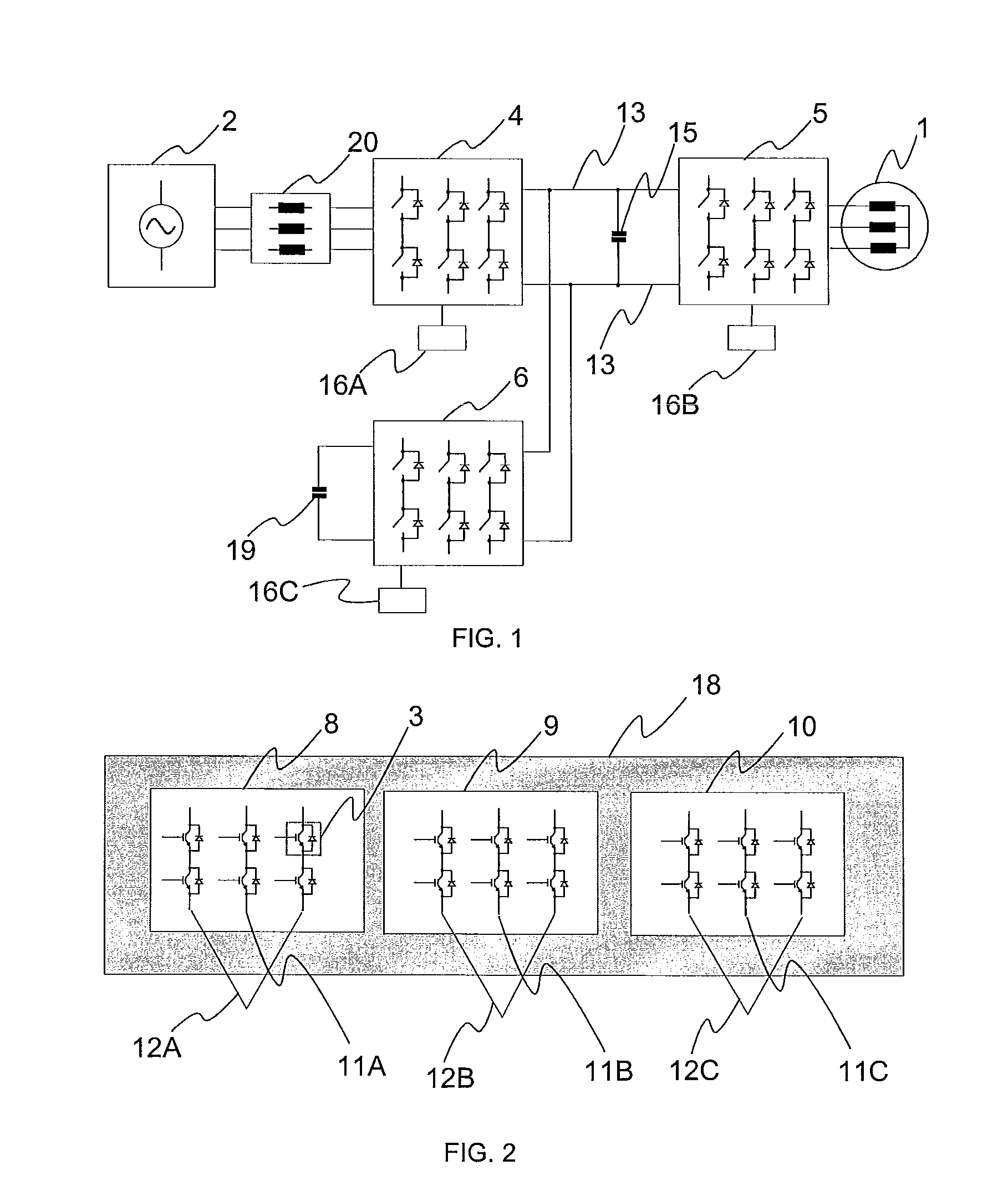

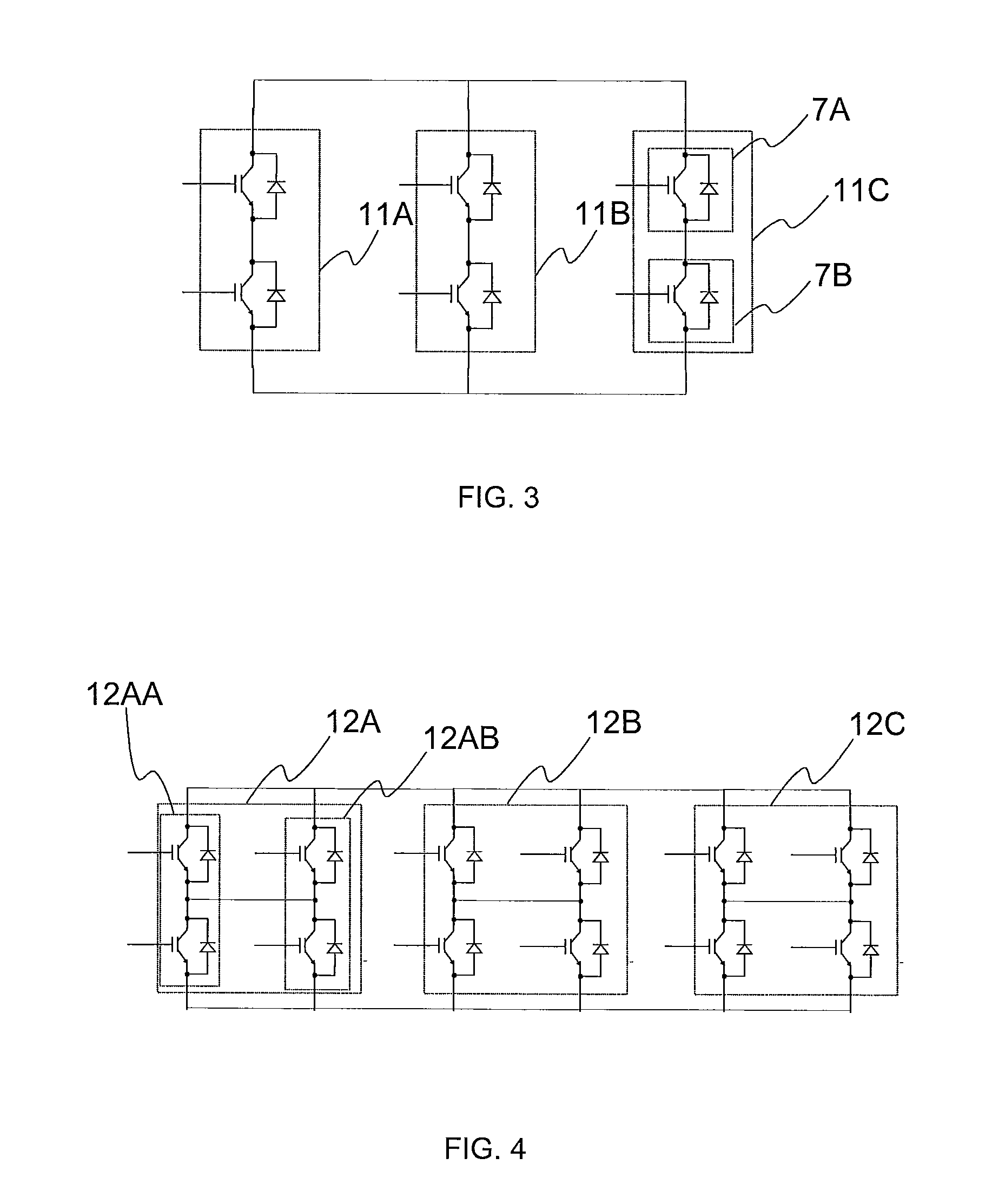

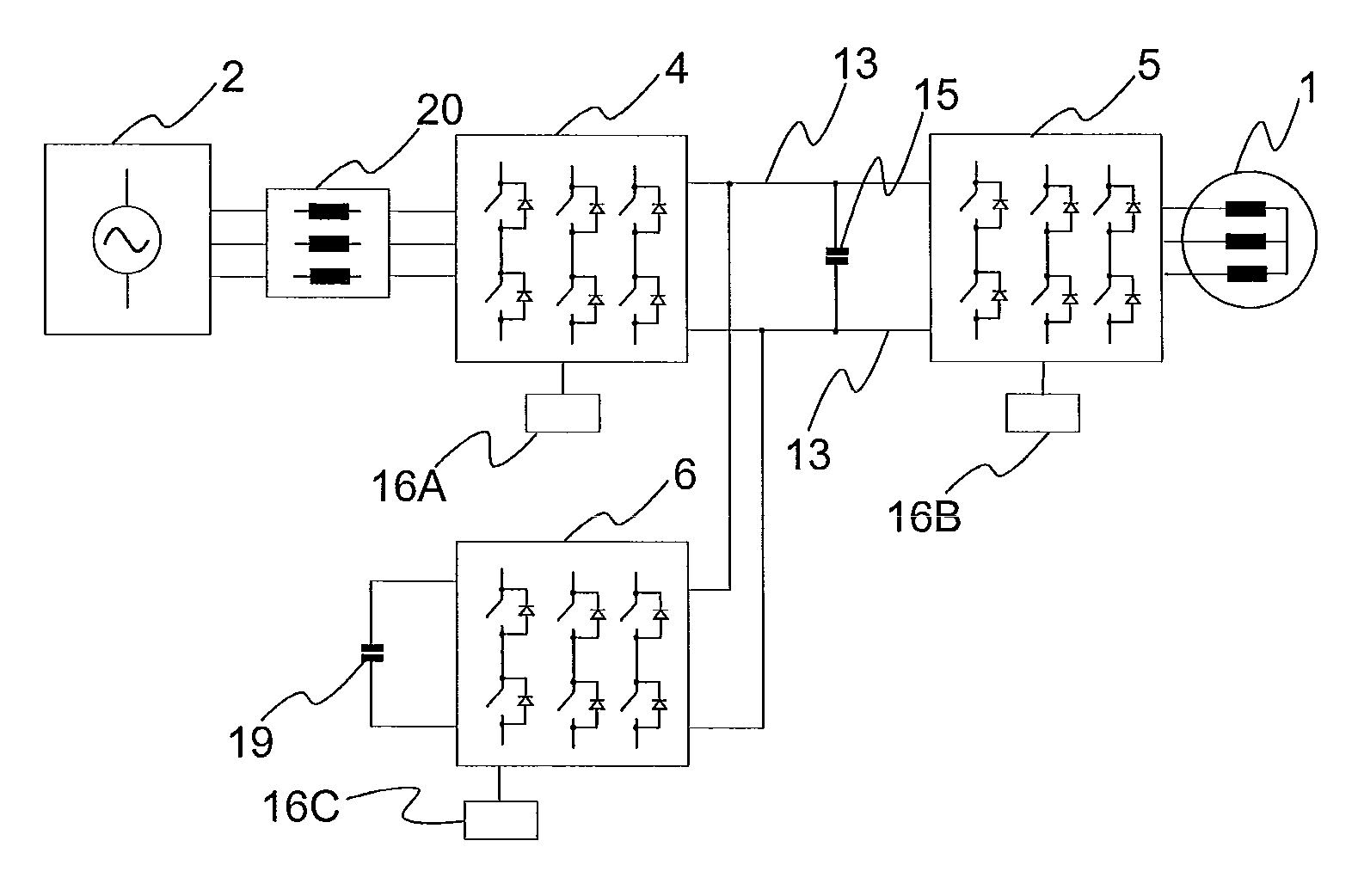

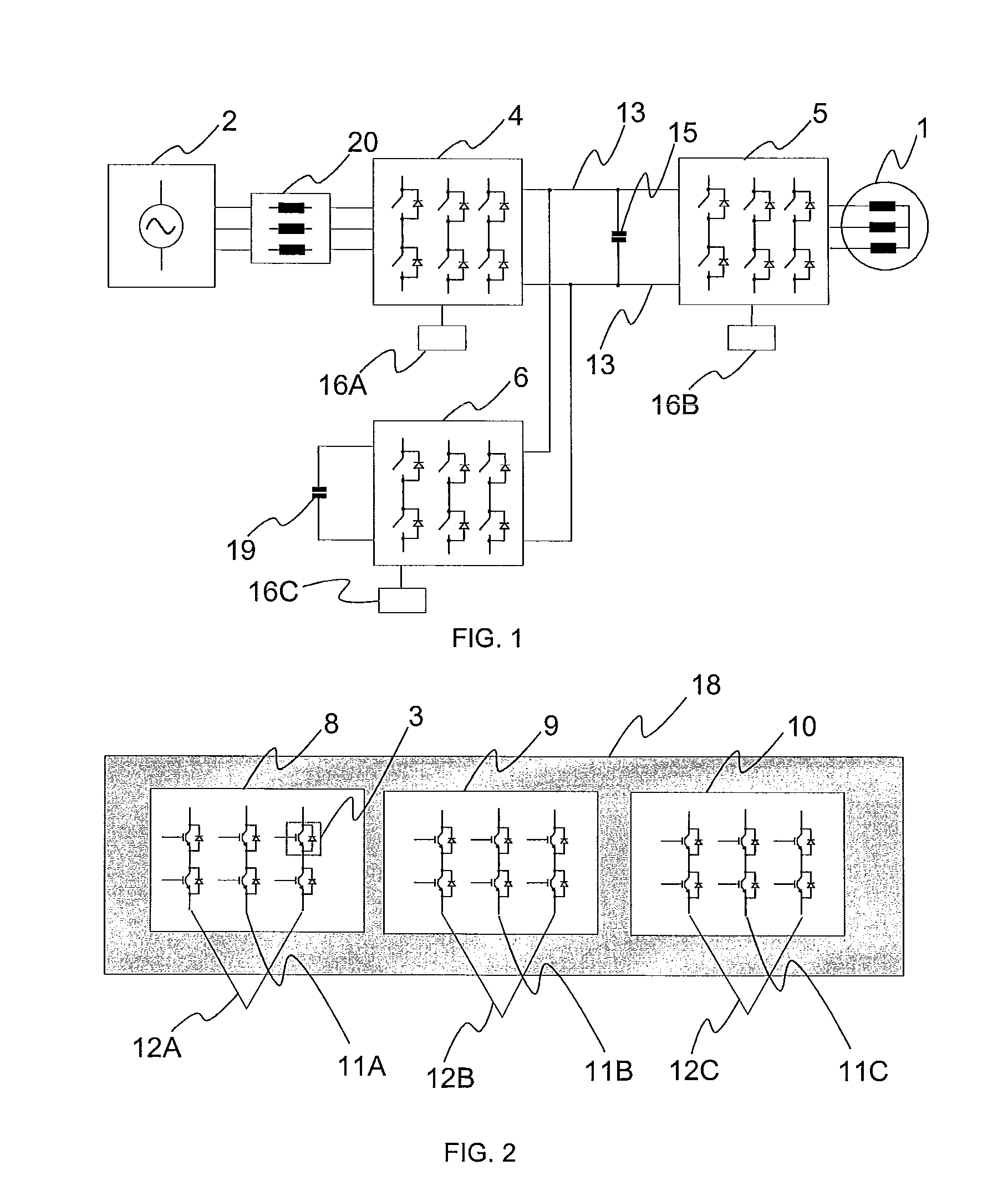

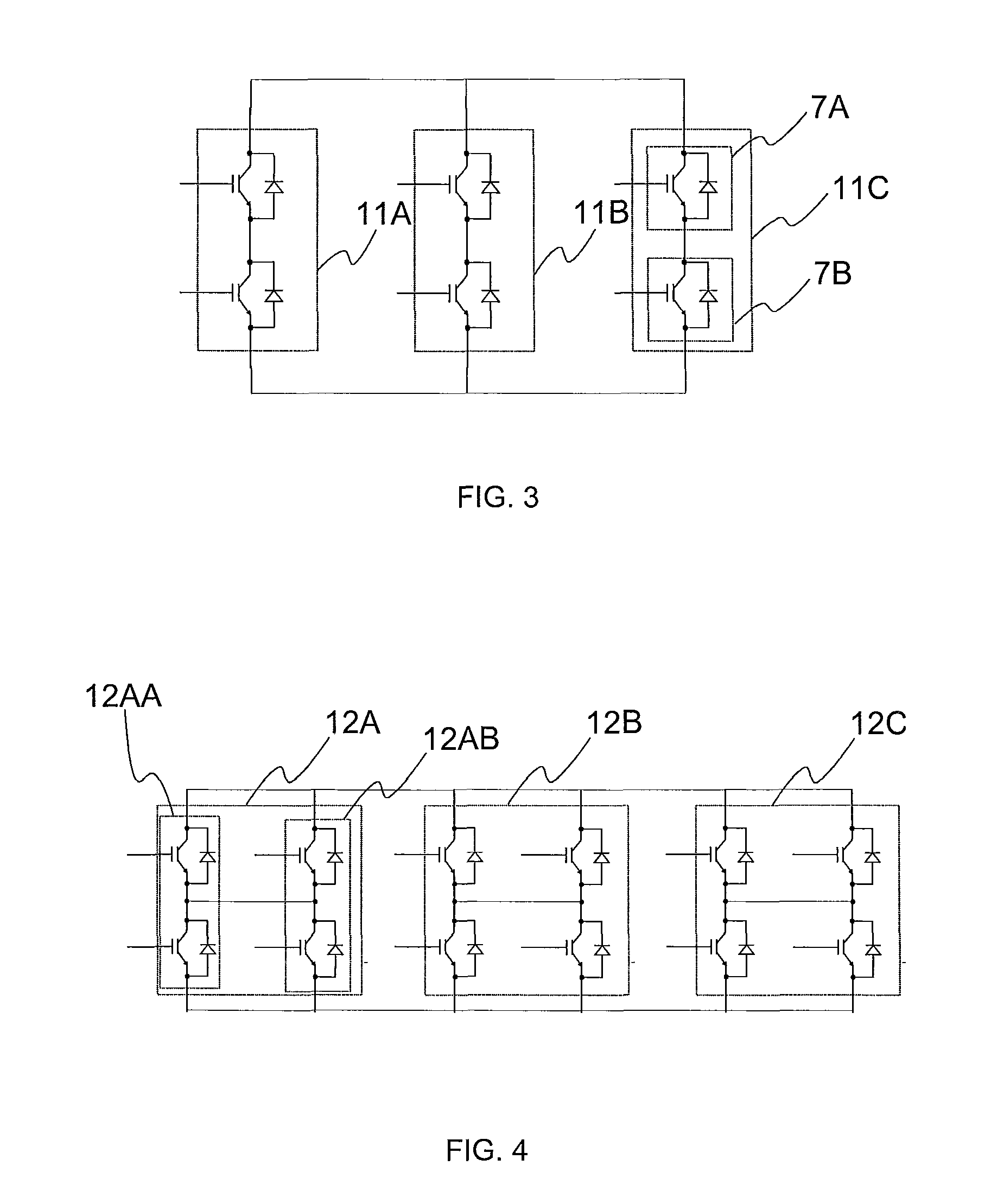

Apparatus and method for controlling the motor power

InactiveUS20090284079A1Increase power consumptionPower dissipationDc network circuit arrangementsAC motor controlElectric machineEngineering

The invention concerns a power control apparatus and a method for supplying power between an electric machine and an energy source. The power control apparatus contains at least two converters comprising a plurality of switches, at least some of which switches belong to a set of switch modules comprising a plurality of switches. In the method of the invention, a first set of switches belonging to at least two different modules and arranged to form a first converter is controlled by a first converter control, and a second set of switches arranged to form a second converter is controlled by a second converter control.

Owner:KONE CORP

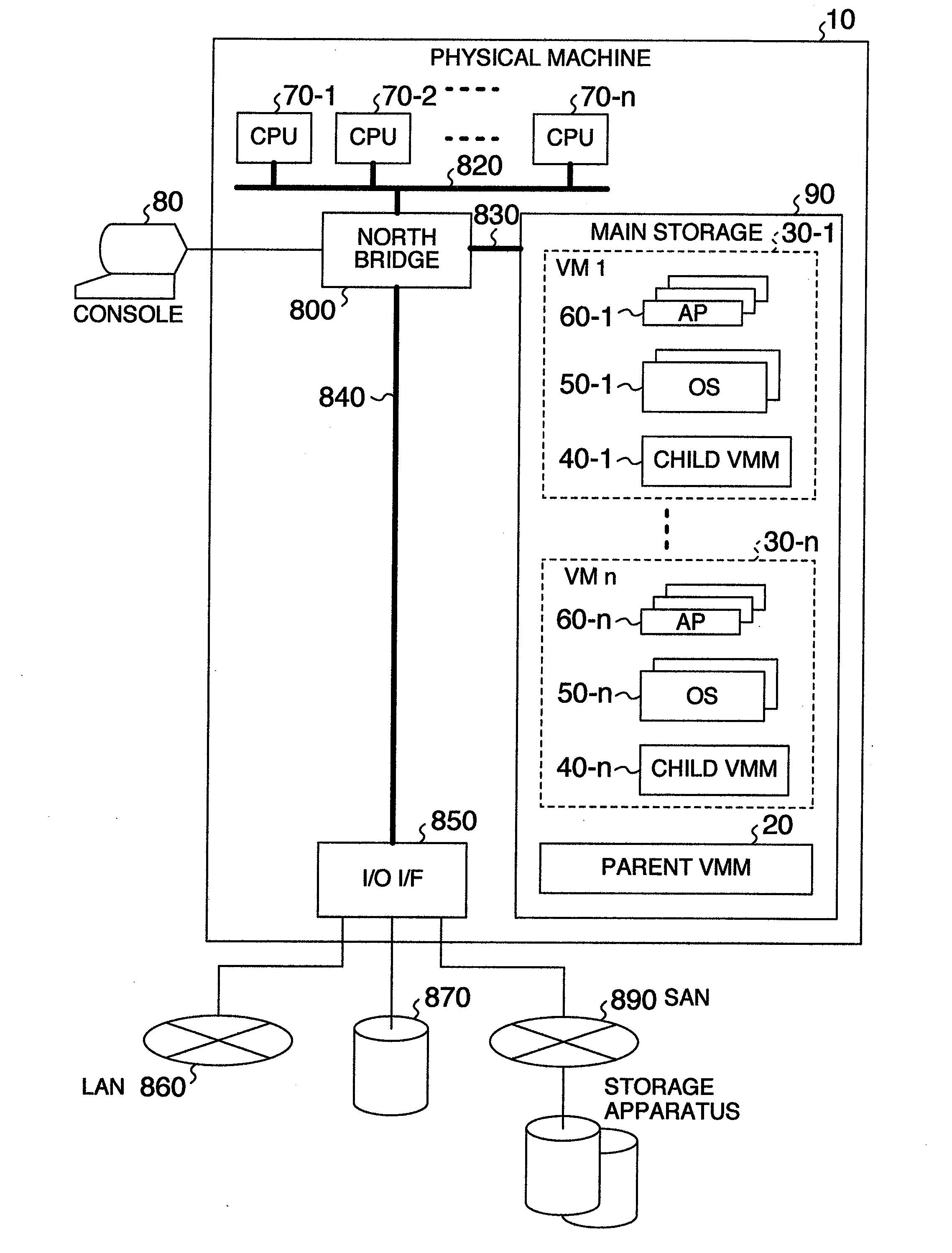

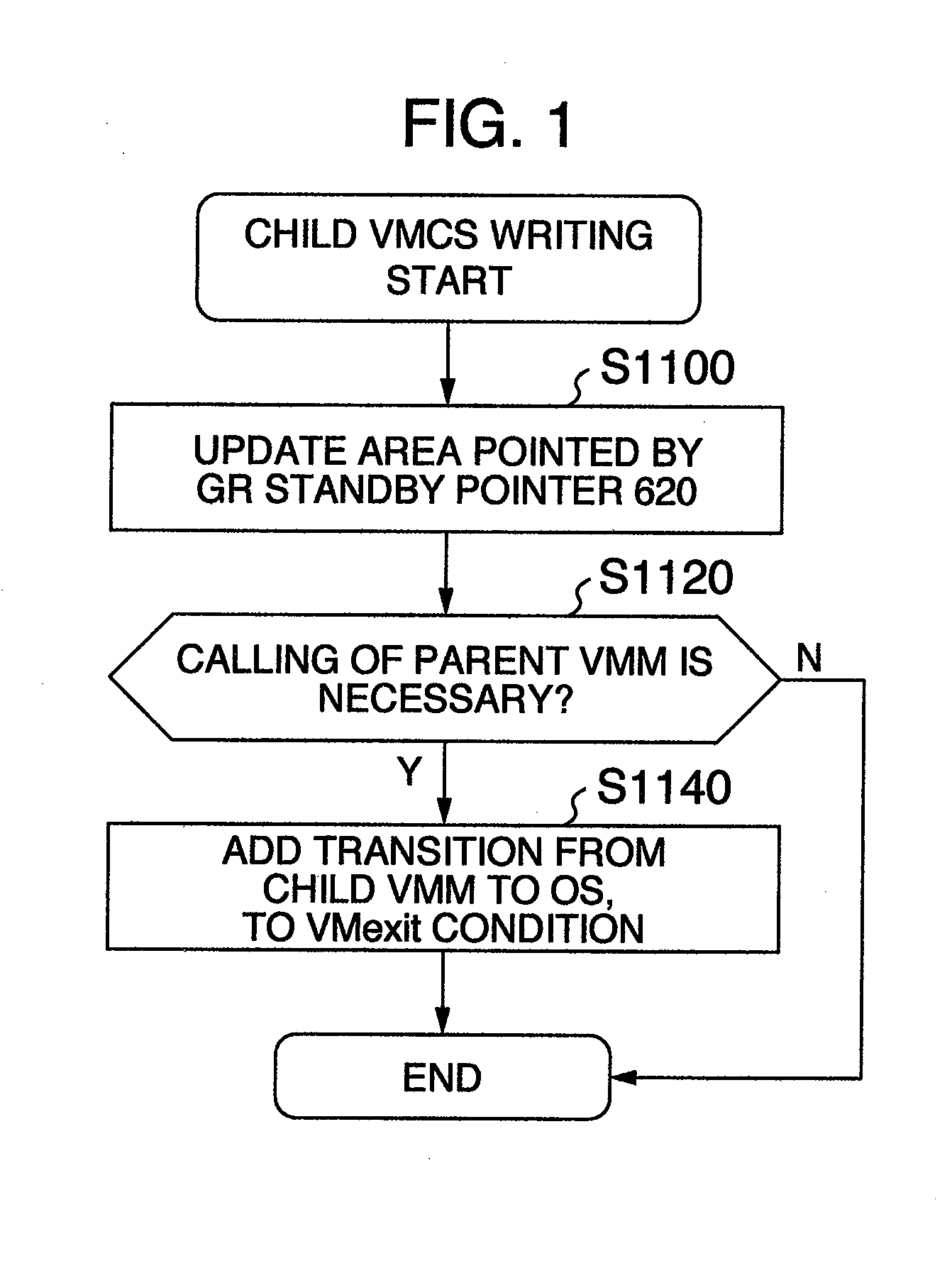

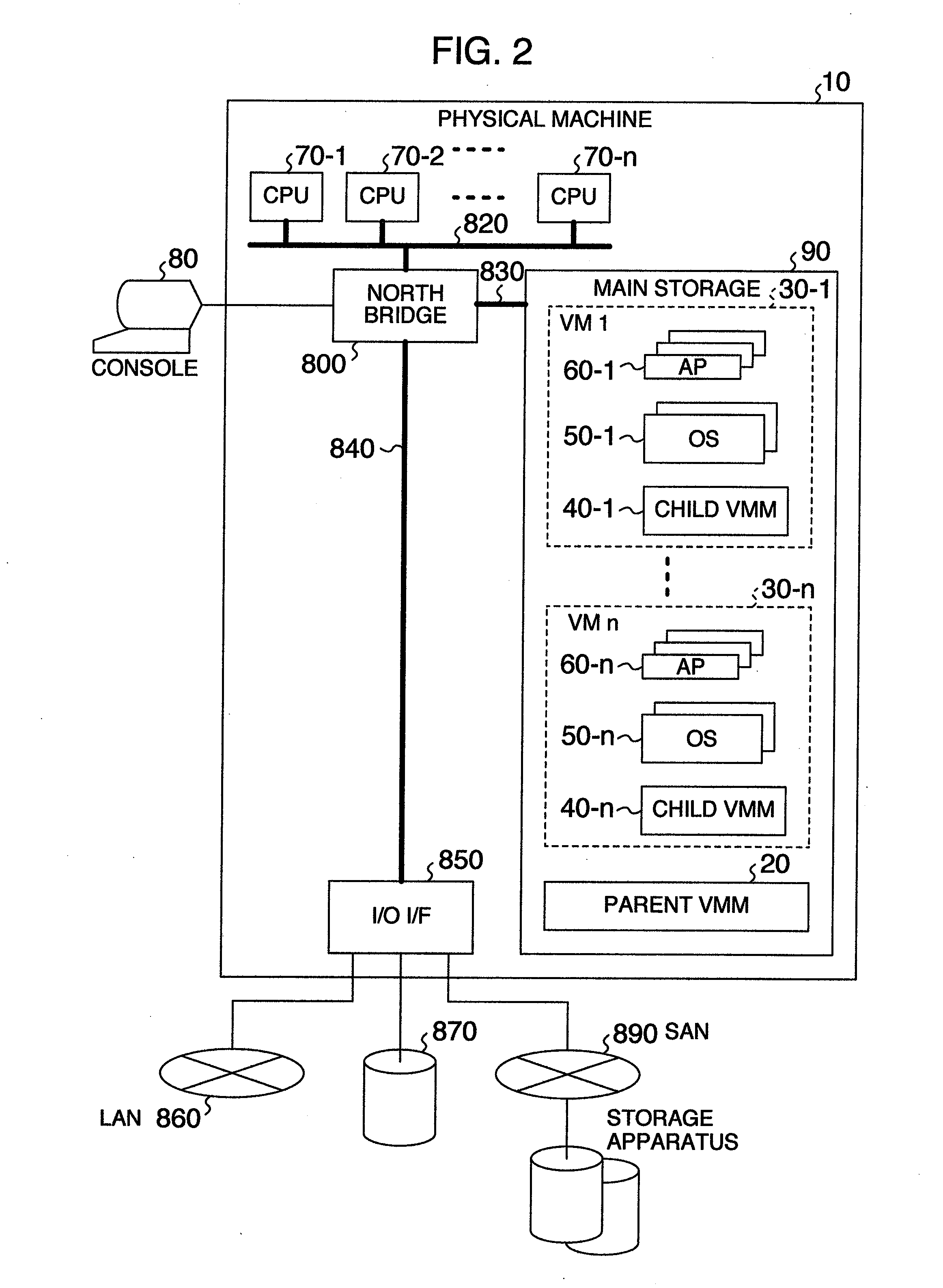

Virtual machine system and control method thereof

InactiveUS20100332722A1Increase the number ofPower dissipationComputer security arrangementsSoftware simulation/interpretation/emulationComputer scienceSemiconductor

In a two-level virtual machine system having child VMMs operating on a parent VMM, the field update frequency of VMCS and VMCB which control a VMM assist function of a CPU is not uniform. A G field requiring reflection of emulation results is higher in update frequency than a C field. The semiconductor quantity and power dissipation caused by the assist function expansion tend to increase in the C field used for a condition decision as compared with the G field simply retaining a value because influence upon the CPU operation is greater in the C field. Therefore, events relating to the G field which is high in update frequency and less in increase of semiconductor quantity and power dissipation caused by the assist function expansion are coped with by the CPU with its assist function expanded. Events relating to the C field are coped with by the parent VMM.

Owner:HITACHI LTD

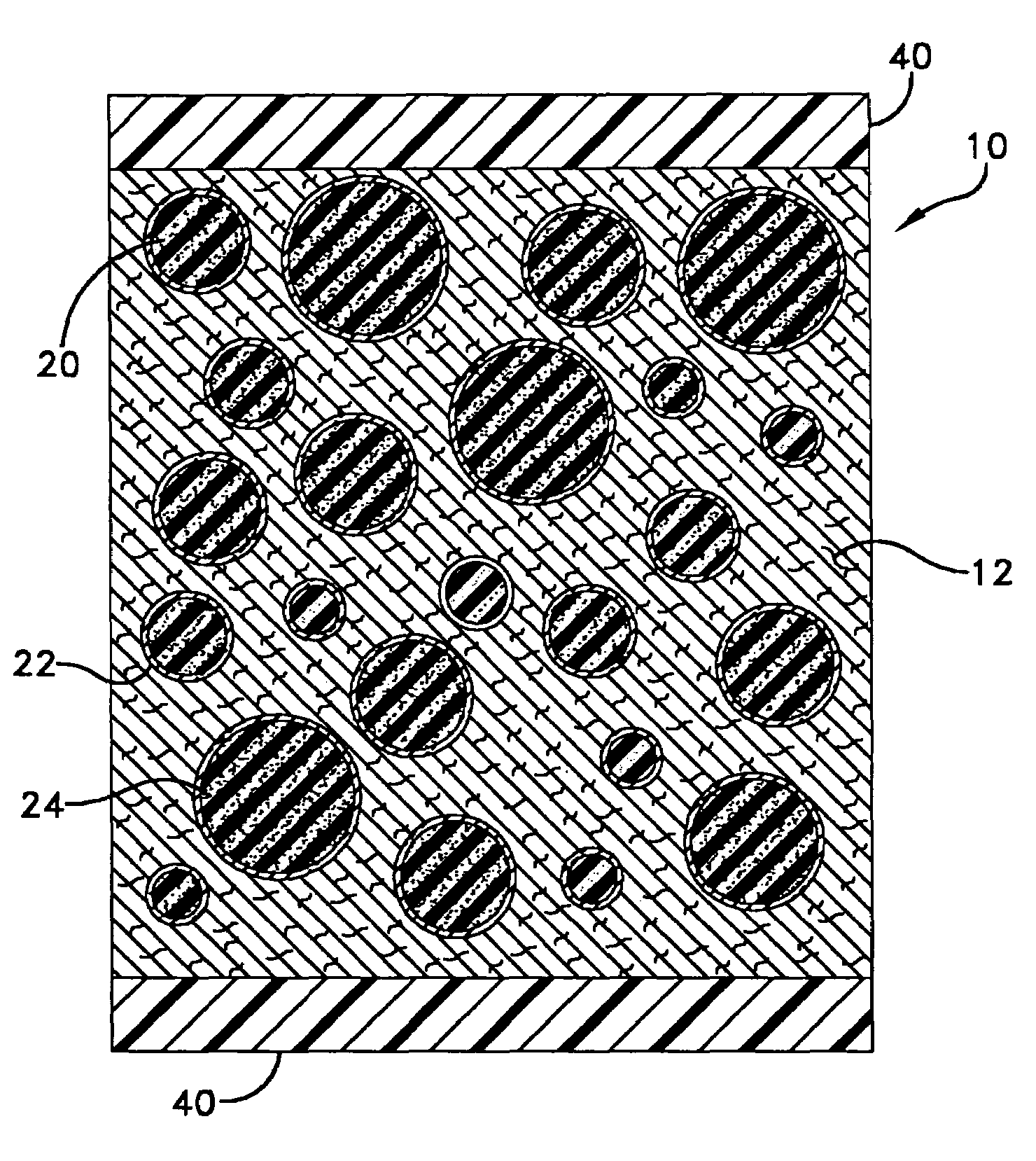

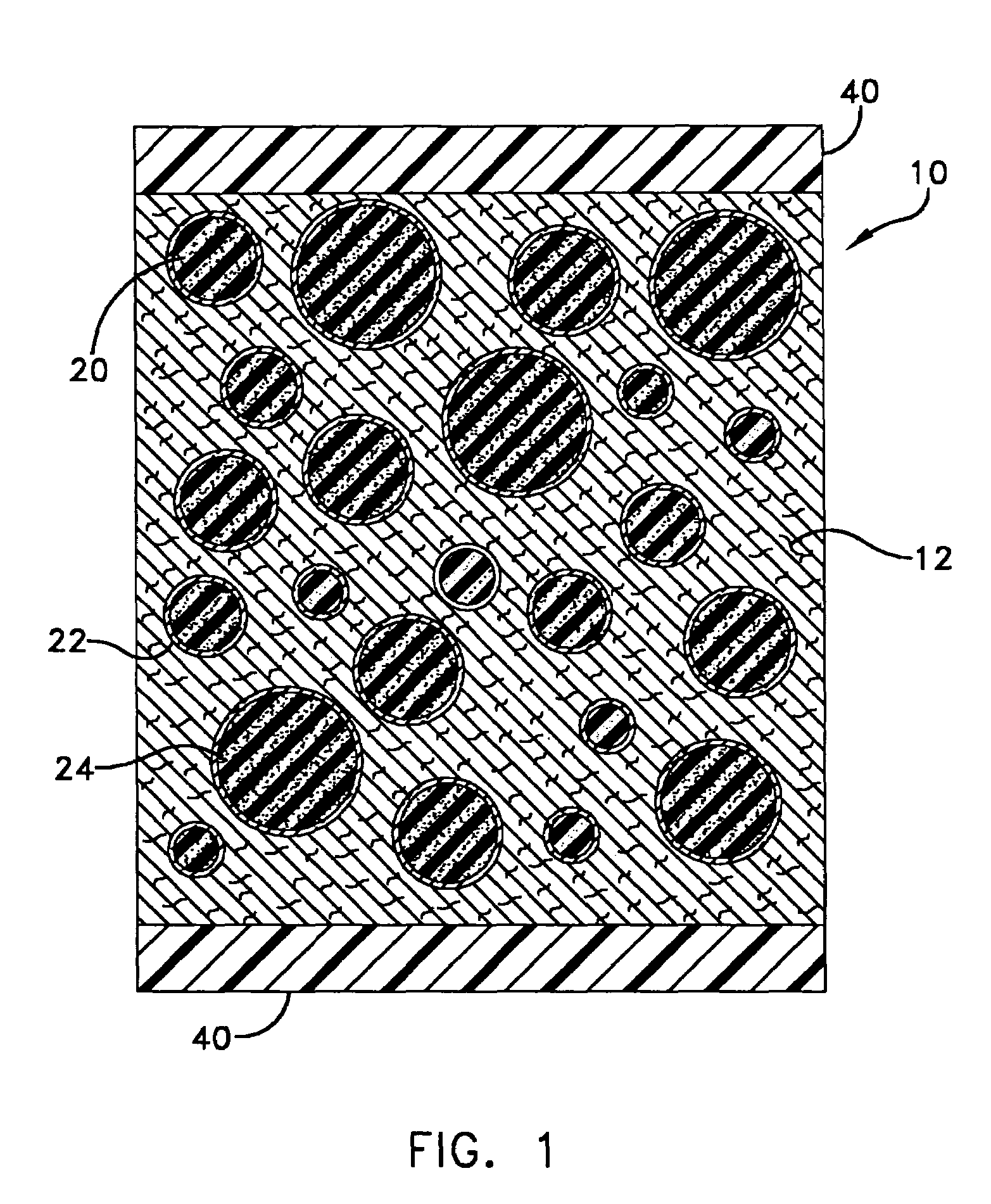

Pressure resistant anechoic coating for undersea platforms

InactiveUS7205043B1Resistant to deteriorationSmall wall thicknessCeilingsSynthetic resin layered productsOcean bottomCoating

A composite material containing inclusions of spherical shells in which each spherical shell encapsulates a rubber core with ferrite loading. The inclusions are embedded in a matrix material of syntactic foam. The spherical shells are made from glass and therefore acoustically transparent and in combination with the cores are statically stiffer than the surrounding matrix material. The composite material with the matrix material and inclusions allows the composite material to be acoustically dissipating with a stiffness in which the energy of forces associated with undersea platforms is resisted.

Owner:THE UNITED STATES OF AMERICA AS REPRESENTED BY THE SECRETARY OF THE NAVY

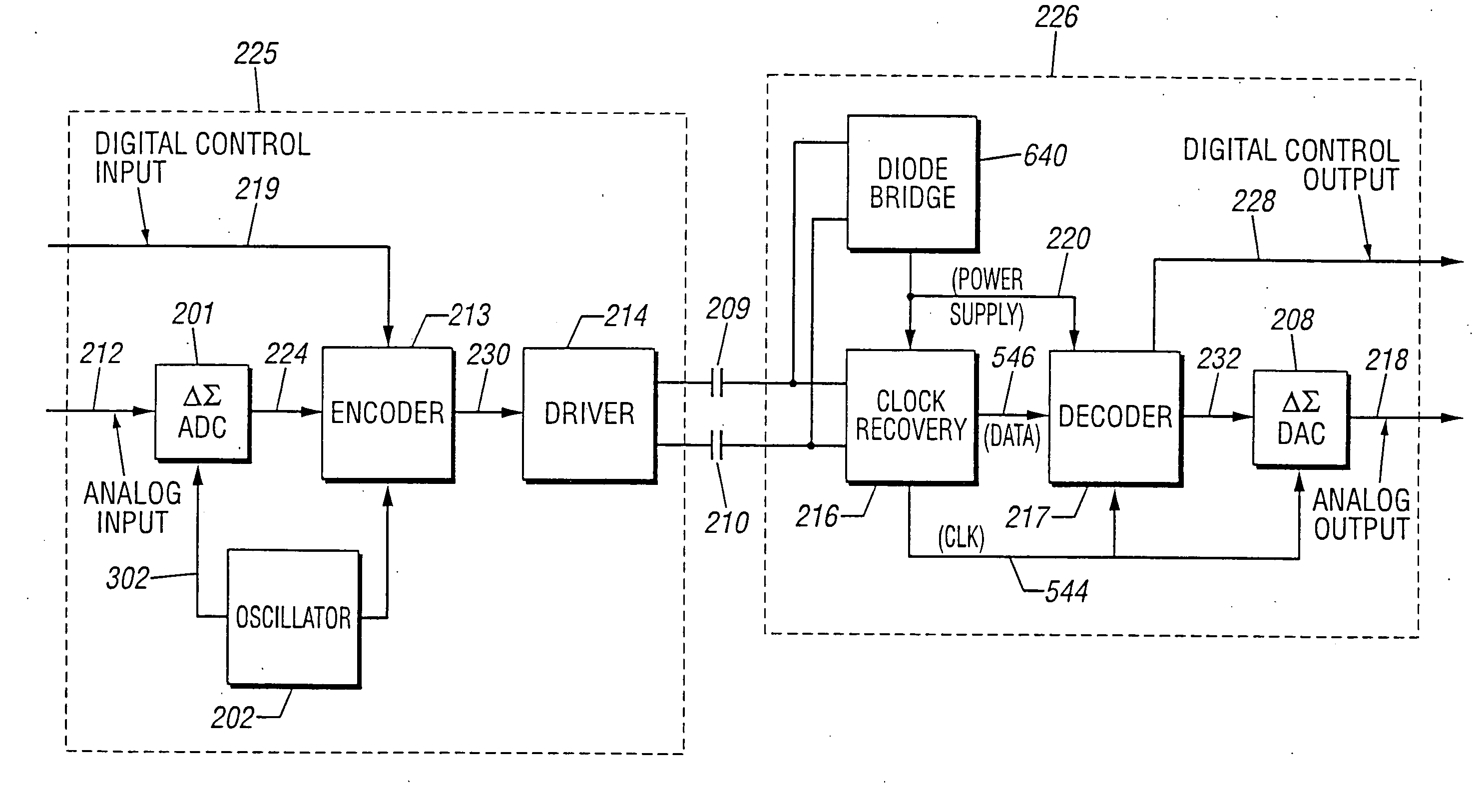

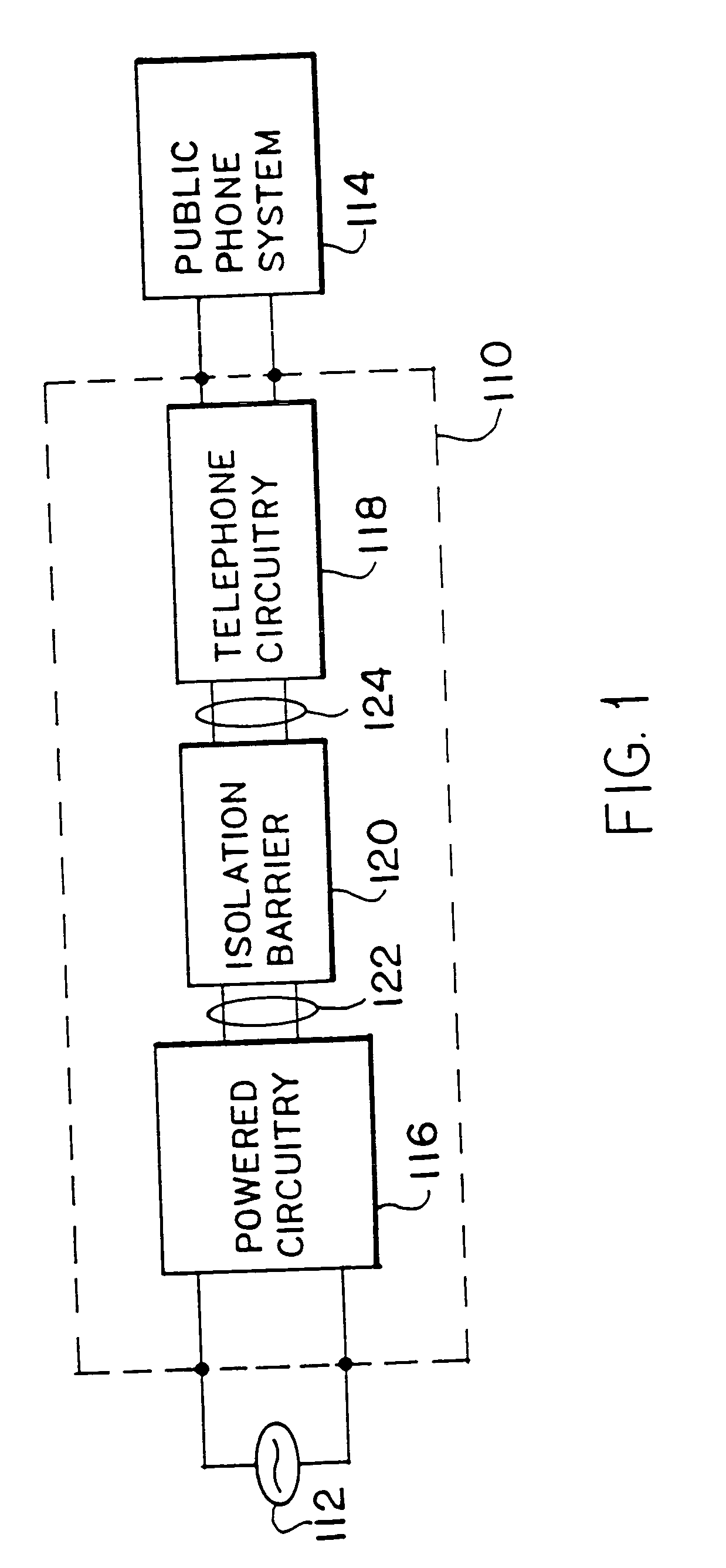

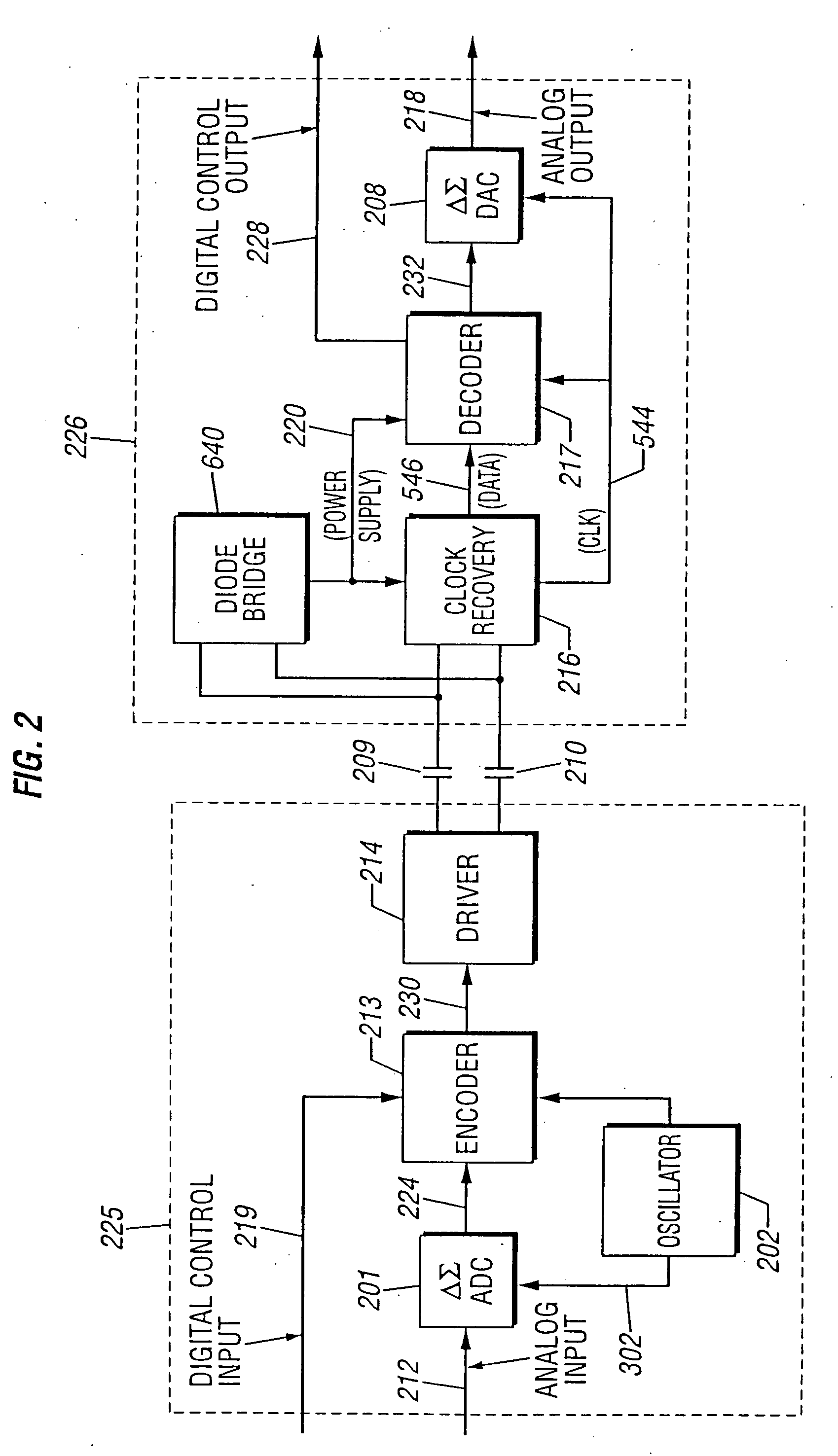

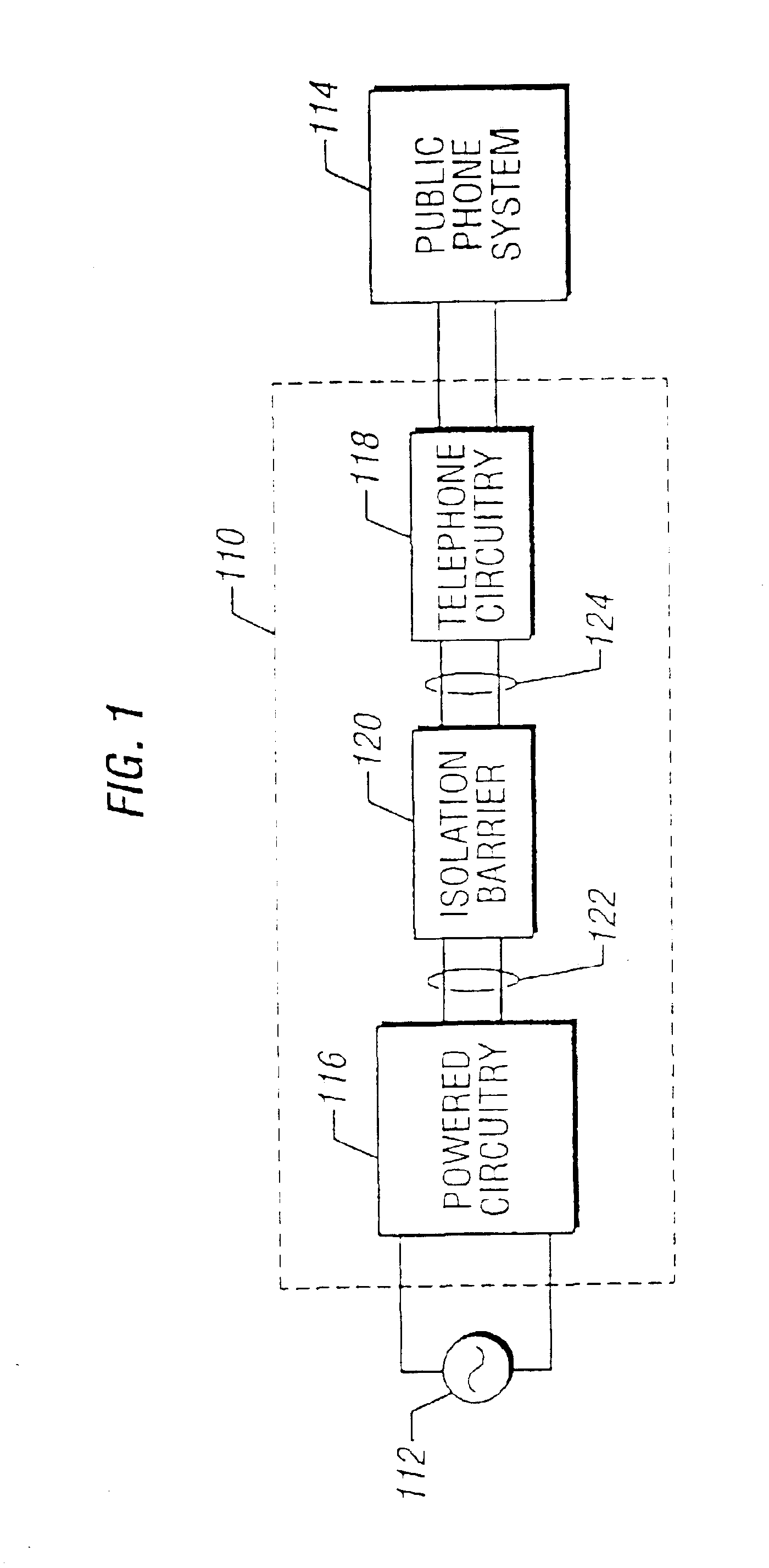

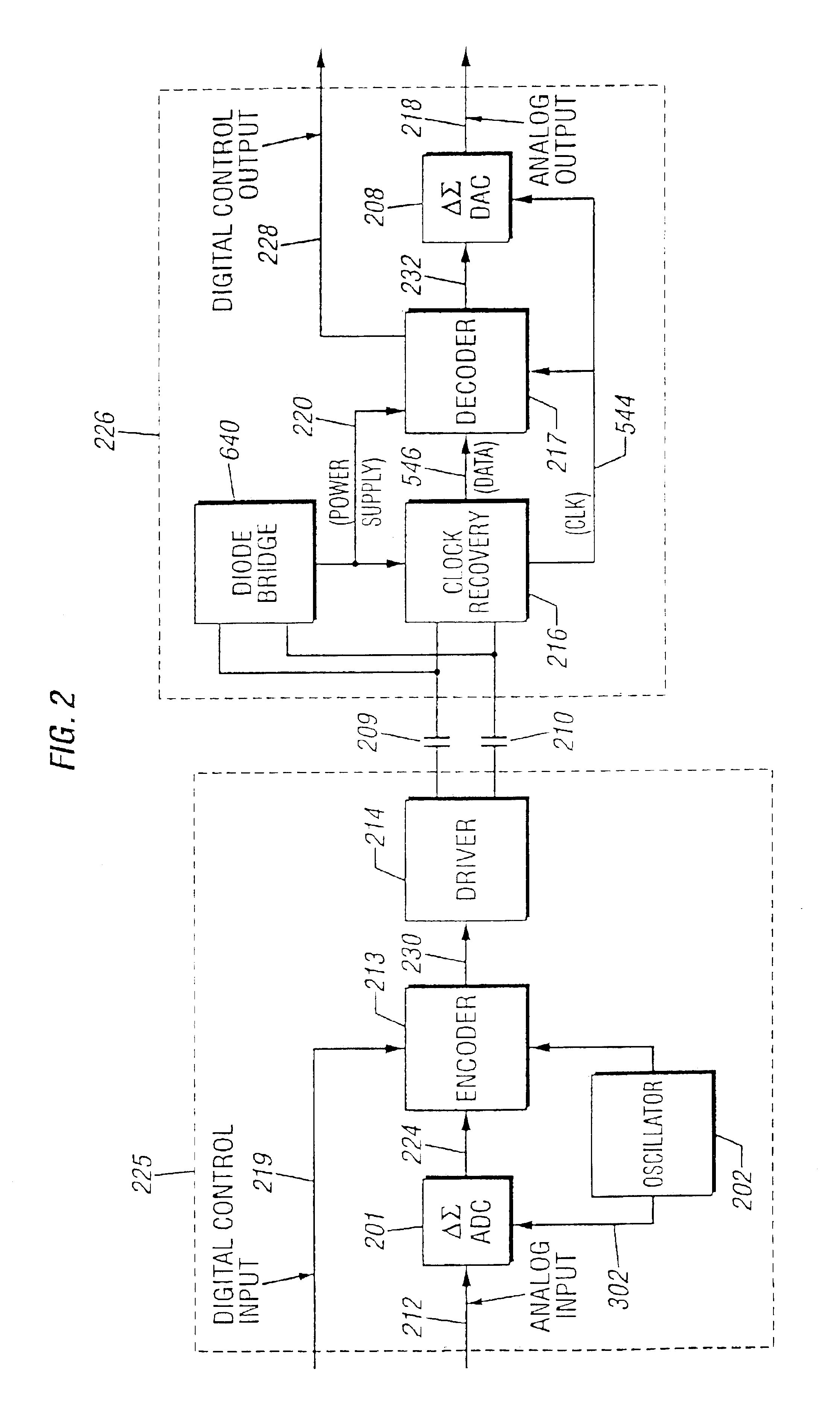

Digital access arrangement circuitry and method for connecting to phone lines having a DC holding circuit with programmable current limiting

InactiveUS20050100104A1Reduce power consumptionPower dissipationInterconnection arrangementsDc level restoring means or bias distort correctionCapacitanceCurrent limiting

A digital direct access arrangement (DAA) circuitry may be used to terminate the telephone connections at the user's end that provides a communication path for signals to and from the phone lines. Briefly described, the DAA provides a programmable means for the DC termination for a variety of international phone standards. The invention may also be utilized with means for transmitting and receiving a signal across a capacitive isolation barrier. More particularly, a DC holding circuit is provided in which a programmable DC current limiting mode is available. In the current limiting mode, power may be dissipated in devices external to a DAA integrated circuit. Moreover, much of the power may be dissipated in external passive devices, such as resistors.

Owner:SILICON LAB INC

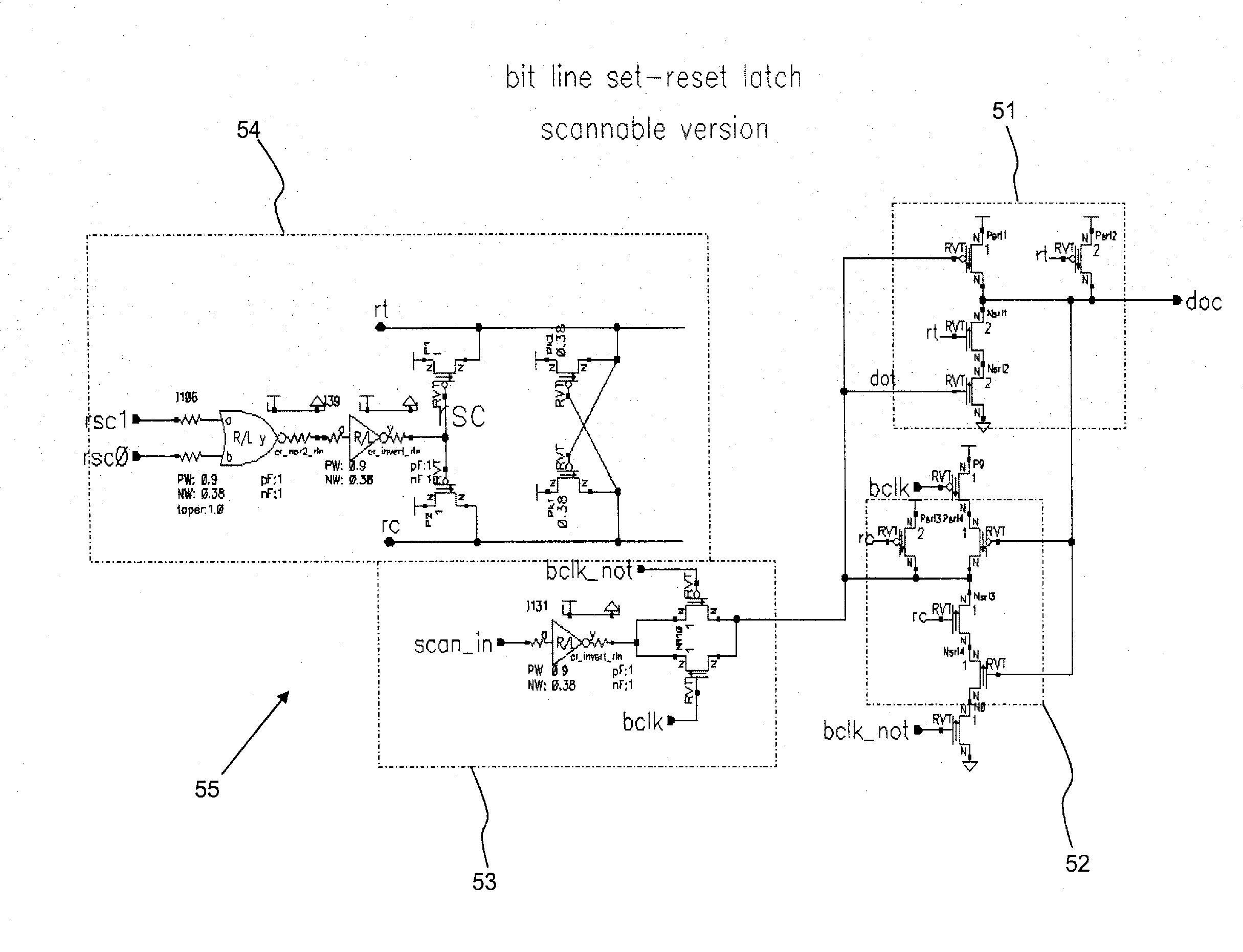

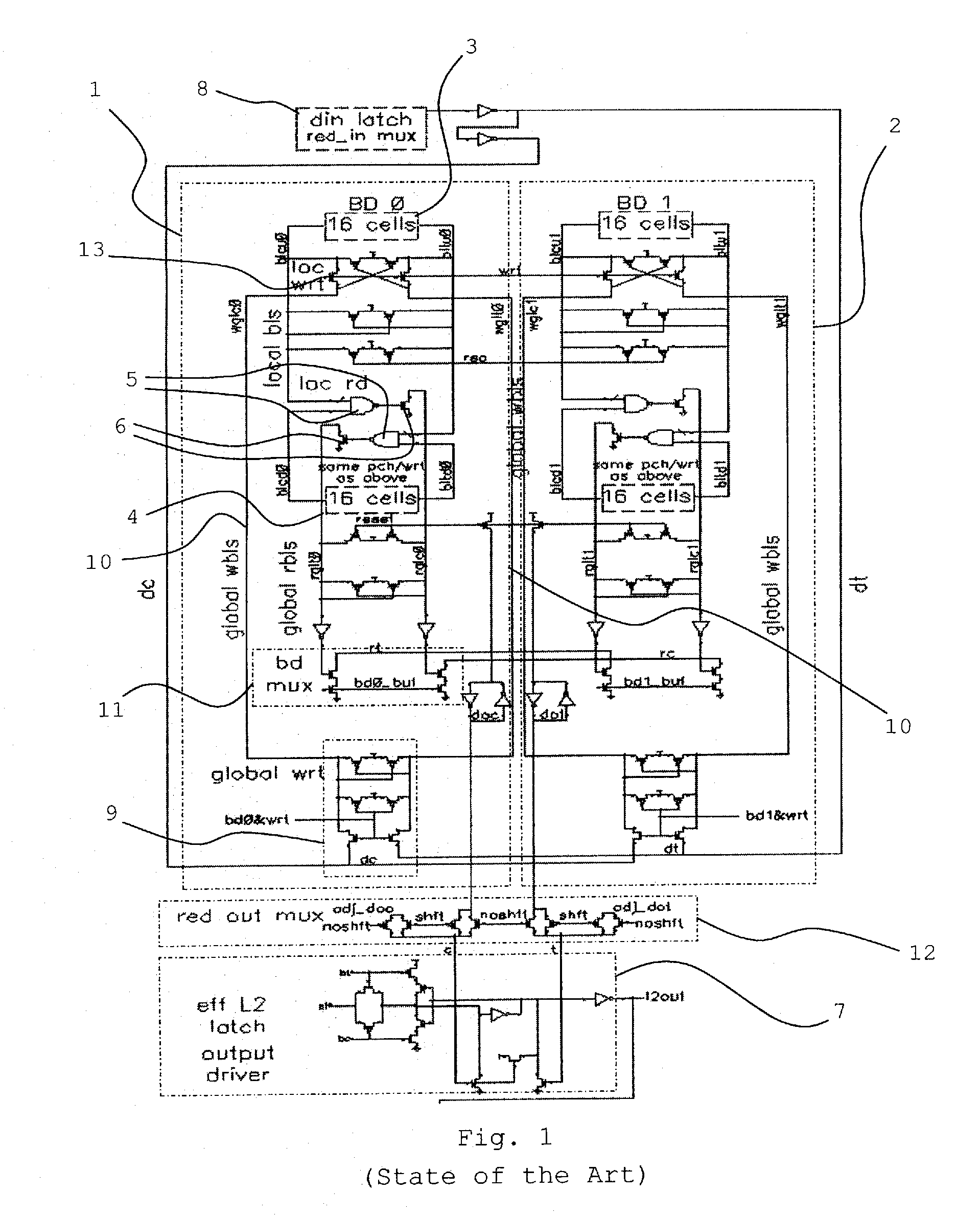

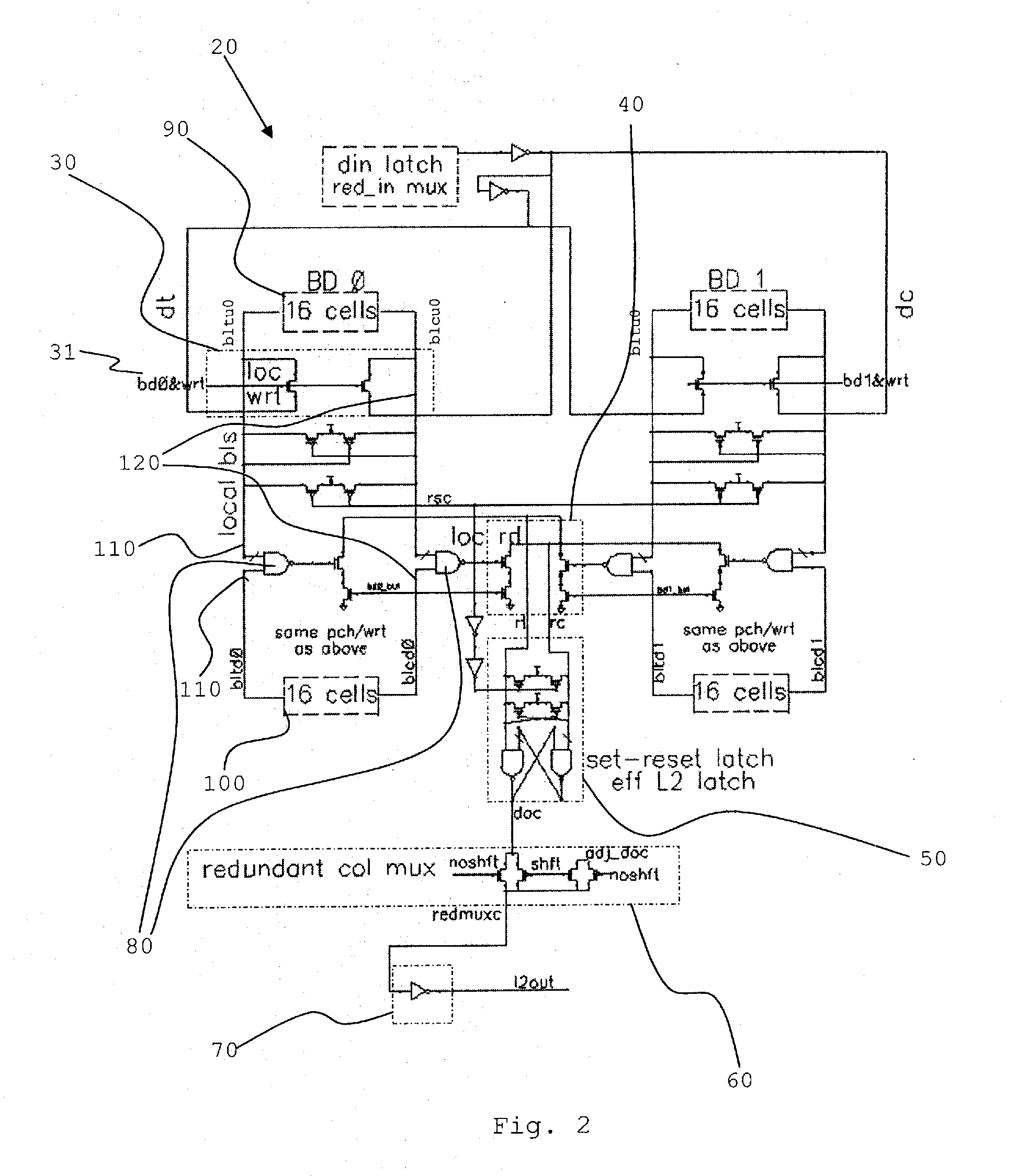

Method and structure for domino read bit line and set reset latch

A domino read bit line structure (20) integral to an SRAM array (1, 2) with thirty-two word lines or less to access SRAM cells divided into two groups (3, 4, 90, 100) is described. The bit line structure (20) includes a dynamic bit decode multiplexer (11, 40) and two NAND circuits (5, 80) used to combine the two groups (3, 4, 90, 100), wherein in order to reduce power consumption the two NANDS (80) drive the dynamic bit decode multiplexer (40) directly, such that true and complement dynamic outputs (rt, rc) drive a set-reset latch (50) to convert the dynamic outputs (rt, rc) to a single static signal (doc), wherein the output of the set-reset latch (50) is already static so that the set-reset latch (50) acts as an effective array output latch (7).

Owner:IBM CORP

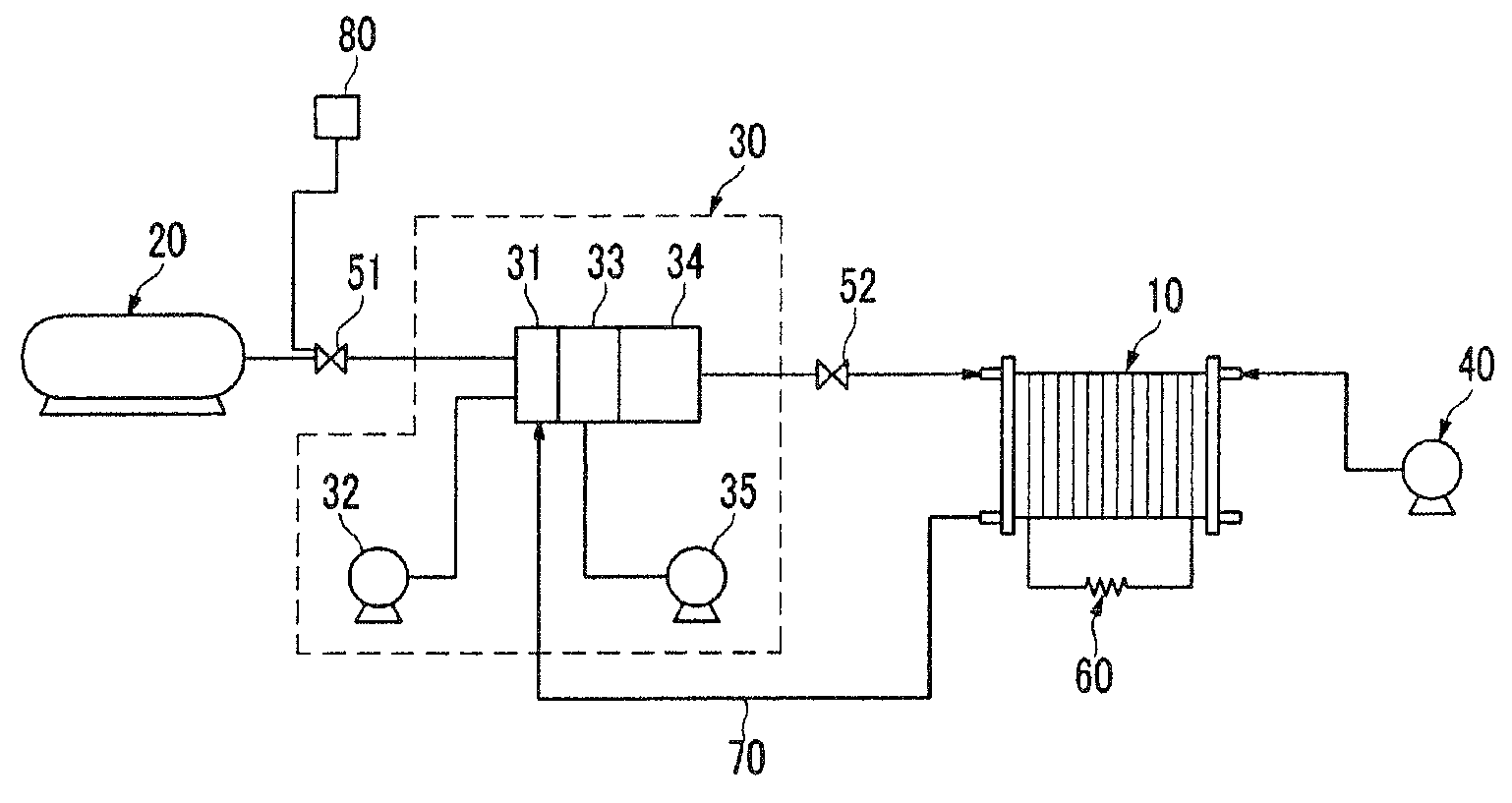

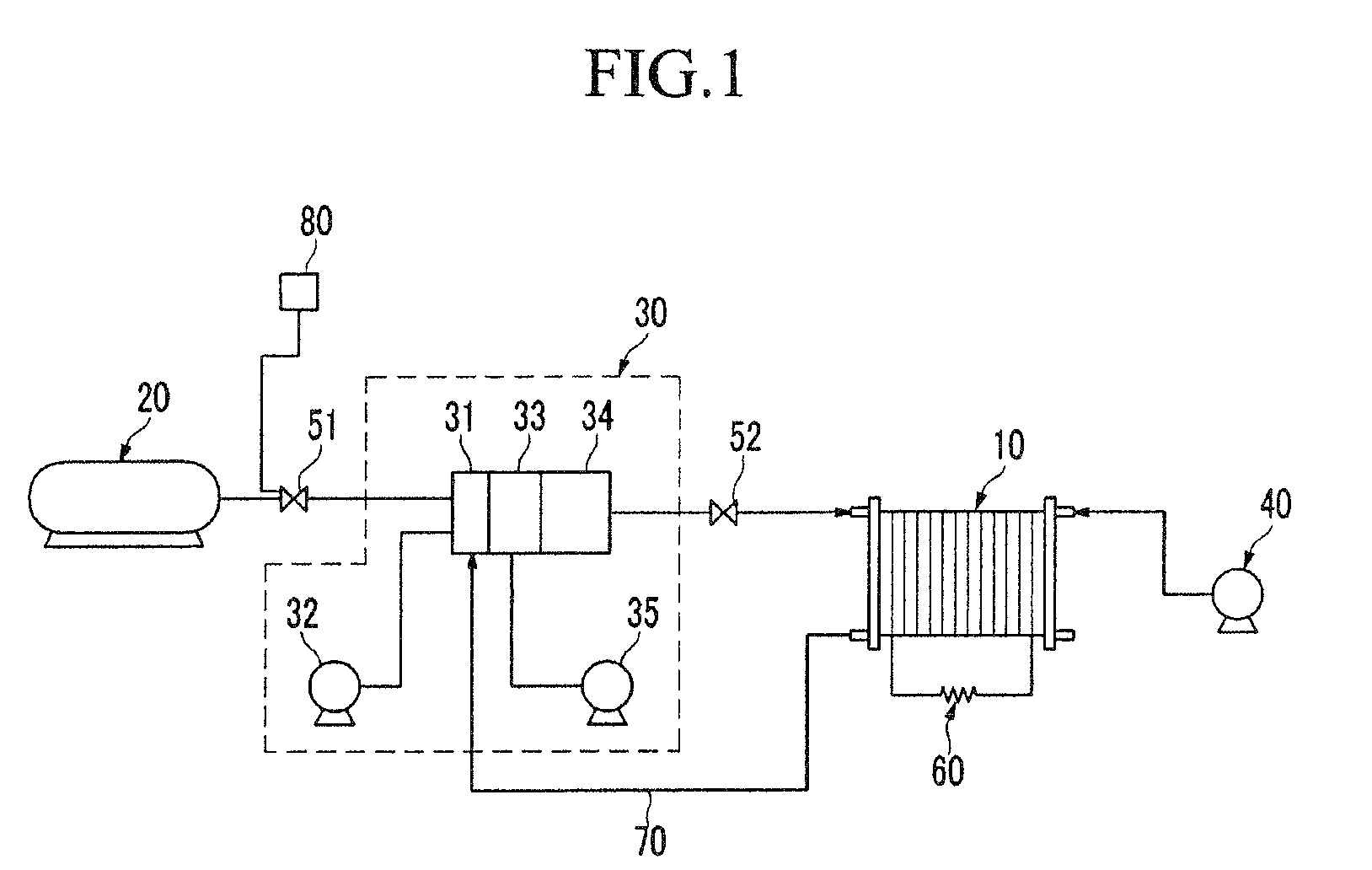

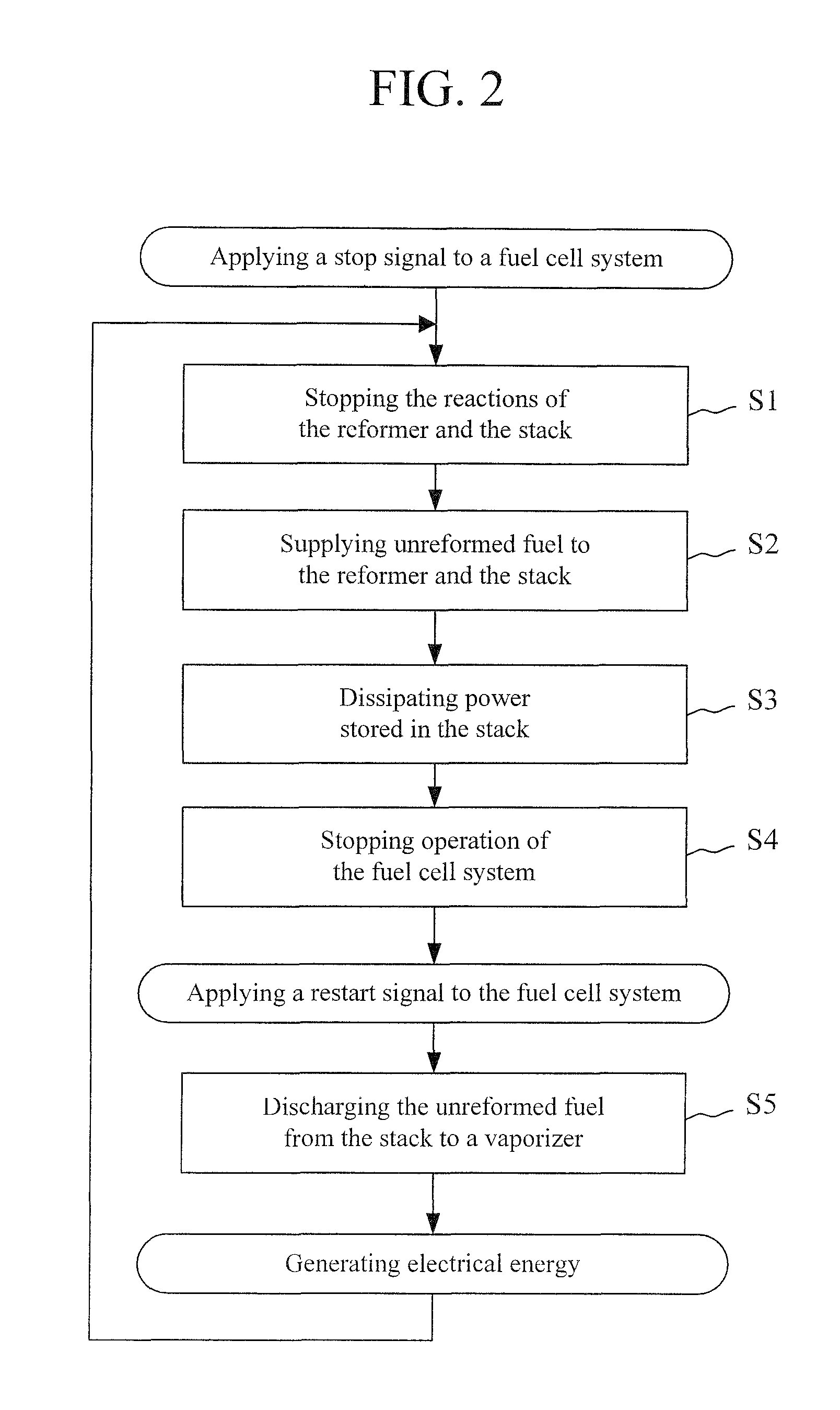

Fuel cell system and method for operating the same

InactiveUS8173310B2Promote recoveryAvoid reactionFuel cell auxillariesElectrochemical responseHydrogen

A fuel cell system and a method for operating the same are disclosed. In one embodiment, a fuel cell system includes a fuel supplier, a reformer for reforming a fuel supplied from the fuel supplier into hydrogen gas by a reforming reaction, and a fuel cell stack for generating electrical energy by an electrochemical reaction between the hydrogen gas and an oxidizing agent. When the fuel cell system is to be stopped, the reforming reaction of the reformer and the electrochemical reaction of the fuel cell are stopped and a portion of unreformed fuel is fed to the reformer and the fuel cell stack. Residual hydrogen is reacted and residual power from the fuel cell stack is dissipated by a power dissipation circuit. By largely removing hydrogen from the fuel cell stack on a stopped condition, reactions that are detrimental to the fuel cell membrane are reduced.

Owner:SAMSUNG SDI CO LTD

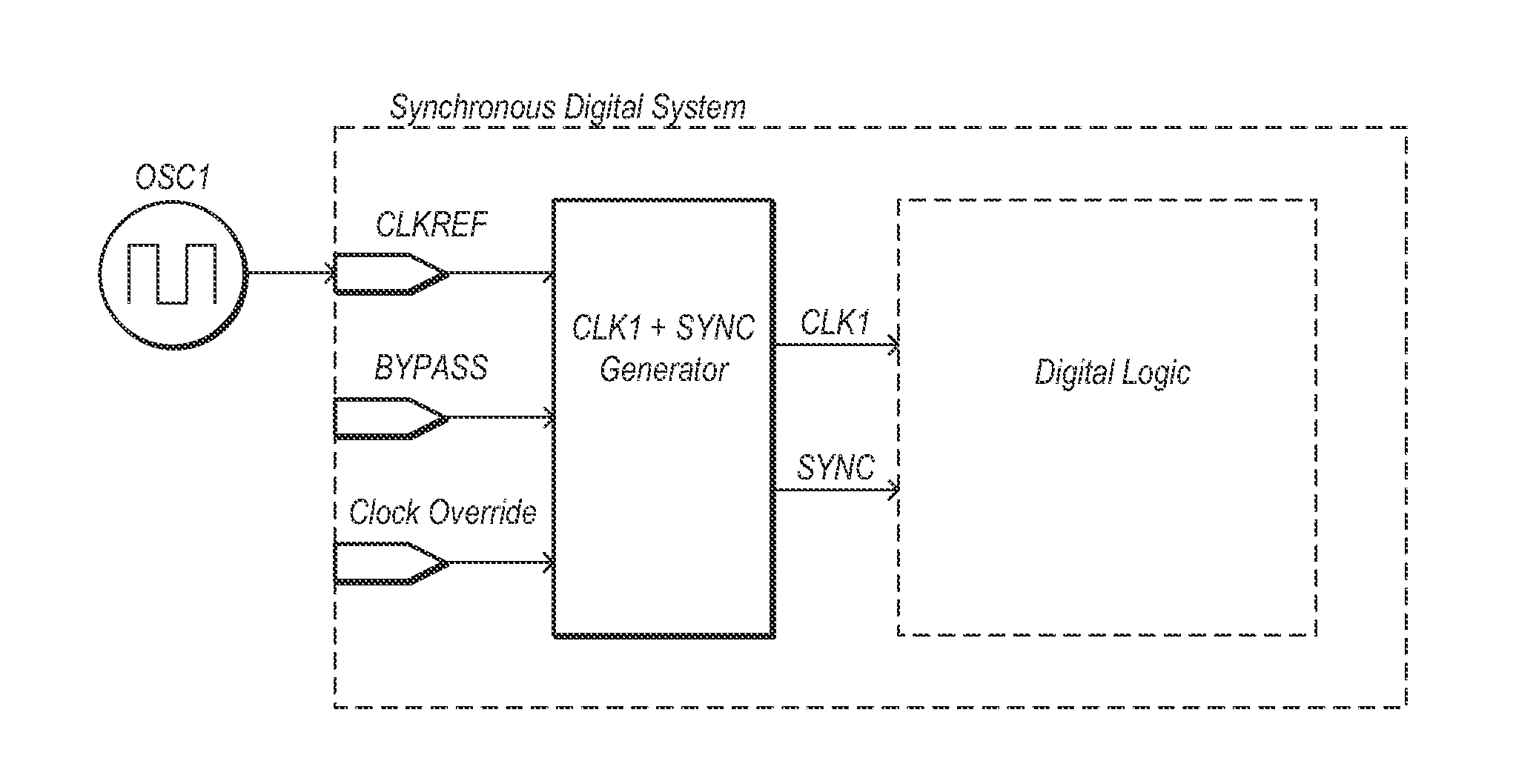

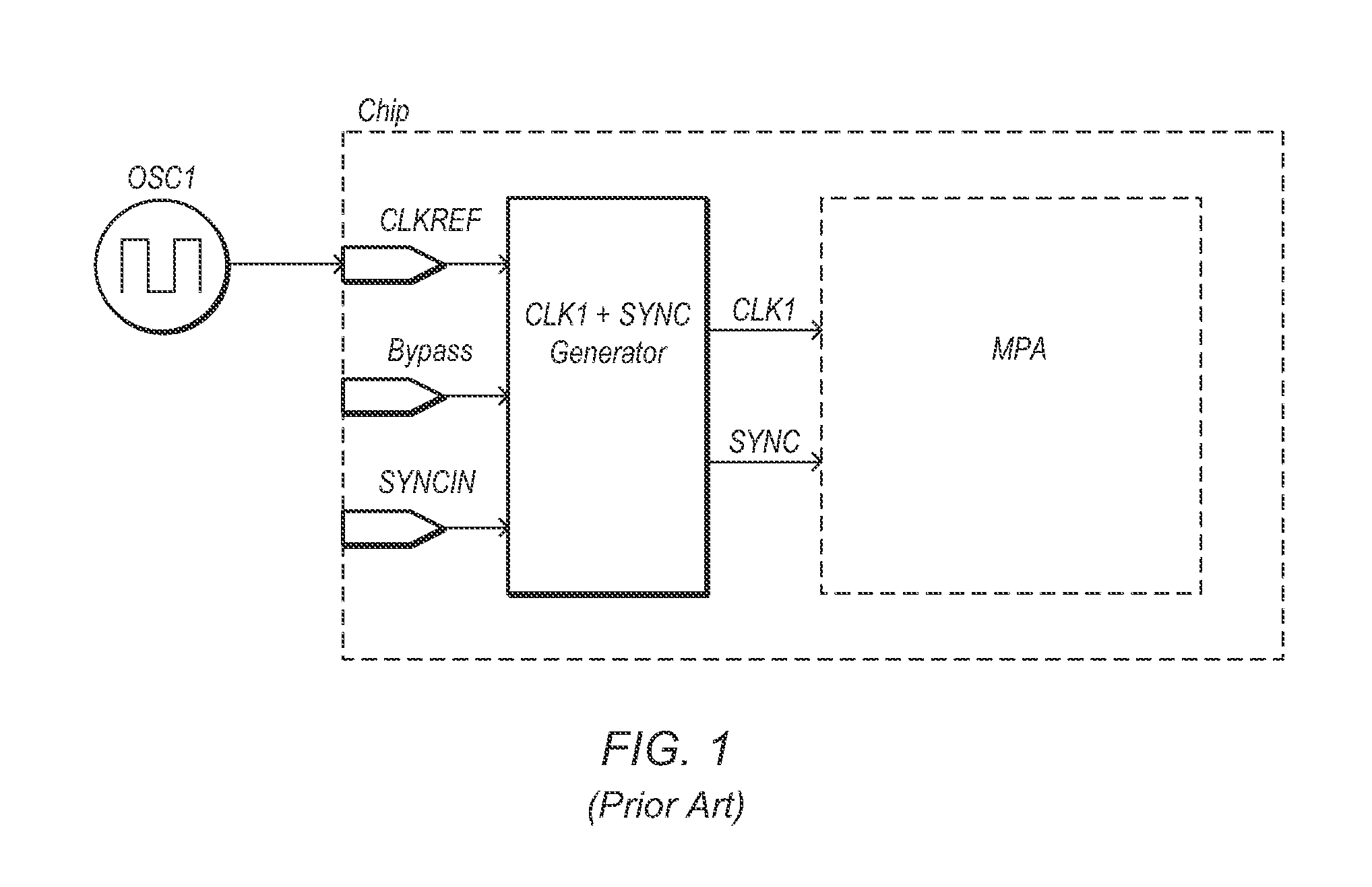

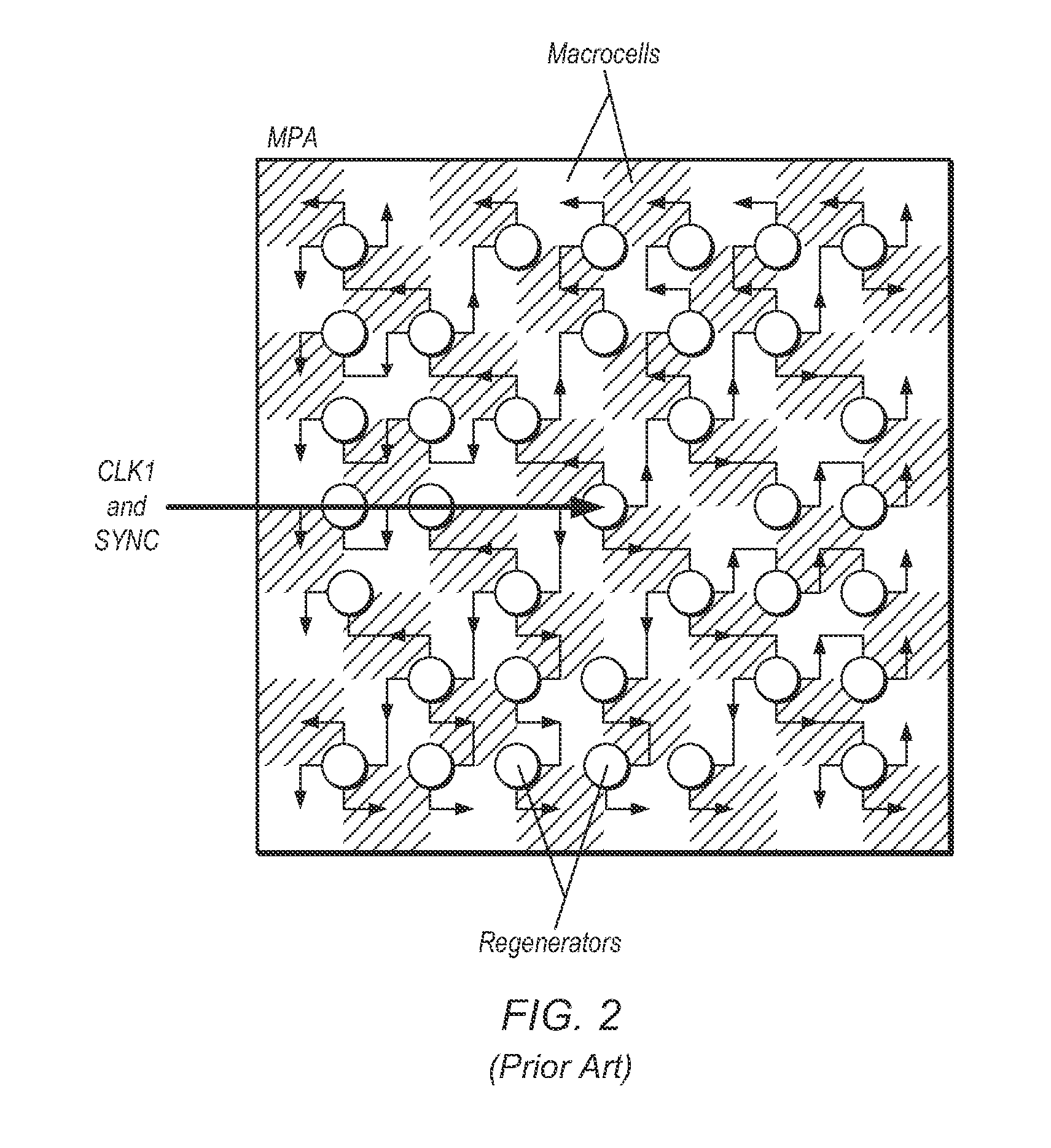

Multi-frequency clock skew control for inter-chip communication in synchronous digital systems

ActiveUS20140167825A1Power dissipationPulse automatic controlError detection/correctionDistribution treePhase-locked loop

Embodiments are disclosed of a multi-chip apparatus capable of performing multi-rate synchronous communication between component chips. Each chip may receive a common clock reference signal, and may generate an internal clock signal dependent on the clock reference signal. A clock distribution tree and phase-locked loop may be used to minimize internal clock skew at I / O circuitry at the chip perimeter. Each chip may also generate an internal synchronizing signal that is phase-aligned to the received clock reference signal. Each chip may use its respective synchronizing signal to synchronize multiple clock dividers that provide software-selectable reduced-frequency clock signals to the I / O cells of the chip. In this way, the reduced-frequency clock signals of the multiple chips are edge-aligned to the low-skew internal clock signals, and phase-aligned to the common clock reference signal, allowing the I / O cells of the multiple chips to perform synchronous communication at multiple rates with low clock skew.

Owner:COHERENT LOGIX

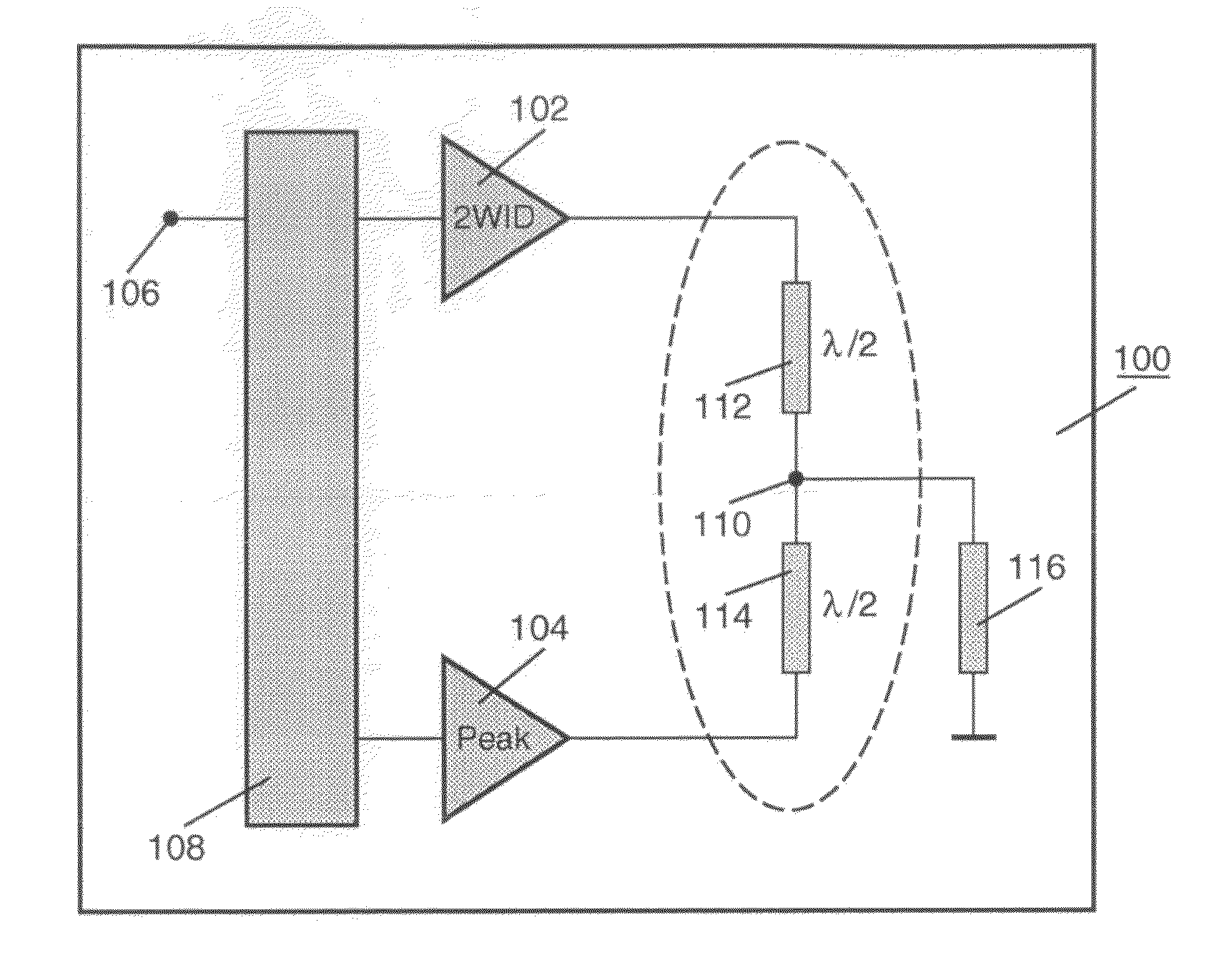

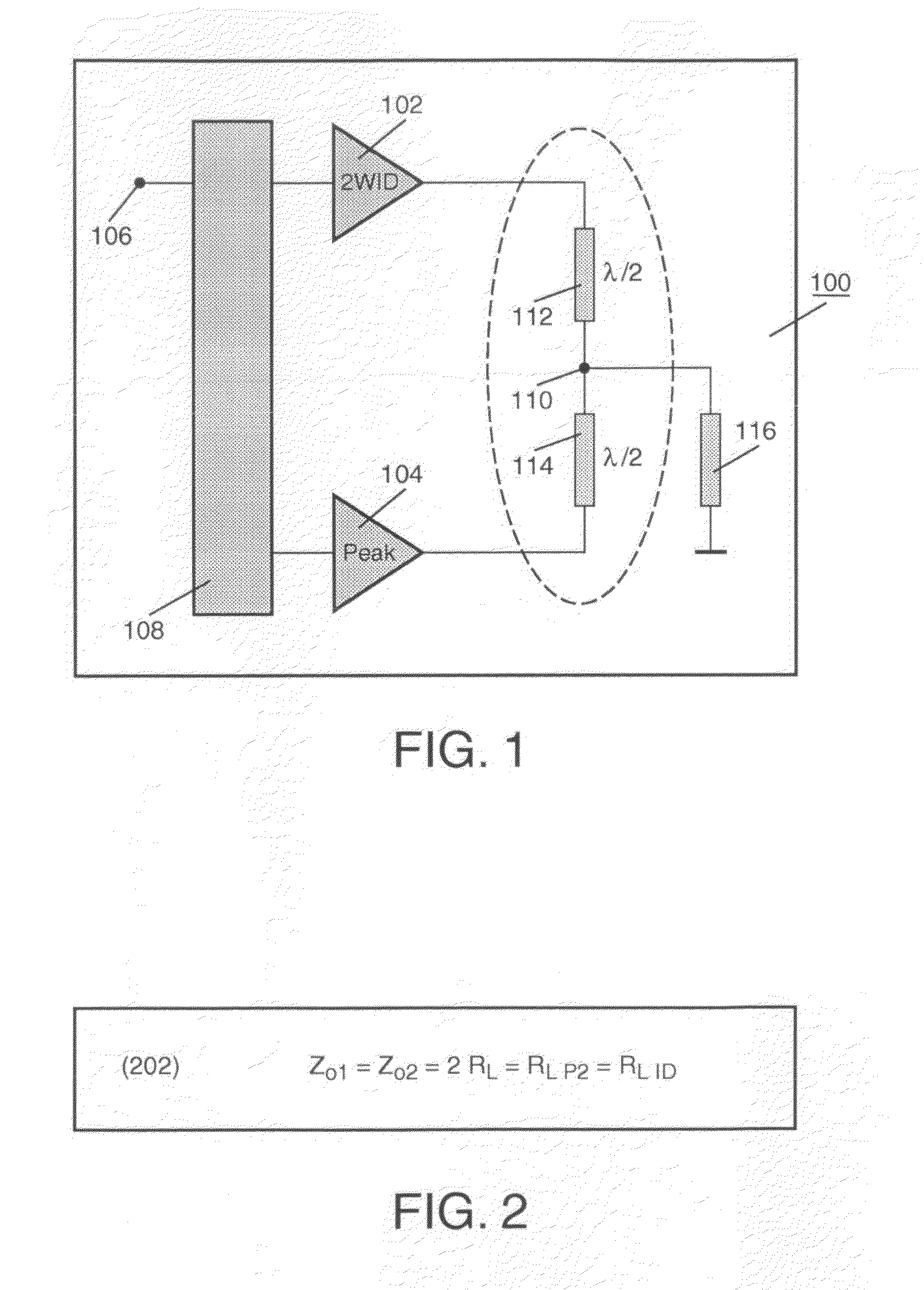

Multi-way doherty amplifier

ActiveUS20100188147A1High similarityImproves consistenceAmplifier combinationsAmplifier modifications to reduce detrimental impedenceAudio power amplifierDevice material

An electronic circuit has a multi-way Doherty amplifier. The multi-way Doherty amplifier comprises a two-way Doherty amplifier with a main stage and a first peak stage that are integrated in a semiconductor device; and at least one further peak stage implemented with a discrete power transistor.

Owner:AMPLEON NETHERLANDS

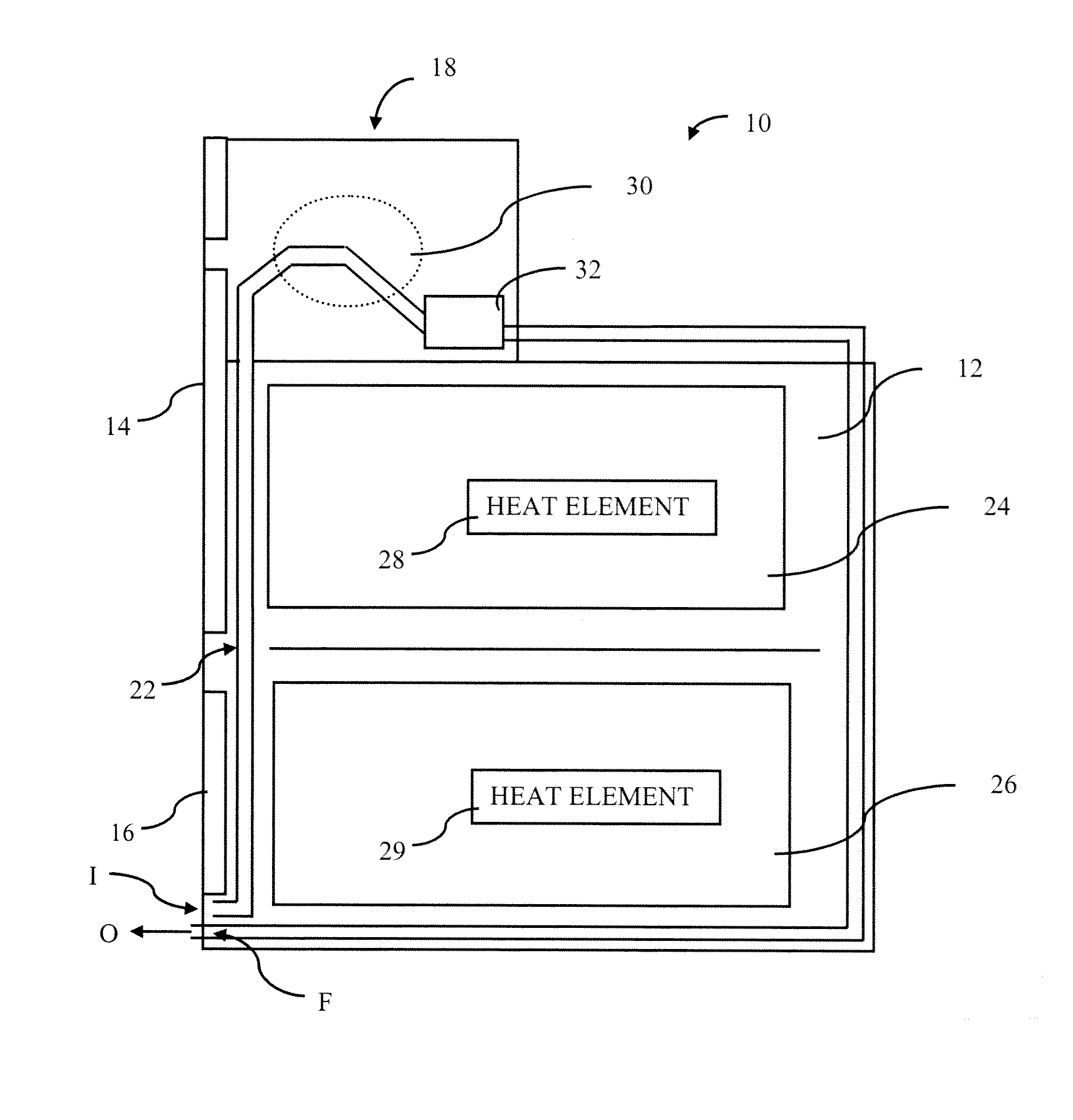

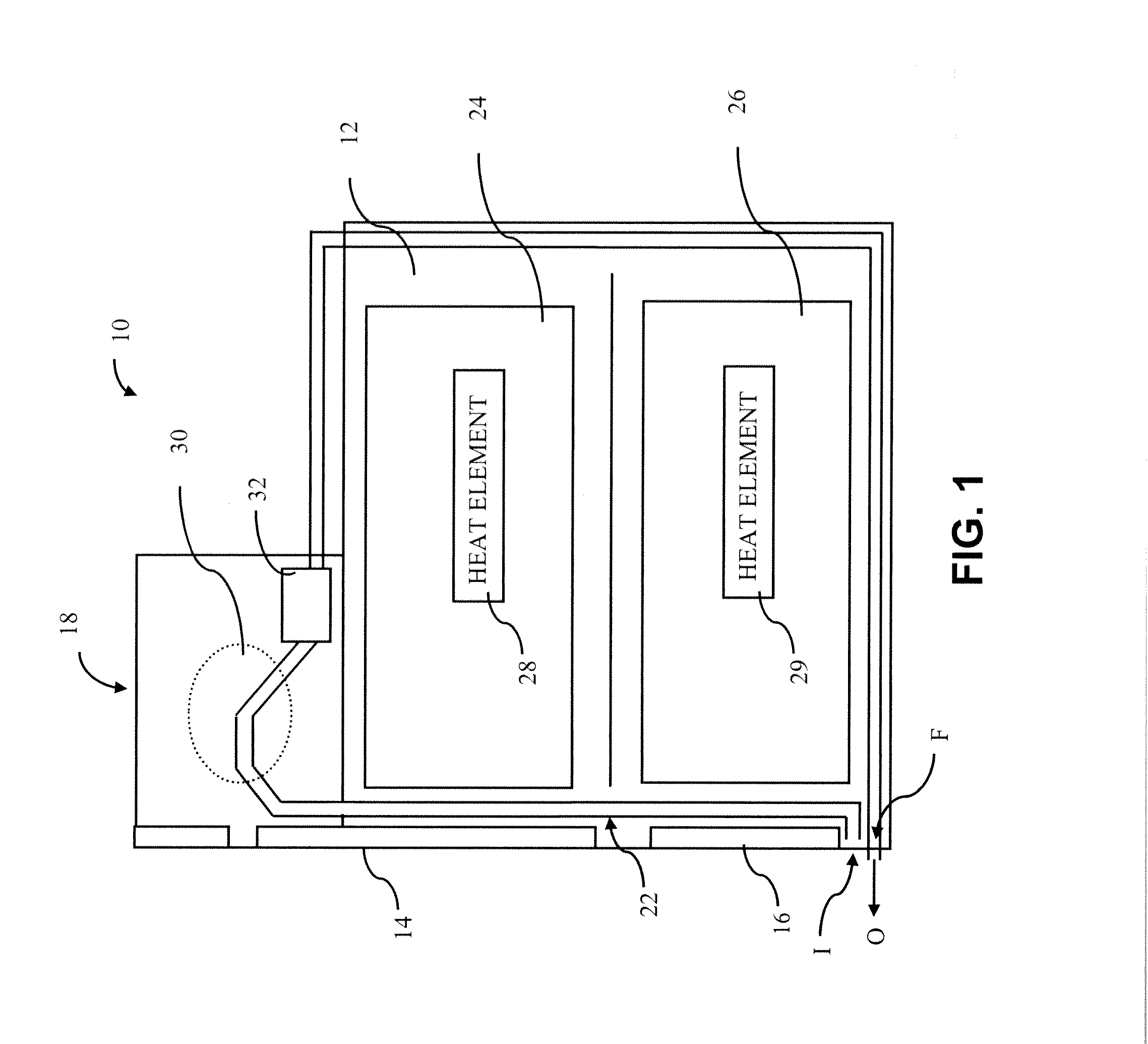

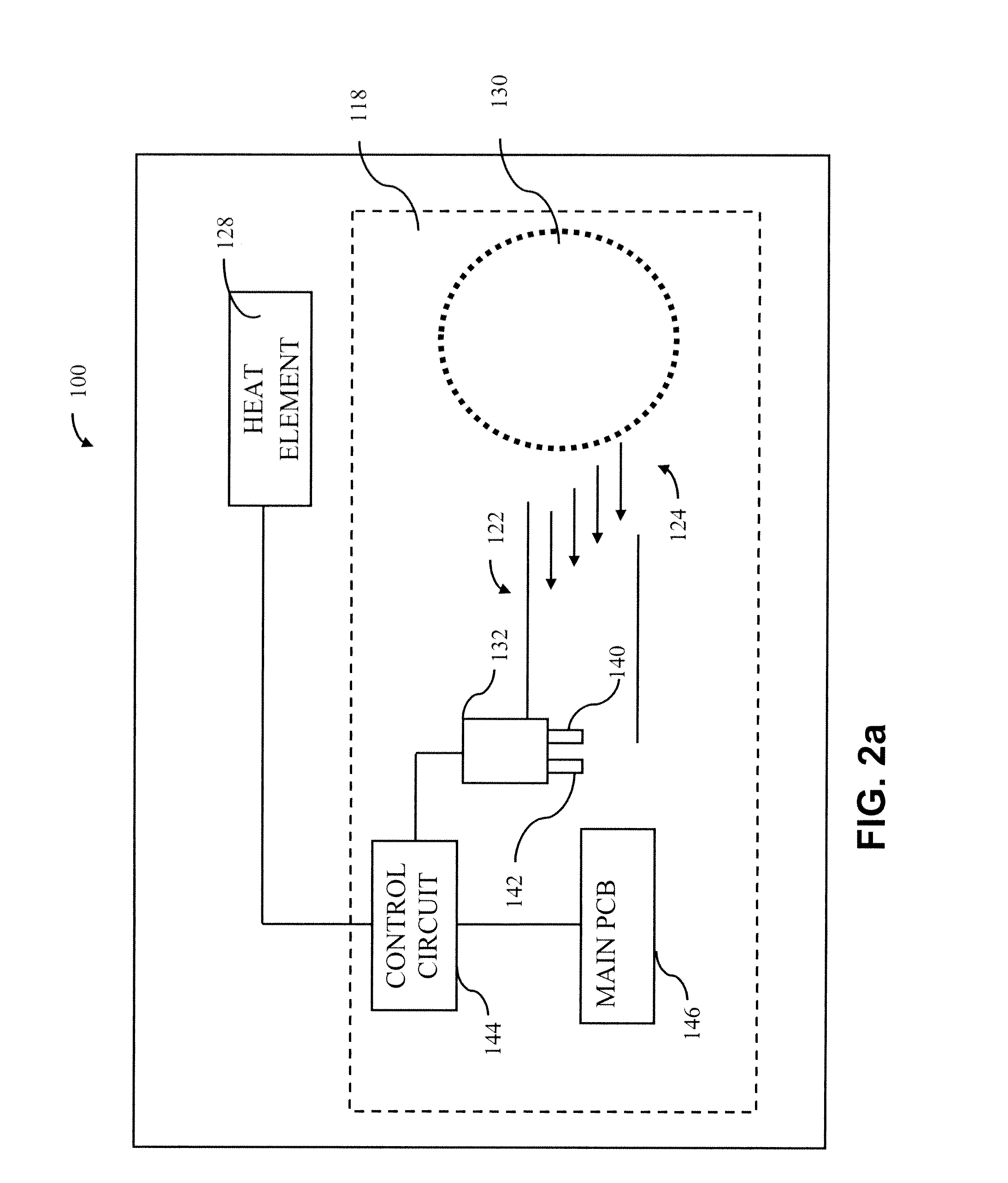

Appliance airflow detection using differential heating of electronic devices

ActiveUS20130025364A1Power dissipationContinuous operationTobacco treatmentVolume/mass flow by thermal effectsEngineeringThermistor

Apparatus and methods are disclosed to measure airflow within a chassis-cooling pathway of an appliance. The rate of airflow is determined based on the differential heating among a pair of sensor devices, such as thermistors, transistors, diodes or resistive thermal devices operating at distinctly different power levels. The appliance utilizes the calculated airflow rate to perform safety-related tasks, such as de-energizing heating elements when low or no airflow is detected.

Owner:HAIER US APPLIANCE SOLUTIONS INC

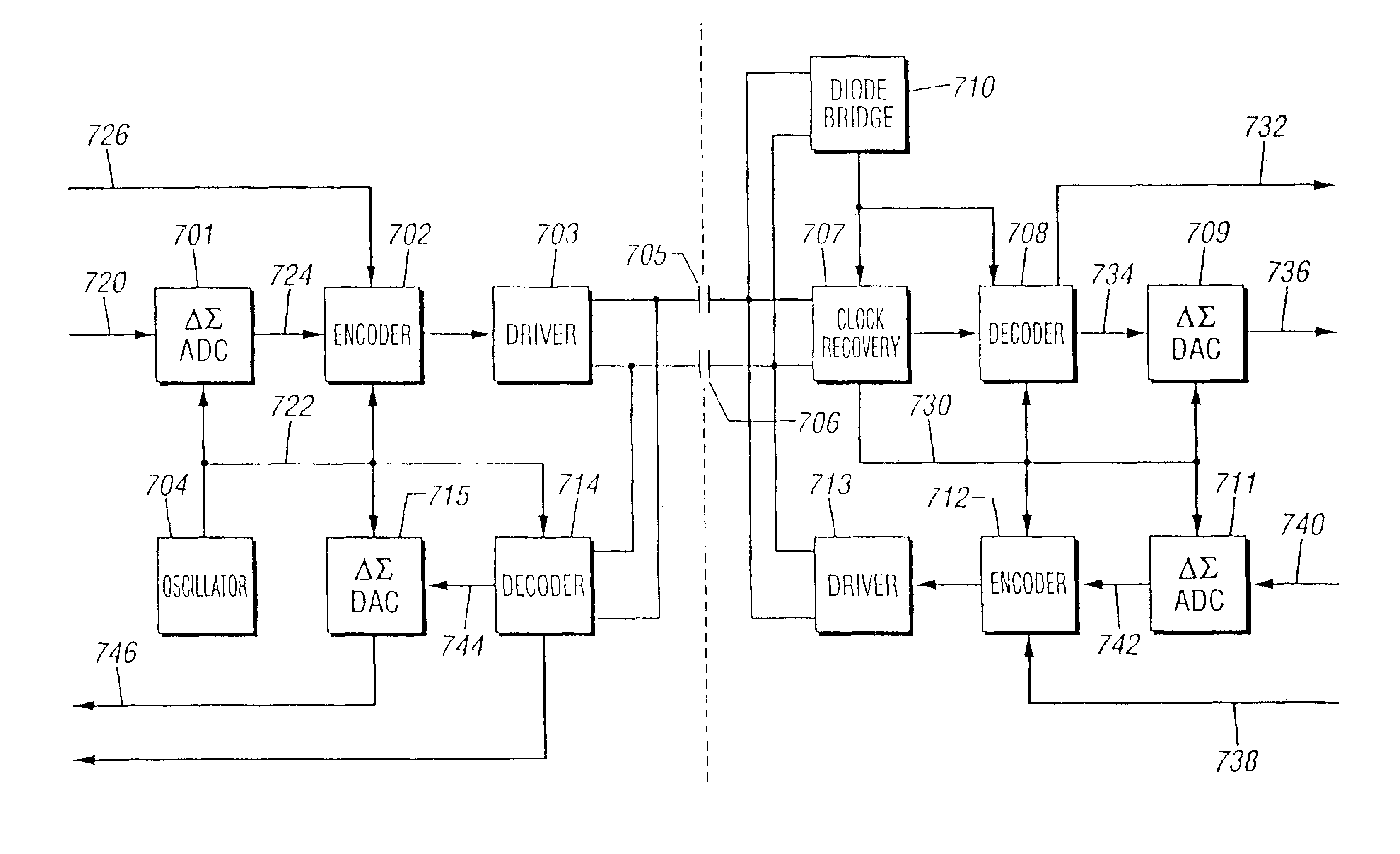

Loop current monitor circuitry and method for a communication system

InactiveUS6959083B2High distortionHigh impedanceAnalogue/digital conversionElectric signal transmission systemsCommunications systemGreek letter sigma

An audio signal processor which modifies audio signal components outside the conventional audio frequency band. The processor includes a Delta Sigma Modulator (DSM) that receives a non-interpolated digital audio signal sampled at a frequency of at least 198 kHz.

Owner:SILICON LAB INC

Apparatus and method for controlling the motor power

InactiveUS7960865B2Increase power consumptionPower dissipationElectric signal transmission systemsDc network circuit arrangementsElectric machineComputer module

The invention concerns a power control apparatus and a method for supplying power between an electric machine and an energy source. The power control apparatus contains at least two converters comprising a plurality of switches, at least some of which switches belong to a set of switch modules comprising a plurality of switches. In the method of the invention, a first set of switches belonging to at least two different modules and arranged to form a first converter is controlled by a first converter control, and a second set of switches arranged to form a second converter is controlled by a second converter control.

Owner:KONE CORP

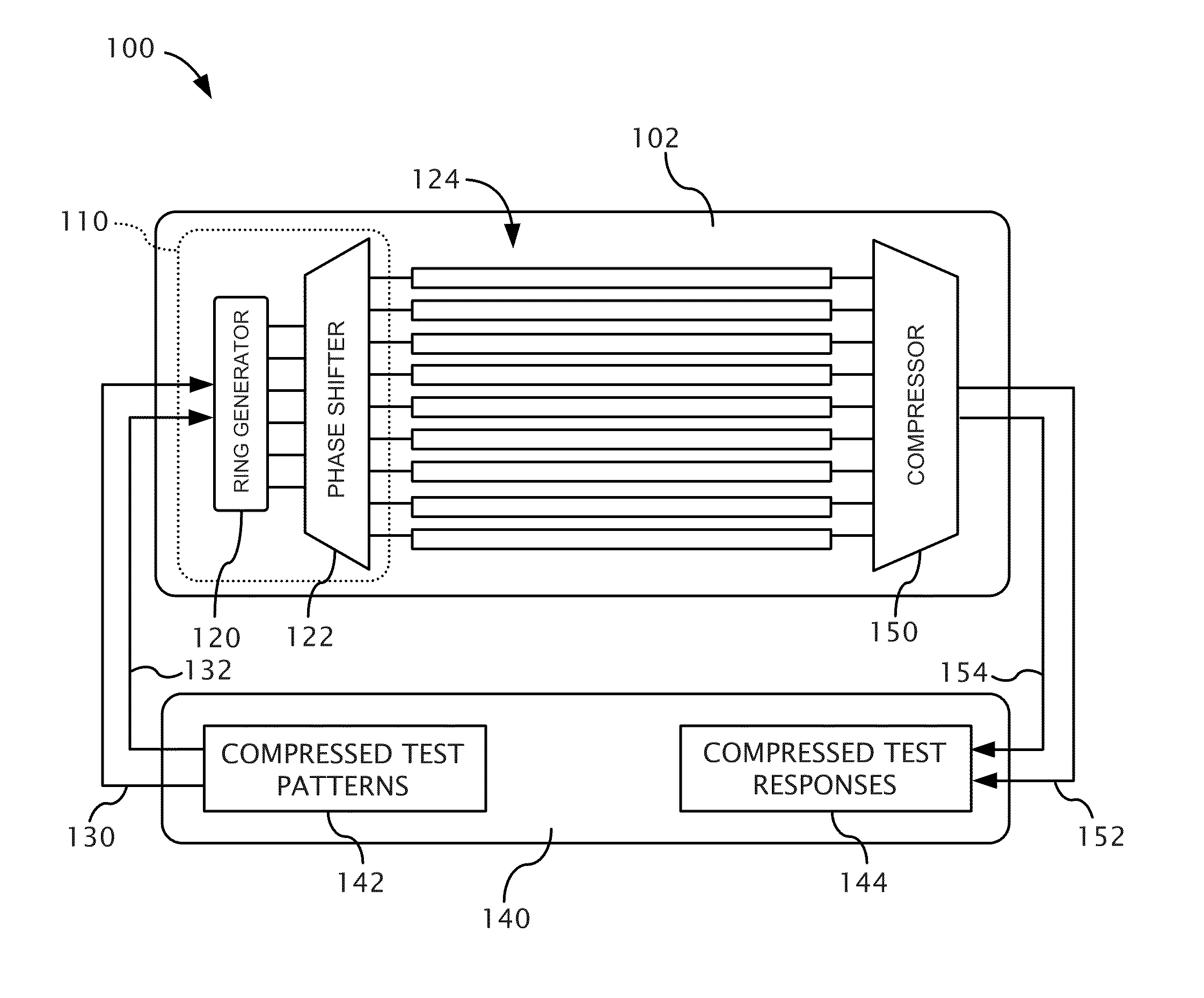

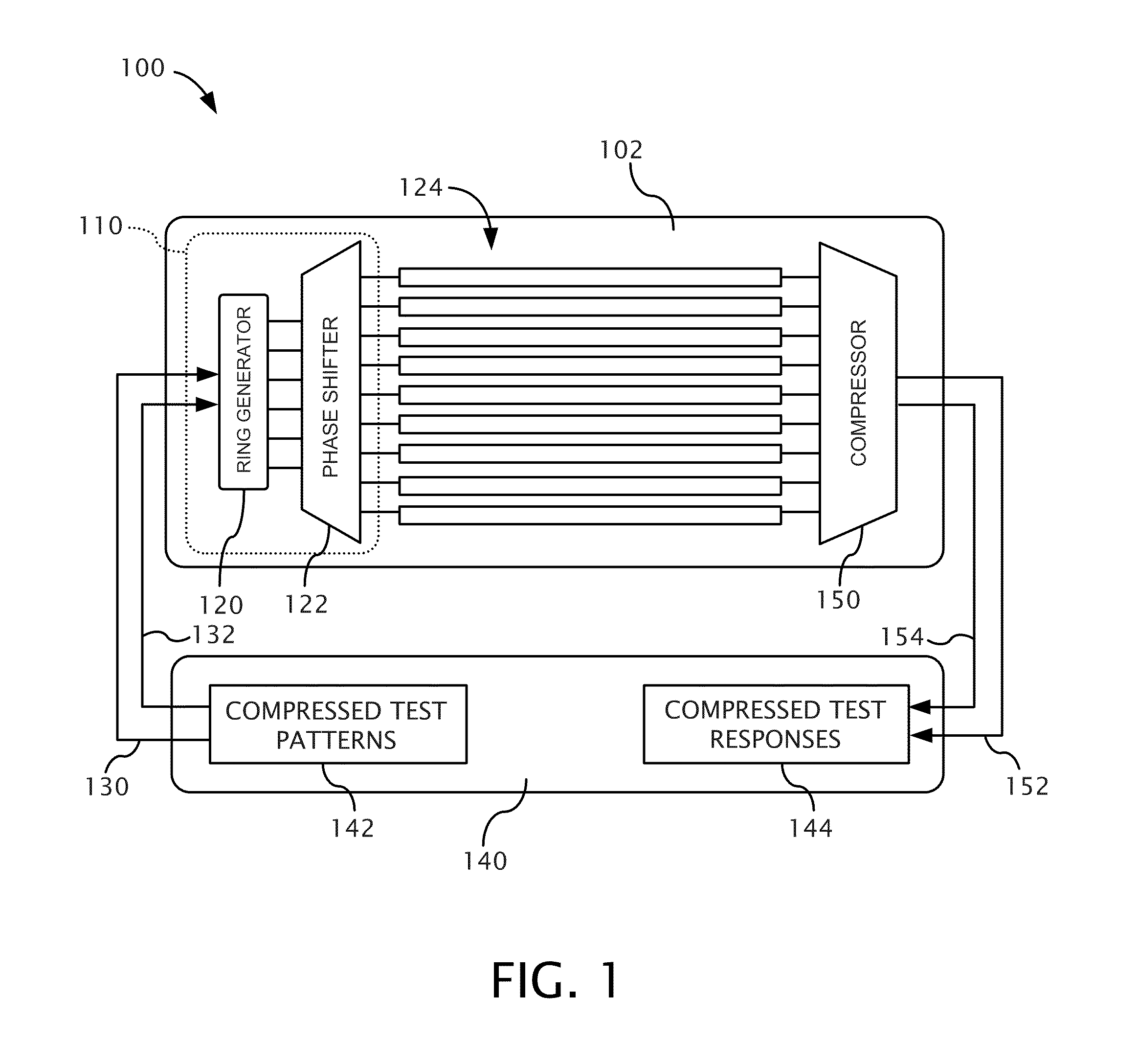

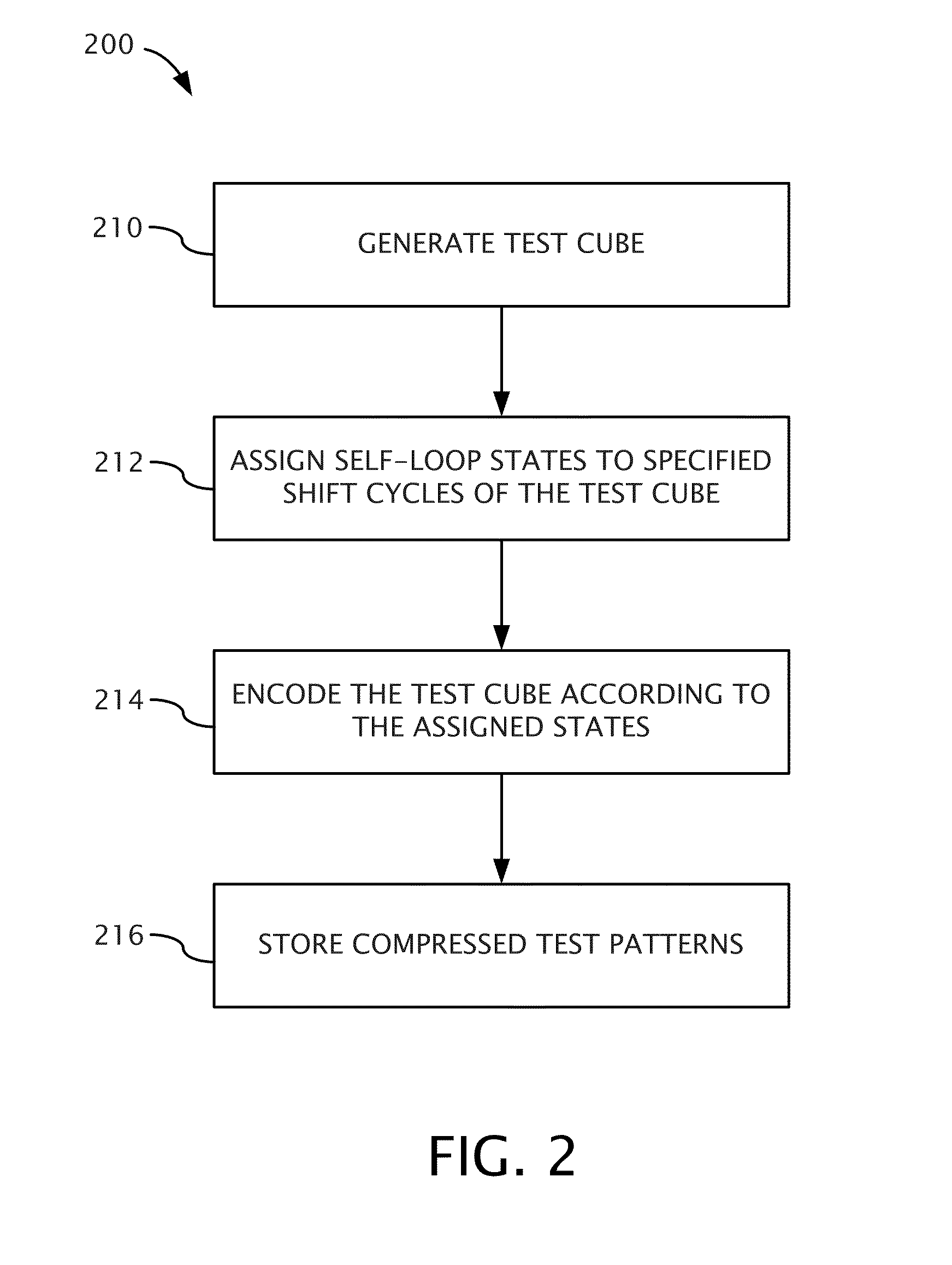

Low power decompression of test cubes

ActiveUS8046653B2Reduce ratePower dissipationElectronic circuit testingError detection/correctionHardware architecturePower test

Disclosed below are representative embodiments of methods, apparatus, and systems used to generate test patterns for testing integrated circuits. Embodiments of the disclosed technology can be used to provide a low power test scheme and can be integrated with a variety of compression hardware architectures (e.g., an embedded deterministic test (“EDT”) environment). Certain embodiments of the disclosed technology can reduce the switching rates, and thus the power dissipation, in scan chains with no hardware modification. Other embodiments use specialized decompression hardware and compression techniques to achieve low power testing.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

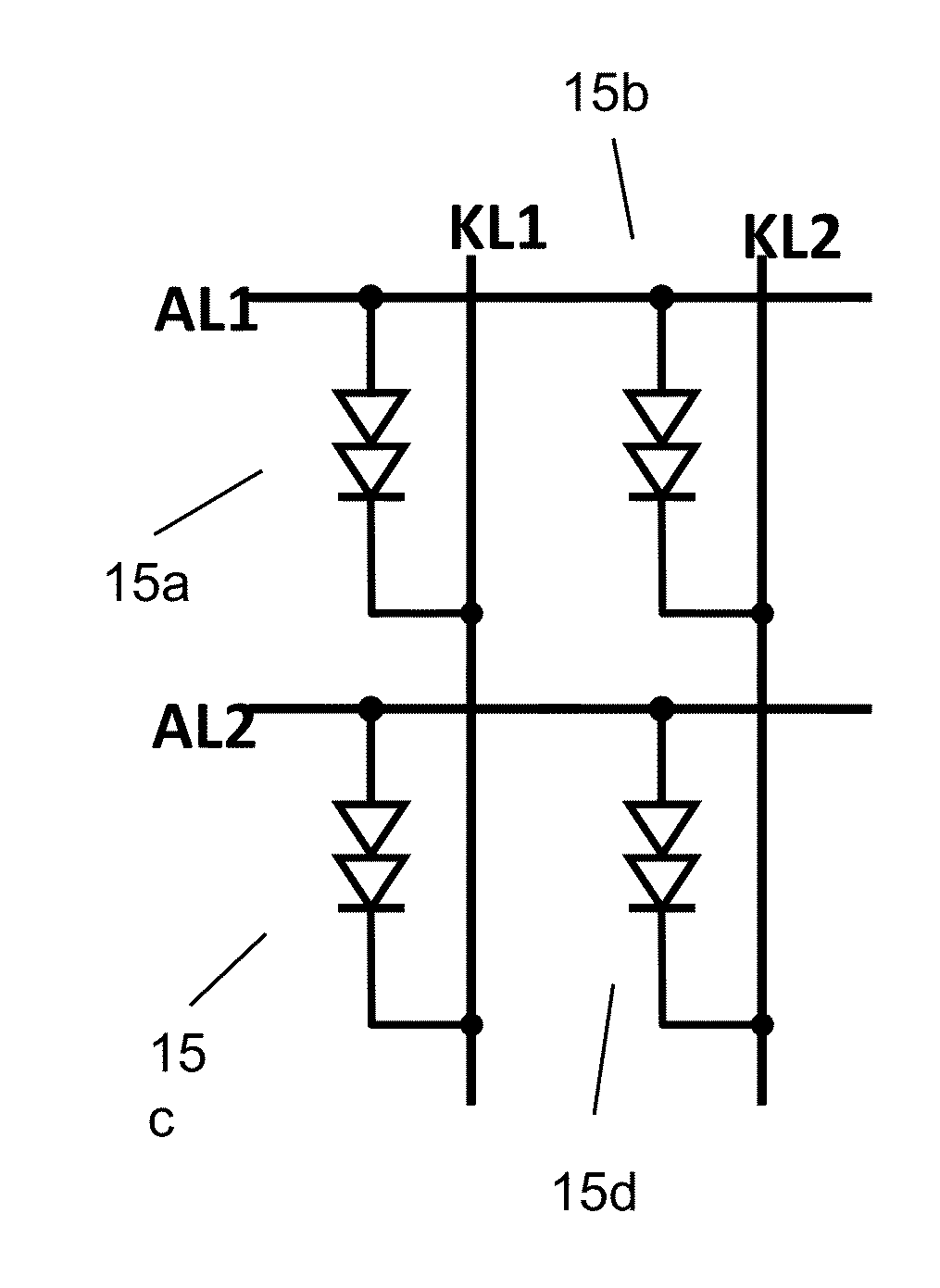

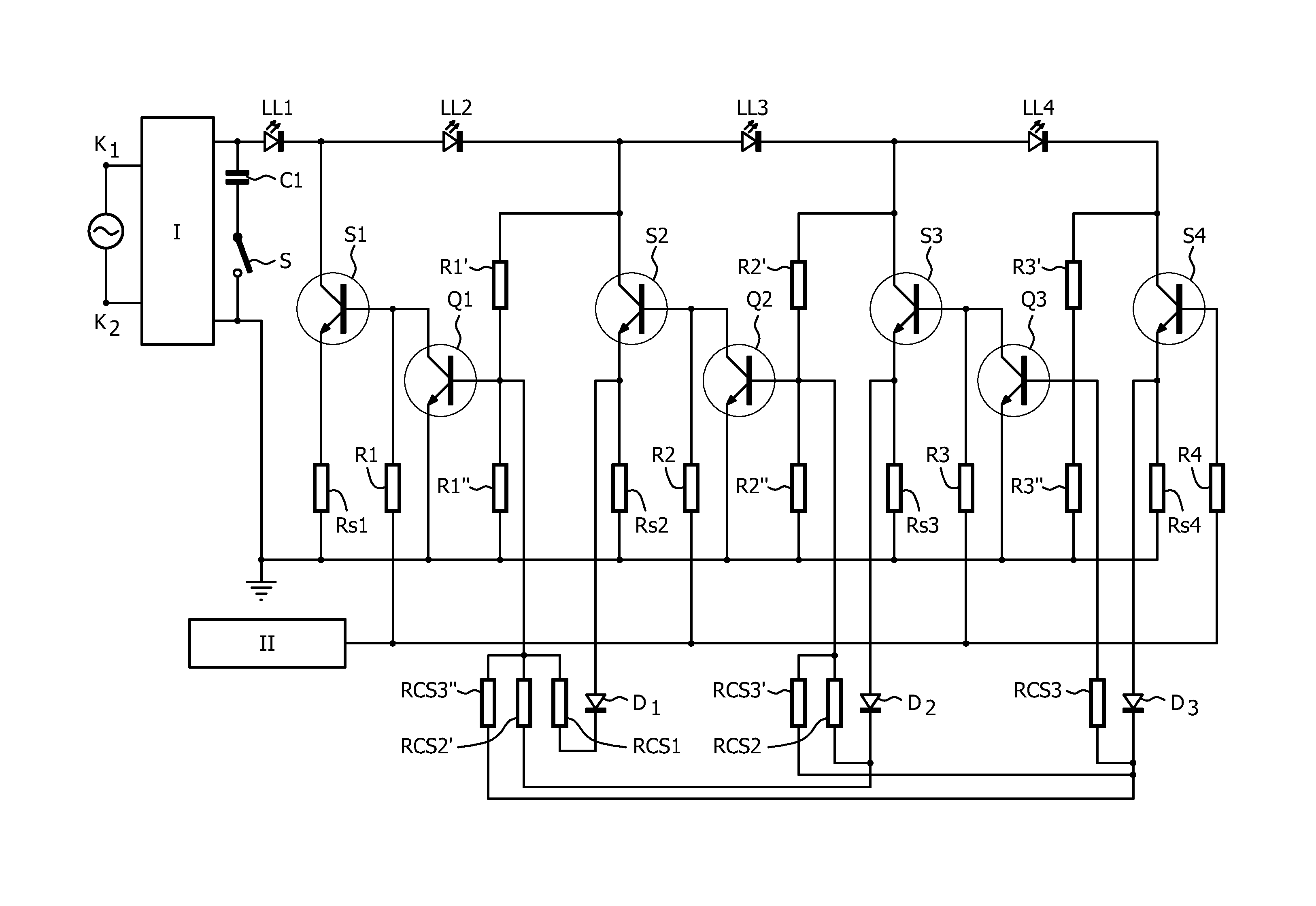

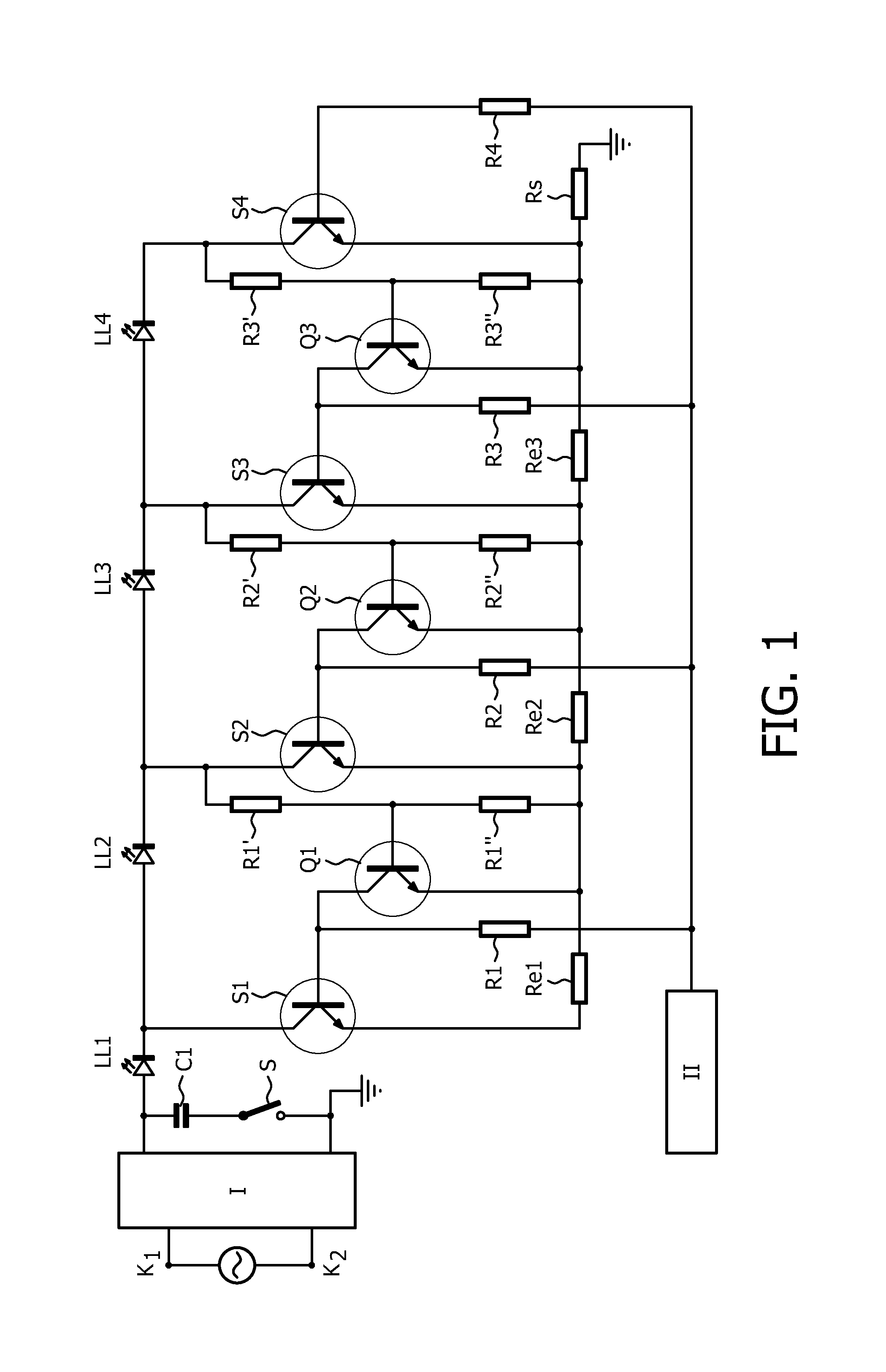

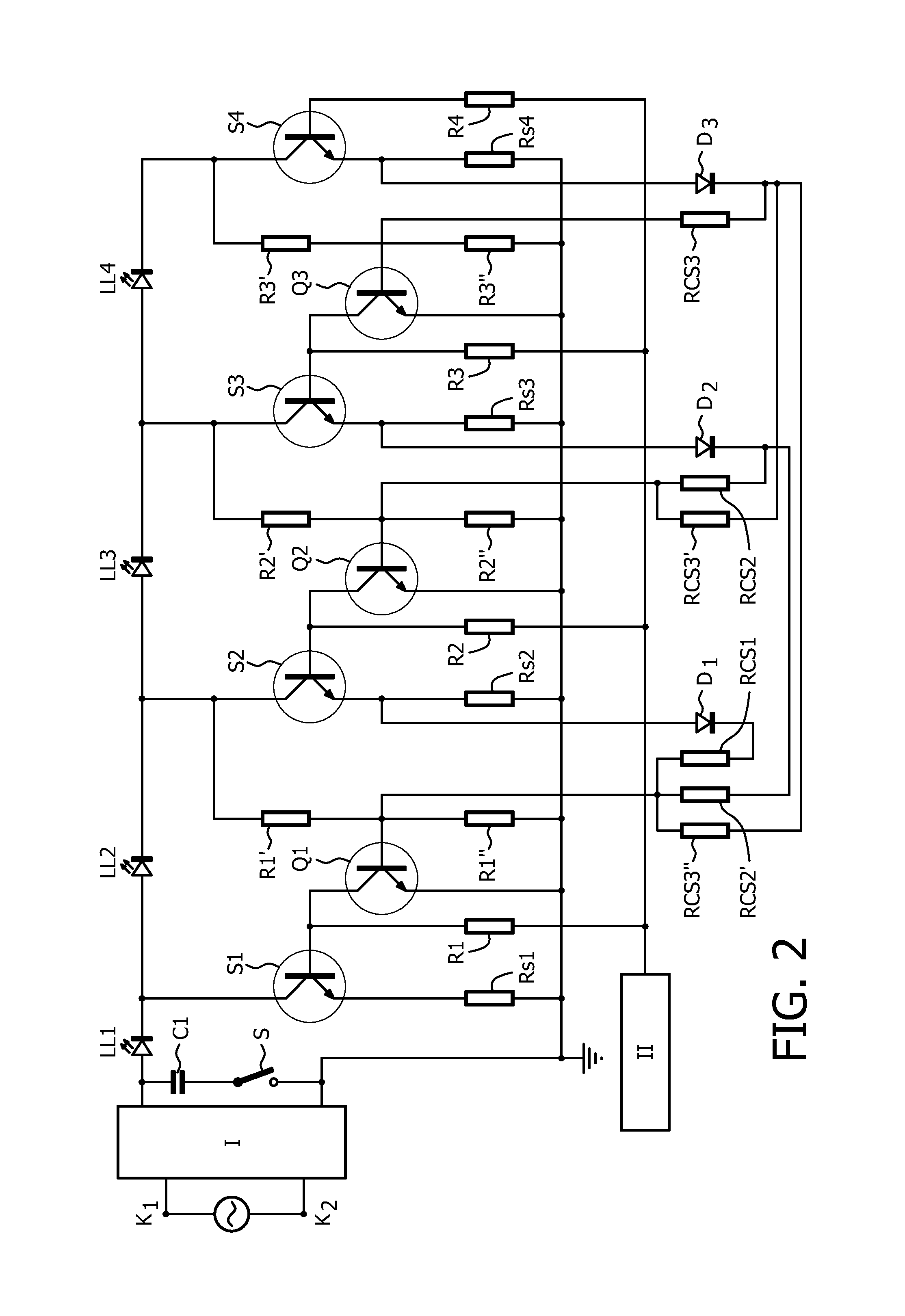

LED light source

InactiveUS9210757B2Power dissipationEasy to controlElectrical apparatusElectroluminescent light sourcesEngineeringVoltage

A string of LED loads is supplied by means of a rectified mains voltage. A cathode of each LED load is coupled to ground by means of a string. The strings are made conductive and non-conductive one by one in dependency of the instantaneous value of the rectified mains using both voltage and current sensing.

Owner:KONINK PHILIPS ELECTRONICS NV +1