Thyristor Volatile Random Access Memory and Methods of Manufacture

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035]1. An Individual Memory Cell

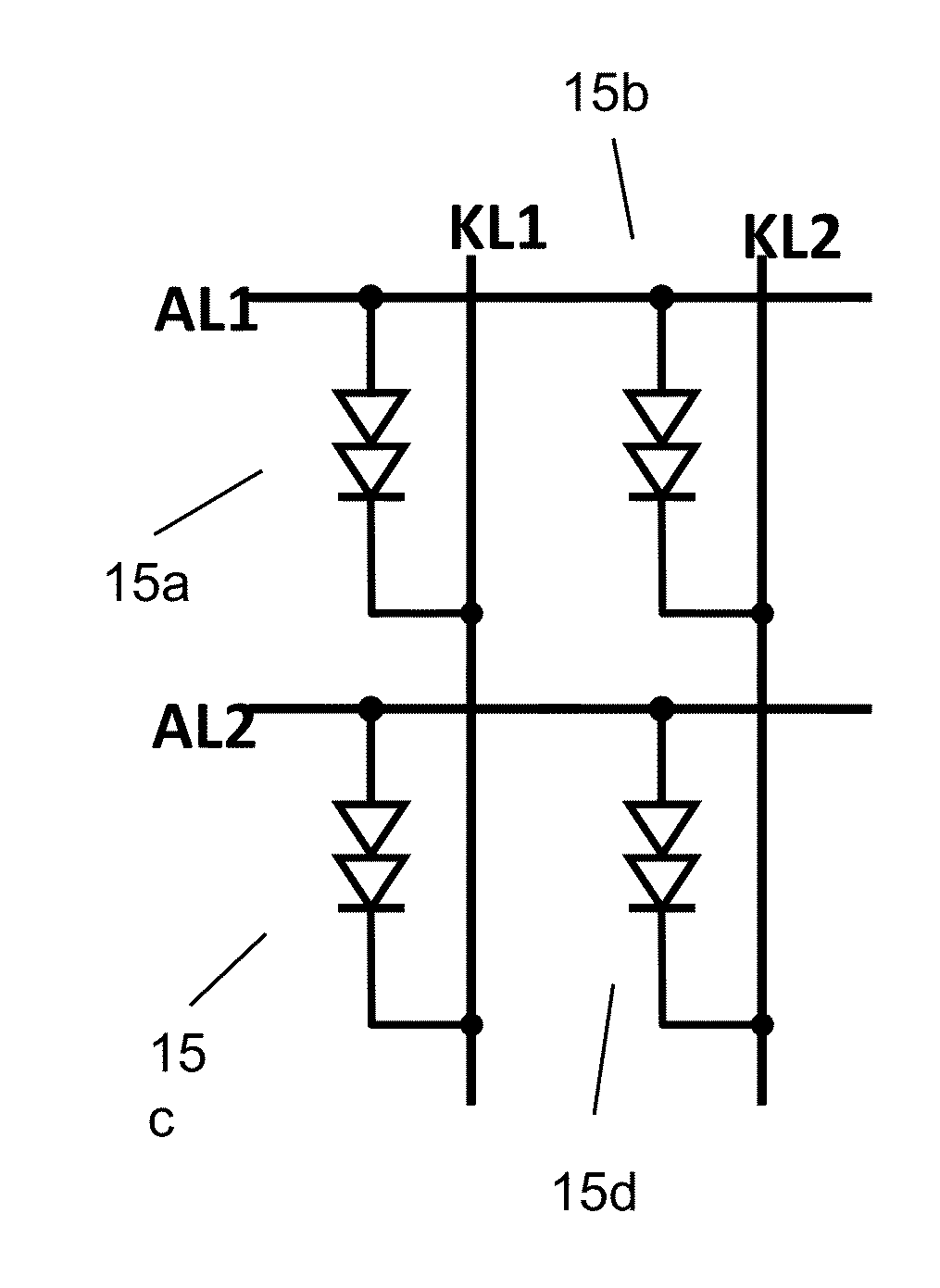

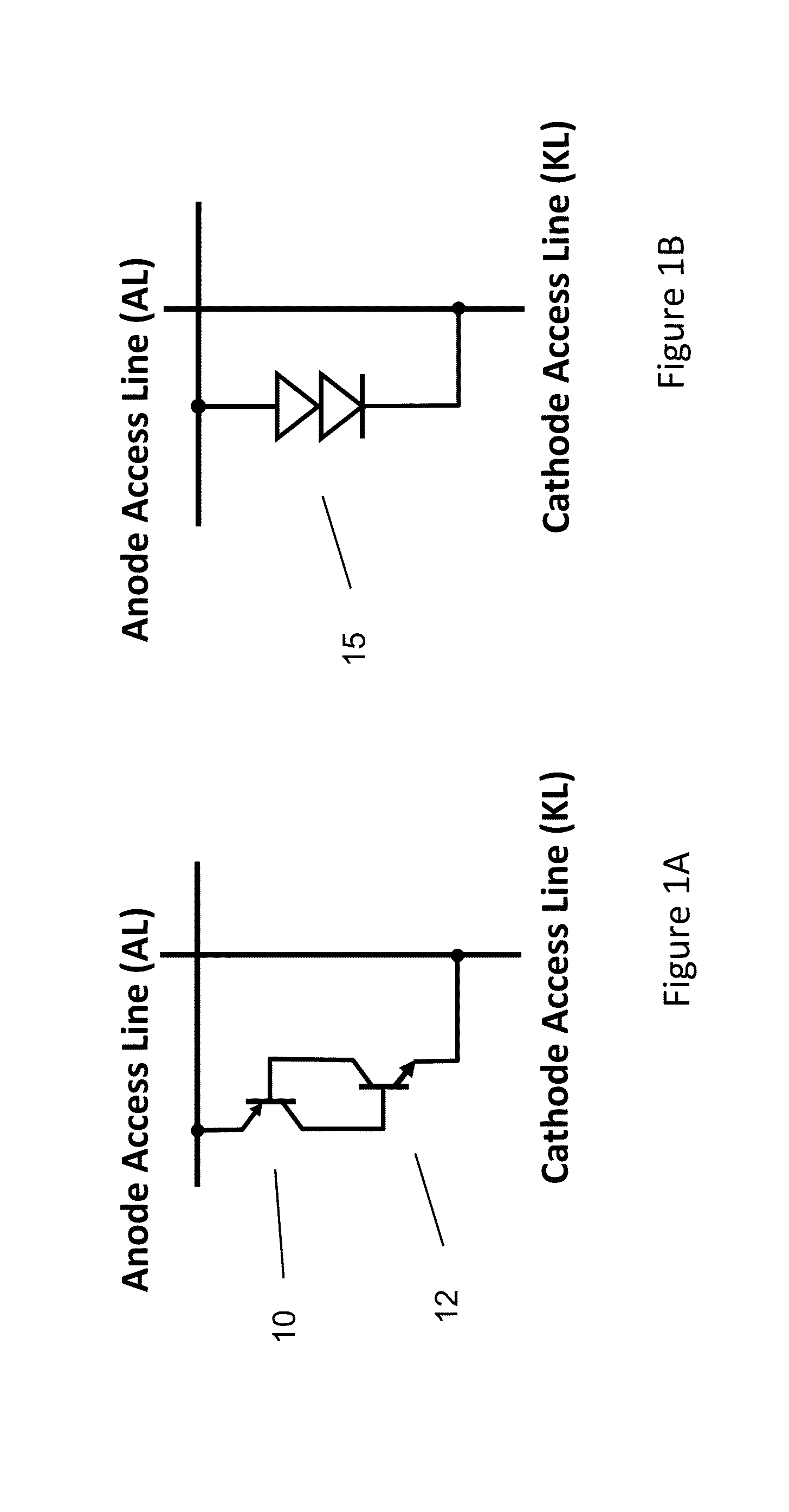

[0036]This invention provides a thyristor-based volatile memory cell, methods of manufacturing the cell, and methods of operating an array of such cells. The memory cell has particular utility for use in dynamic random access memory (DRAM) integrated circuit, as well as circuits in which DRAM memories are embedded. FIG. 1A is a circuit schematic of a thyristor coupled between an anode access line (AL) and a cathode access line (KL). The thyristor consists of two cross-coupled bipolar transistors 10 and 12. The emitter of PNP transistor 10 is coupled to the anode access line, while the emitter of NPN transistor 12 is coupled to the cathode access line. The collectors and bases of the two transistors are coupled together as shown. FIG. 1B is an equivalent circuit schematic showing the thyristor 15 using conventional notation. This notation is used in subsequent figures below.

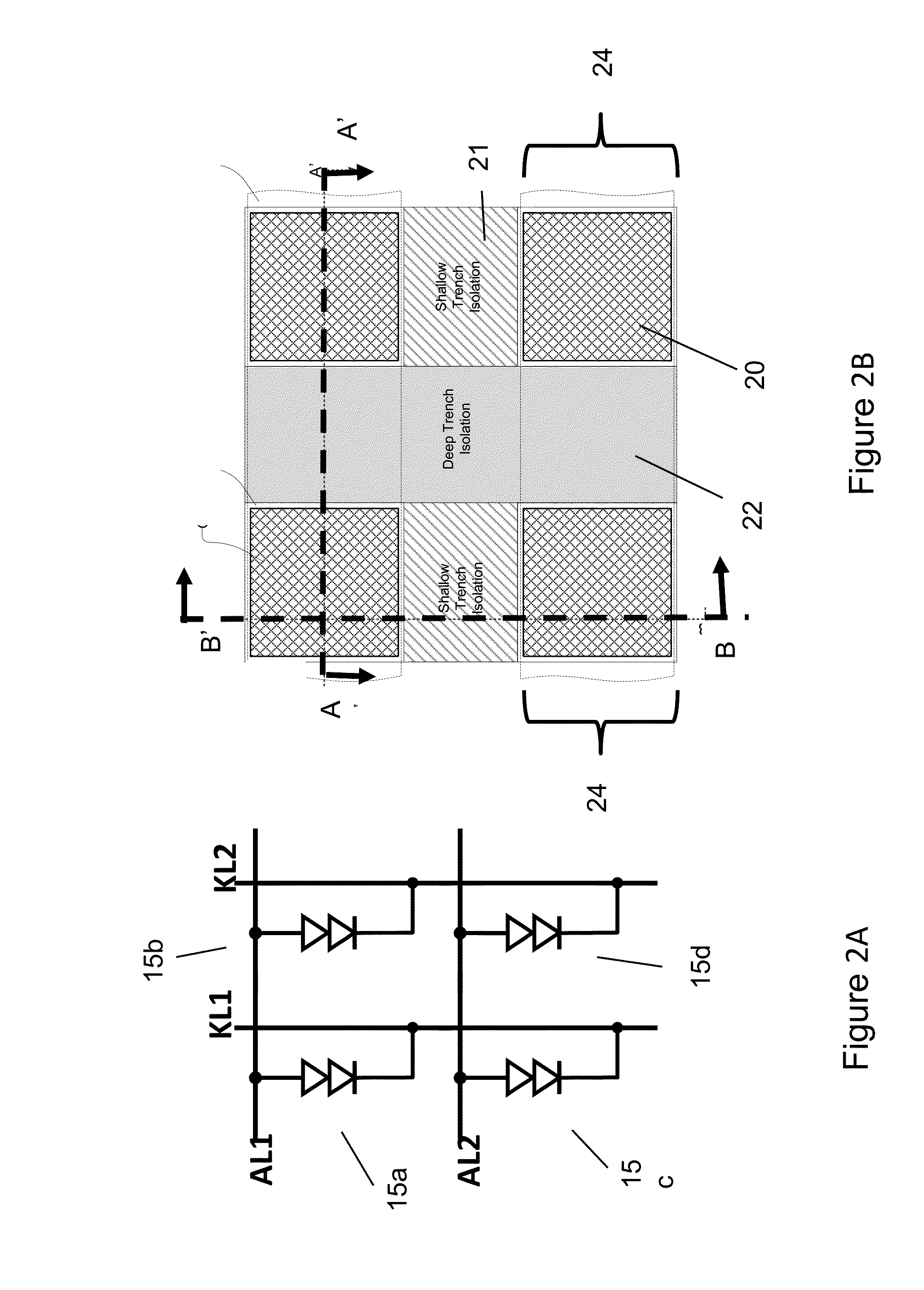

[0037]FIG. 2A illustrates an array of four thyristors 15a, 15b, 15c, and 15d ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More