Manufacturing method of wafer level package structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032]In the following detailed description, for purposes of explanation, numerous specific details are set forth in order to provide a thorough understanding of the disclosed embodiments. It will be apparent, however, that one or more embodiments may be practiced without these specific details. In other instances, well-known structures and devices are schematically shown in order to simplify the drawing.

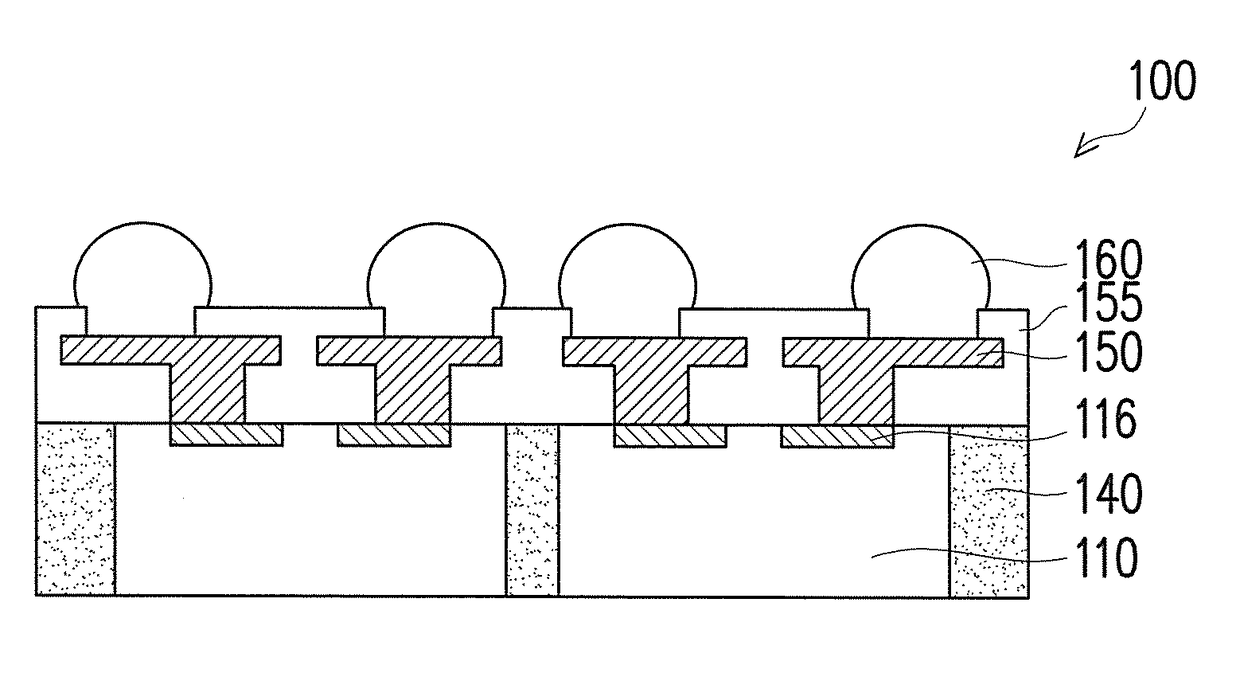

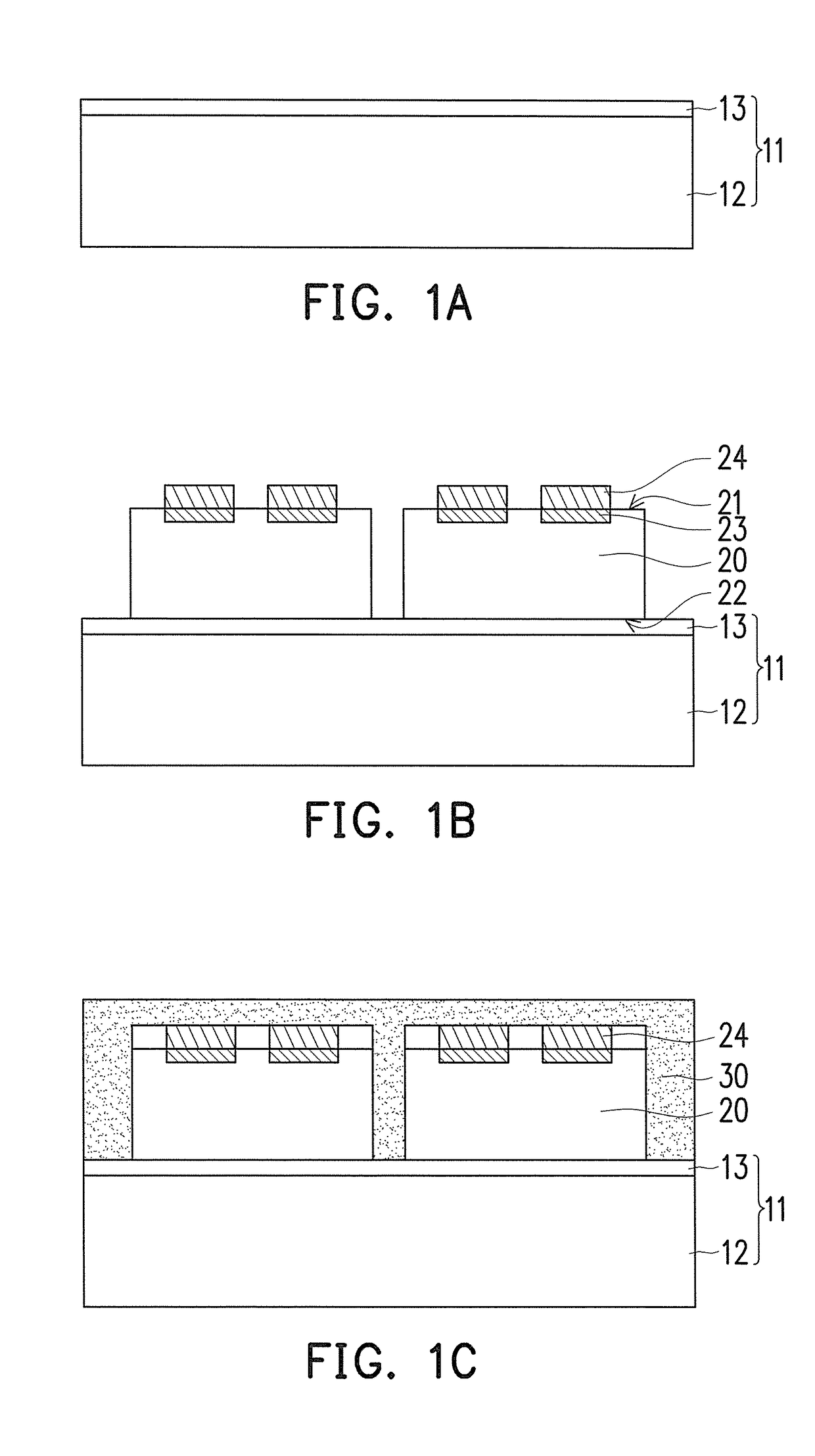

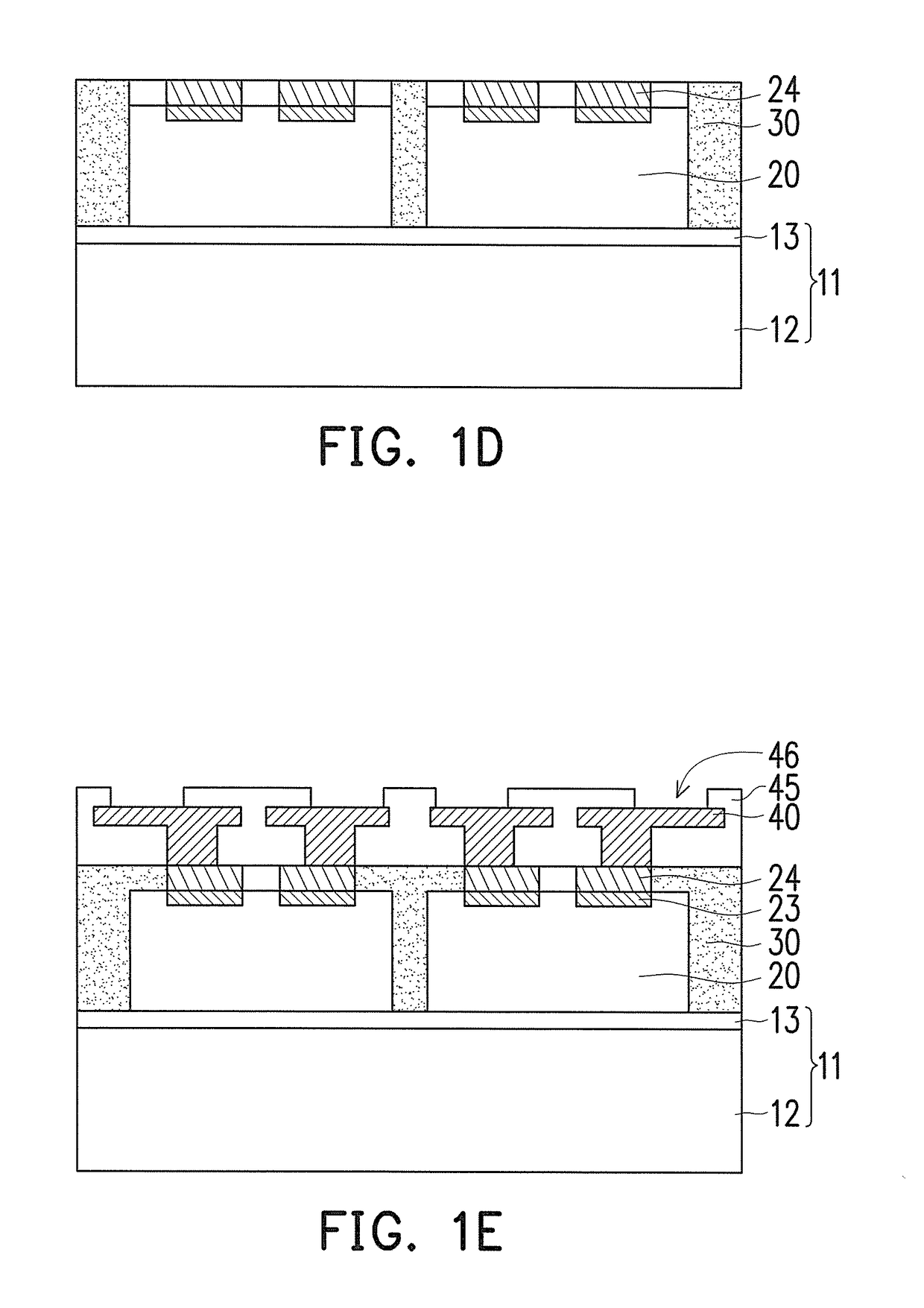

[0033]FIG. 2A to FIG. 2F are schematic diagrams of a manufacturing process of a wafer level package structure according to an embodiment of the invention. FIG. 3 is a flow diagram of a manufacturing process of a wafer level package structure according to an embodiment of the invention. Referring to FIG. 2A and FIG. 3, a manufacturing process of a wafer level package structure 200 of the embodiment includes the following steps. First, a chip 110 is provided. The chip 110 includes an active surface 112, a back surface 114 opposite to the active surface 112, and a plurality of pads 116...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More