Integrated circuit structure incorporating stacked field effect transistors and method

a field effect transistor and integrated circuit technology, applied in the direction of transistors, electrical apparatus, semiconductor devices, etc., can solve the problems of limiting the area savings, complex supply of power and/or signal connections to the source/drain region of the lower fets in the stacked pair, and corresponding increase in short channel effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

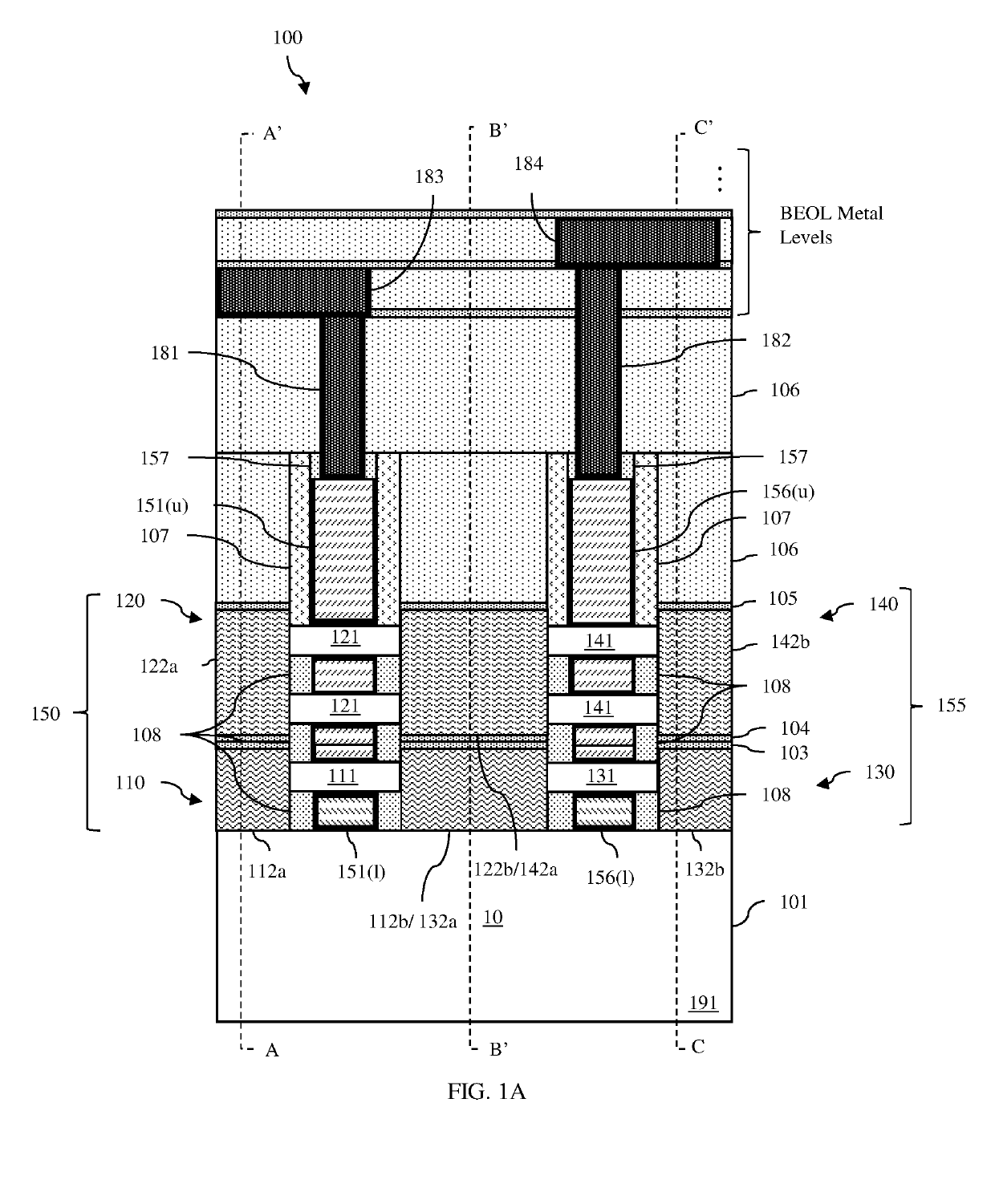

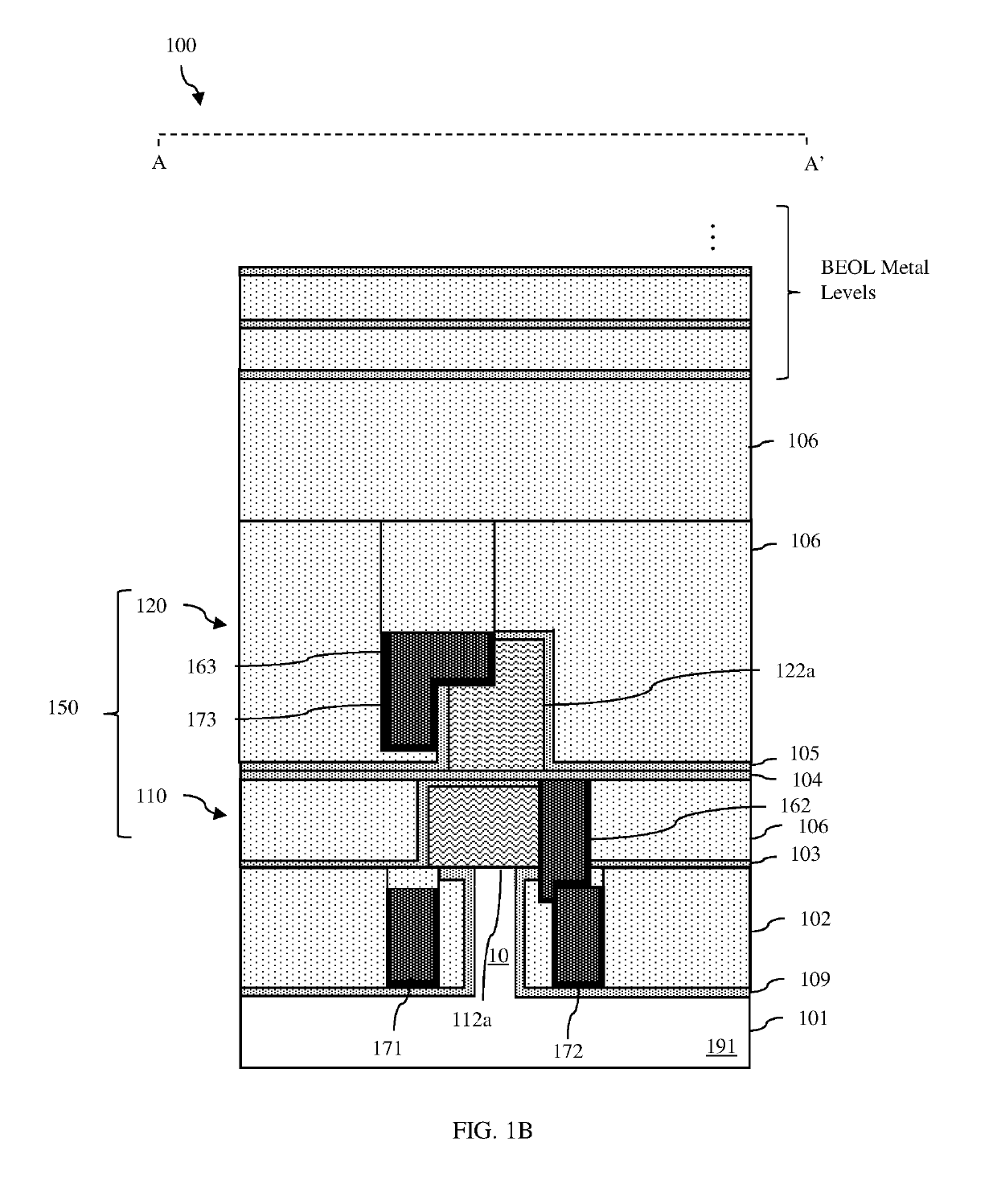

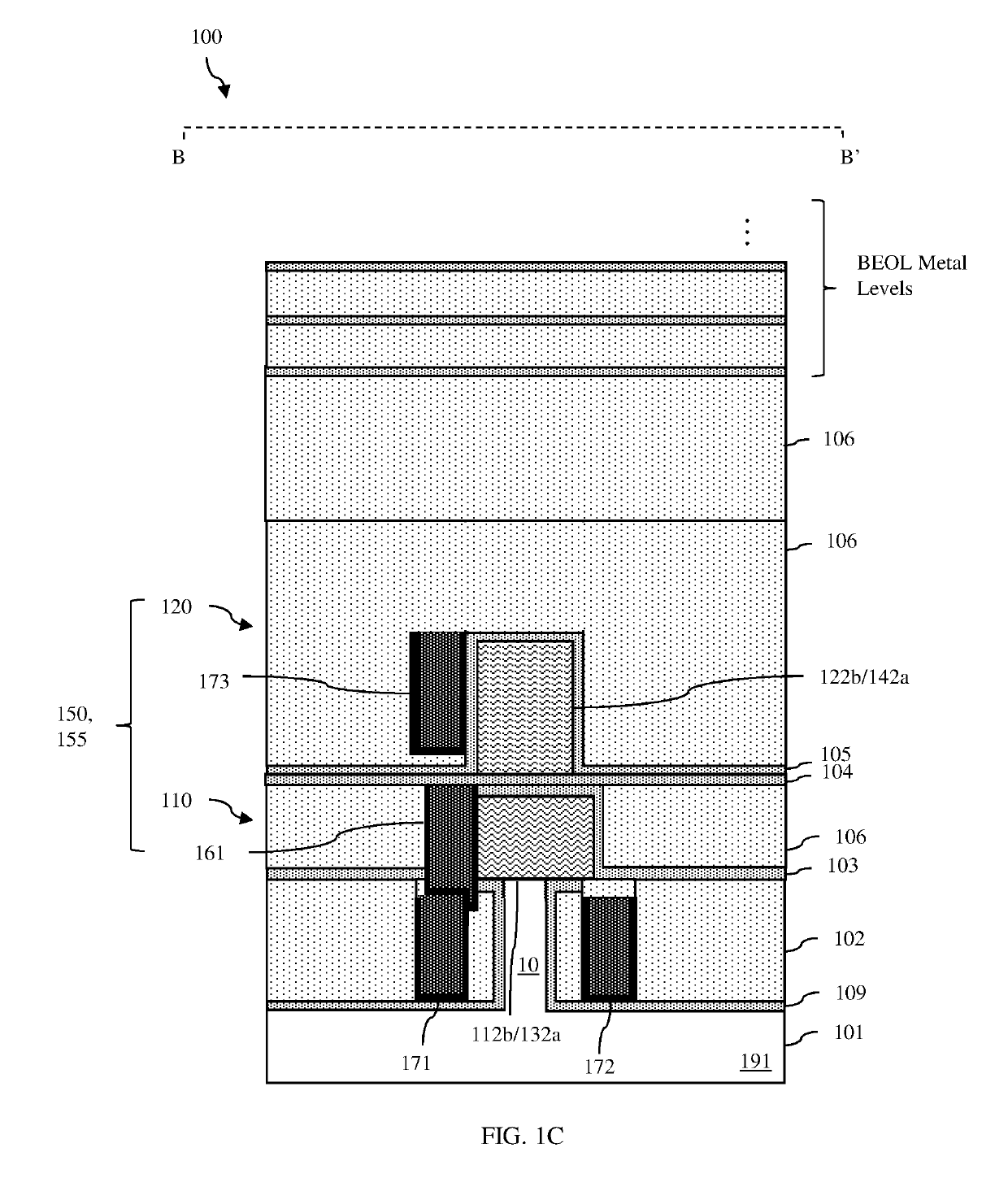

[0037]As mentioned above, a conventional layout with multiple field effect transistors (FETs) (e.g., multiple gate-all-around field effect transistors (GAAFETs)) will typically have a row of N-type FETs on one-side, a corresponding row of P-type FETs on the opposite side, and shared gates that traverse and are adjacent to the channel regions of side-by-side pairs of N-type and P-type FETs. Contrarily, a layout with multiple stacked pairs of FETs (e.g., stacked pairs of GAAFETs) will have P-type FETs on one-level, N-type FETs on an adjacent level (i.e., above or below) and, shared gates that extend vertically across and are adjacent to the channel regions of stacked pairs of N-type and P-type FETs. Unfortunately, while stacked pairs of N-type and P-type FETs consume less chip area than side-by-side pairs of N-type and P-type FETs, providing the necessary power and / or signal connections to the source / drain regions of the lower FETs in the stacked pairs can be complex and may limit the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More