MRAM having memory cell array in which cross-point memory cells are arranged by hierarchical bit line scheme and data read method thereof

a memory cell array and data read technology, applied in the field of memory cell arrays, can solve the problems of insufficient practical utility, difficult to increase capacity or the degree of integration, and the difficulty of ensuring the read margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

[First Embodiment]

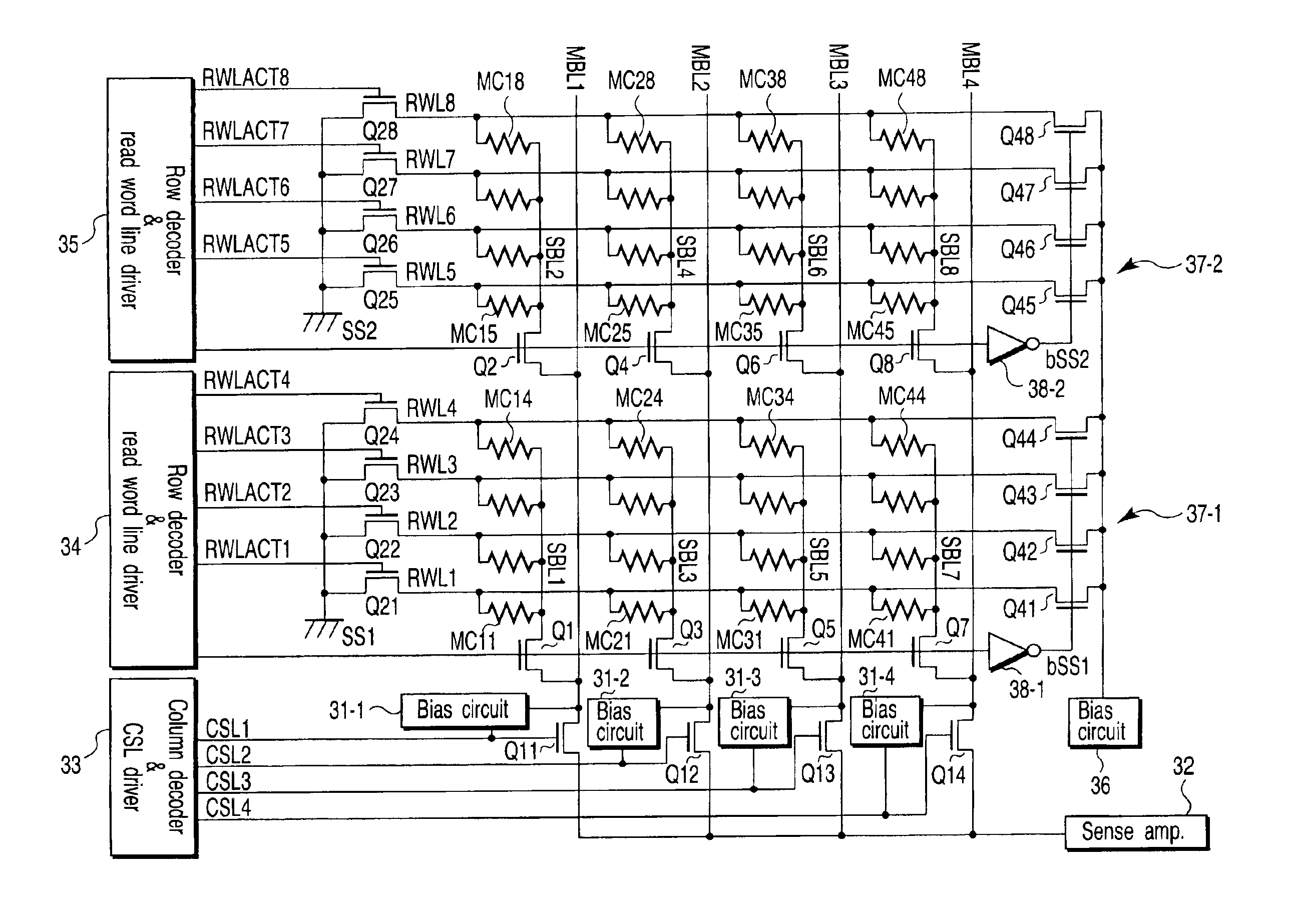

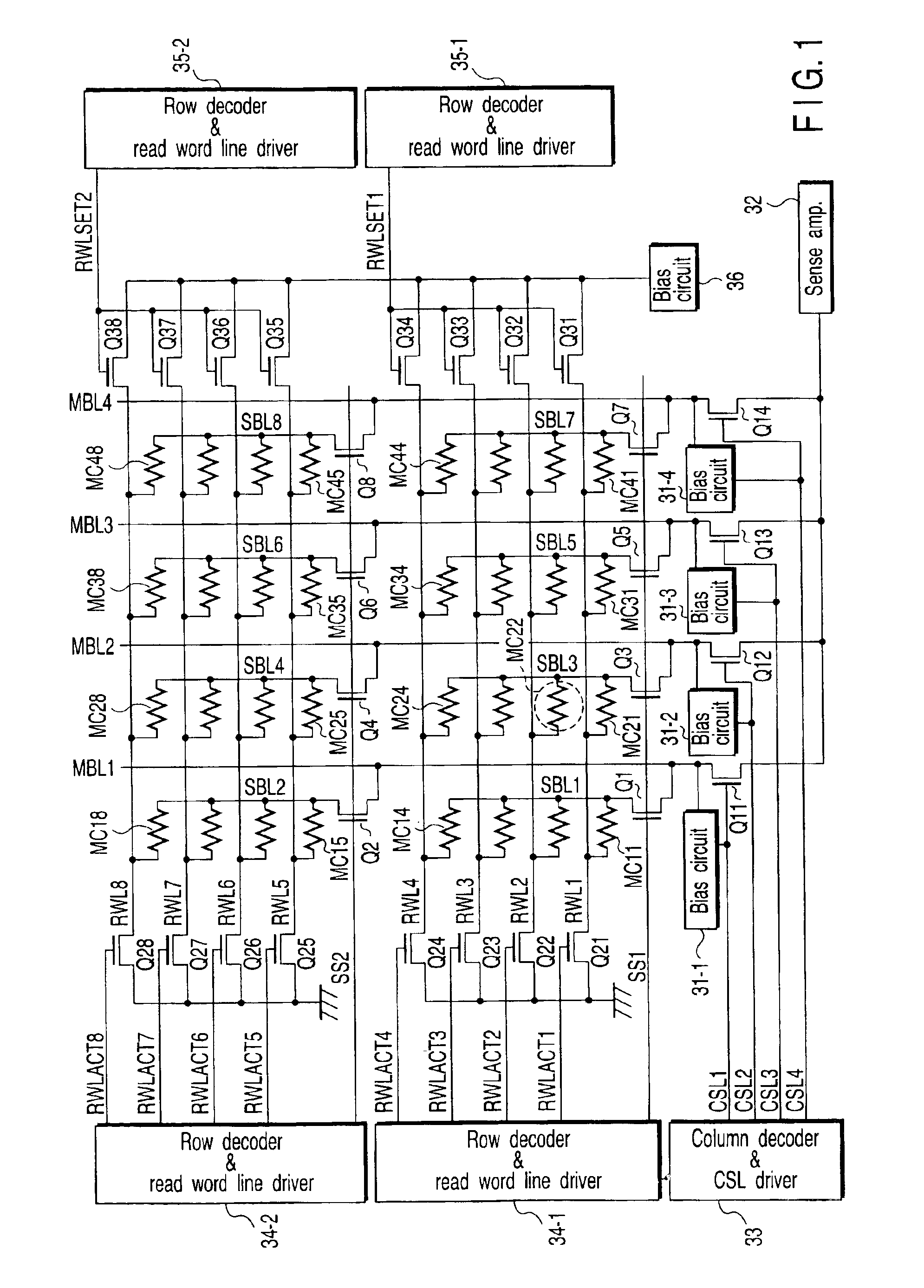

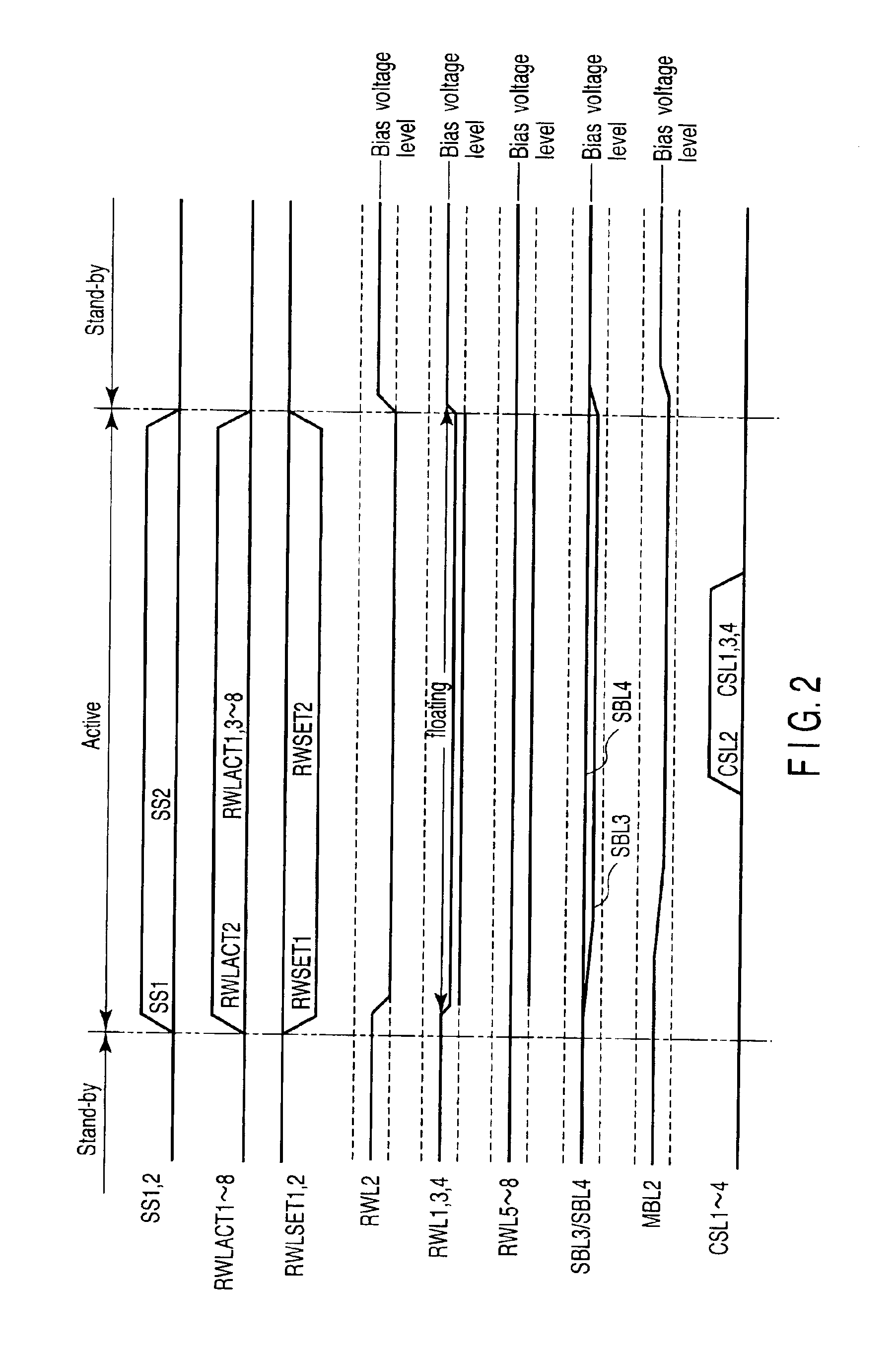

[0031]FIG. 1 is a block diagram showing the main part of a magnetic random access memory (MRAM) according to the first embodiment of the present invention. The present invention is related to a read operation. For the sake of simplicity, FIG. 1 shows the core portion of the read system and does not illustrate the core portion of the write system. Cross-point memory cells MC11 to MC48 each constructed by an MTJ element are arranged in a plurality of (two) memory cell blocks (cell units). One terminal of each to cross-point memory cells MC11 to MC14, MC21 to MC24, MC31 to MC34, and MC41 to MC44 in the first memory cell block is connected by fours to a corresponding one of sub bit lines SBL1, SBL3, SBL5, and SBL7 serving as common nodes. One terminal of each cross-point memory cells MC15 to MC18, MC25 to MC28, MC35 to MC38, and MC45 to MC48 in the second memory cell block is connected by fours to a corresponding one of sub bit lines SBL2, SBL4, SBL6, and SBL8 serving ...

second embodiment

[Second Embodiment]

[0047]FIG. 3 is a block diagram showing the schematic structure of an MRAM according to the second embodiment of the present invention. The same reference numerals as in FIG. 1 denote the same parts in FIG. 3, and a detailed description thereof will be omitted. The second embodiment is different from the first embodiment in that a row decoder & read word line driver is arranged only at one end of each of read word lines RWL1 to RWL8, though the row decoders & read word line drivers are arranged at two ends in FIG. 1.

[0048]To implement this circuit scheme, selection circuits 37-1 and 37-2 which selectively select the read word lines RWL1 to RWL4 and RWL5 to RWL8 to a bias circuit 36 for each cell unit are arranged. The selection circuit 37-1 is constituted by NMOS transistors Q41 to Q44 each of which has a current path having one end connected to a corresponding one of the read word lines RWL1 to RWL4 and the other end commonly connected to the output terminal of t...

third embodiment

[Third Embodiment]

[0051]FIG. 5 is a block diagram showing the schematic structure of an MRAM according to the third embodiment of the present invention. In the third embodiment, a row decoder & read word line driver is arranged only at one end of each of read word lines RWL1 to RWL8, as in FIG. 3, though the row decoders & read word line drivers are arranged at two ends in FIG. 1. Selection circuits 39-1 and 39-2 are formed from PMOS transistors Q51 to Q54 and Q55 to Q58 to directly supply gate signals (signals that are transferred through select lines SS1 and SS2 to selectively connect sub bit lines to main bit lines) to the MOS transistors Q51 to Q54 and Q55 to Q58.

[0052]FIG. 6 is an operation timing chart in the third embodiment. The basic operation is the same as in the first and second embodiments except that the gate signals (the potentials of the select lines SS1 and SS2) are used for the operation of selectively connecting the read word lines RWL1 to RWL4 and RWL5 to RWL8 to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More