Apparatus and method for inspecting semiconductor device

a semiconductor and apparatus technology, applied in semiconductor/solid-state device testing/measurement, instruments, computing, etc., can solve the problems of difficult to measure the performance of analog circuits alone, the semiconductor device is judged to be defective, and the rank sorting cannot be performed in the above manner before shipping, so as to reduce the cost of semiconductor products and yields.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

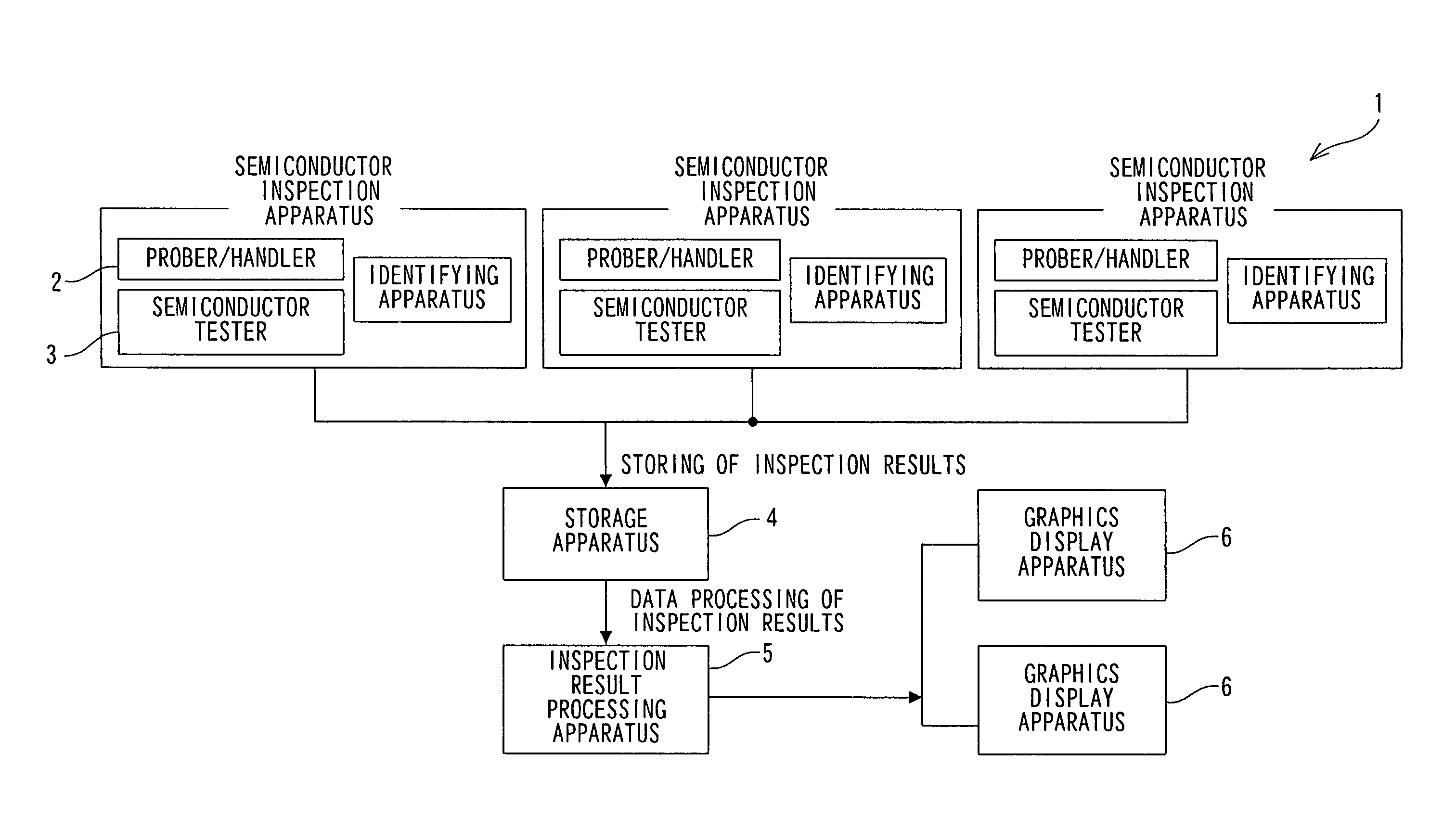

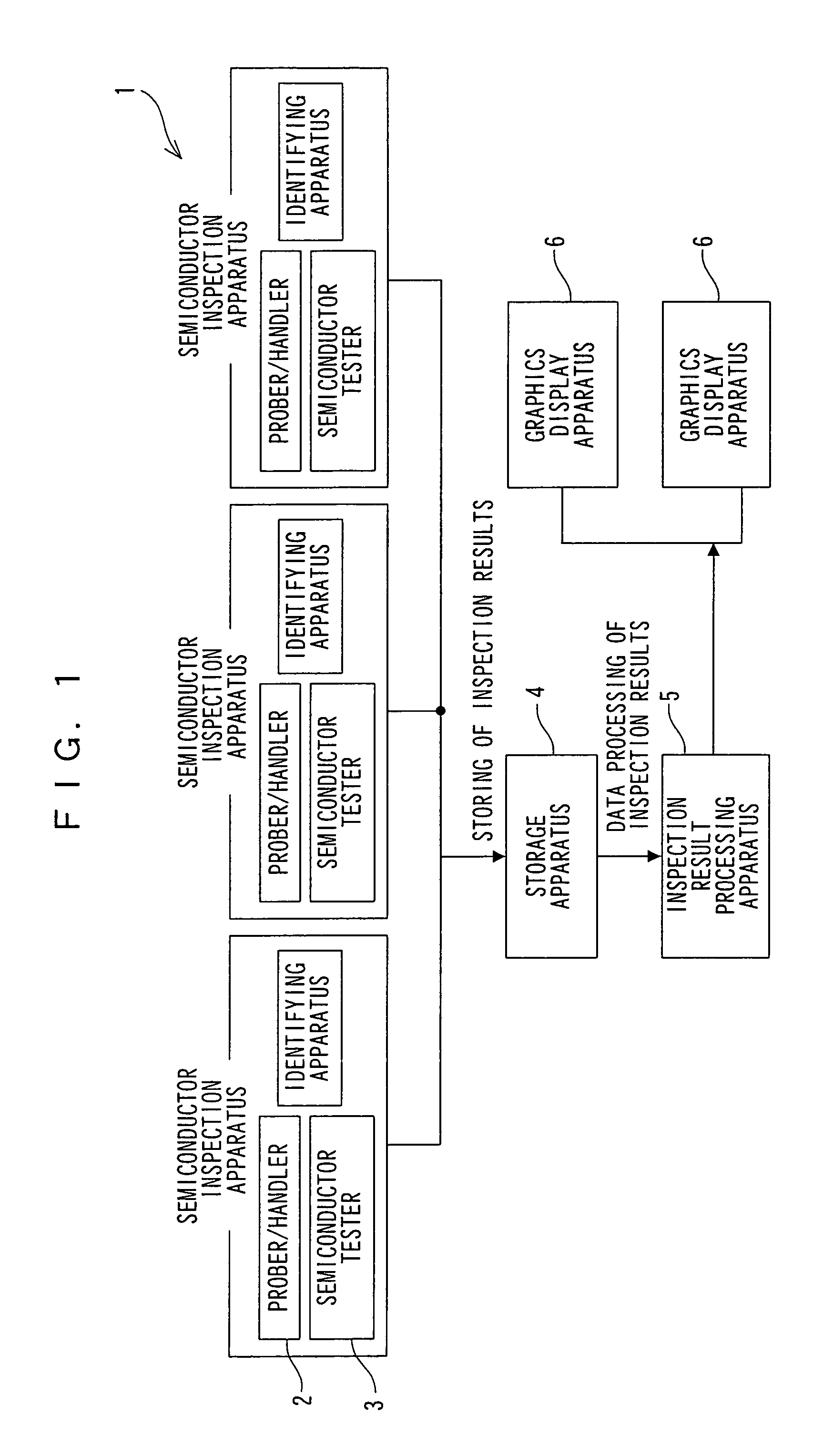

[0033]An embodiment of the present invention will be described below in accordance with the accompanying drawings. FIG. 1 is a schematic diagram showing the configuration of the present invention. A semiconductor inspection apparatus 1 comprises a so-called wafer prober or a handler 2. Generally a prober is used before a semiconductor wafer is split, and a handler is used after a semiconductor wafer is split (after packaging and sealing). A semiconductor tester 3 is a machine for inspecting electrical characteristics of a semiconductor product. Various kinds of semiconductor testers are available.

[0034]In order to use the semiconductor inspection apparatus 1 and the semiconductor tester 3 in the present invention, it is necessary to transmit inspection results on electrical characteristics to a host computer and the like via a communication line. The semiconductor tester 3 in recent years can transmit inspection results via a communication line in most cases.

[0035]The prober 2 which...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical characteristic | aaaaa | aaaaa |

| shape | aaaaa | aaaaa |

| electrical characteristics | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More