Echo canceller and compression operators cascaded in time division multiplex voice communication path of integrated access device for decreasing latency and processor overhead

a technology of voice communication path and echo canceller, which is applied in the field of communication system and subsystem, can solve the problems of consuming a large amount of power, and relative cost of the digital signal processor, and achieve the effect of avoiding burdening the host processor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

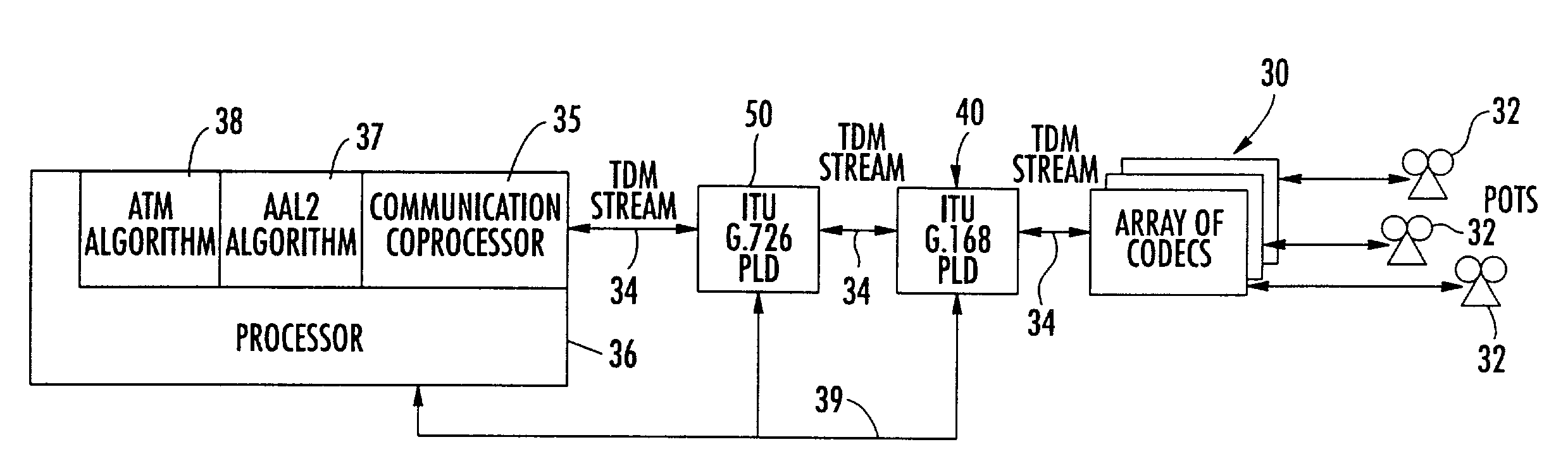

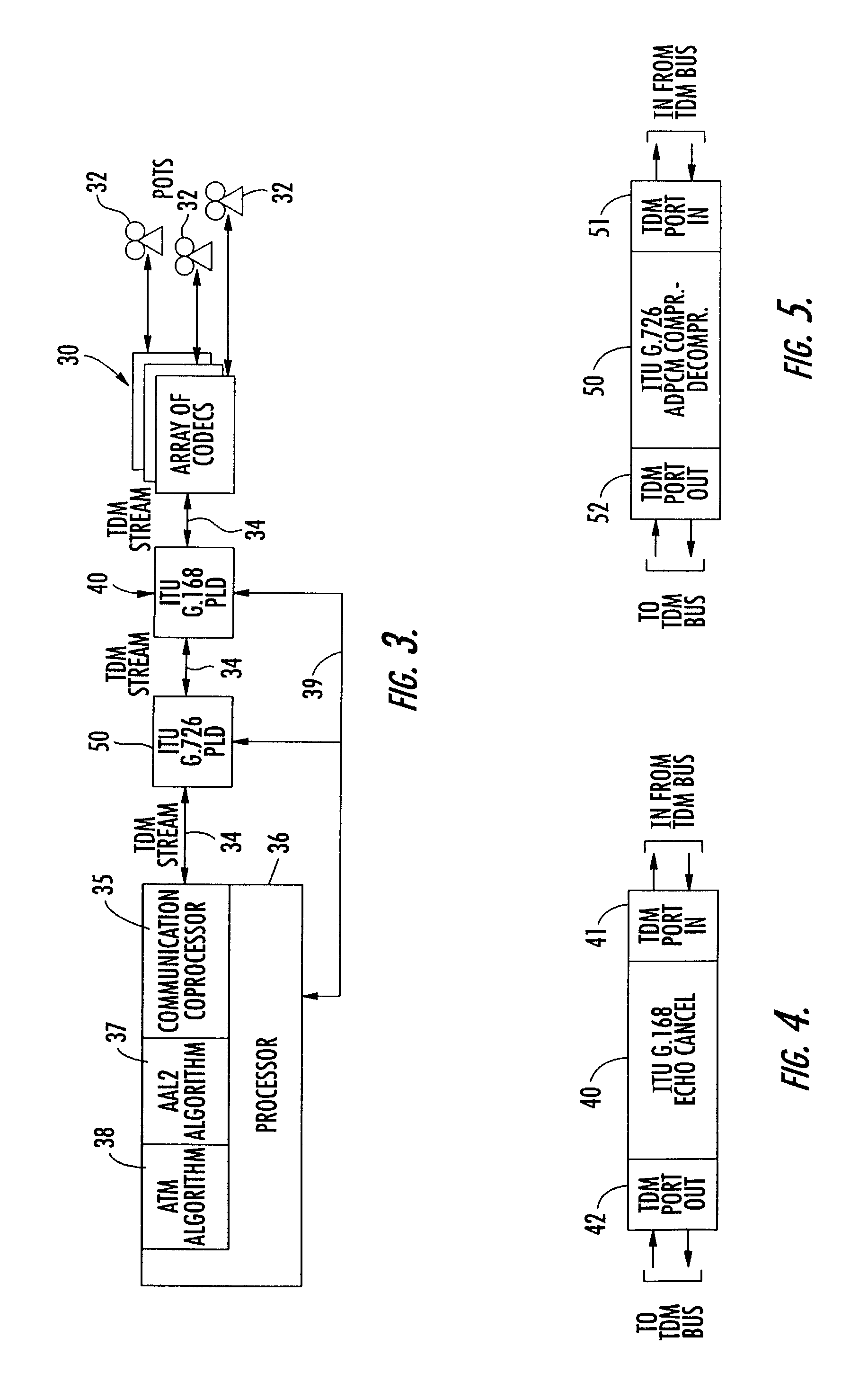

[0013]Before detailing the TDM transport path-cascaded echo canceller and compression arrangement of the present invention, it should be observed that the invention resides primarily in a prescribed arrangement of conventional communication hardware components and attendant supervisory communications microprocessor circuitry and application software therefor, that controls the operations of such components. In a practical implementation that facilitates its incorporation into telecommunication transceiver equipment (such as that which may be installed at a customer premises-associated integrated access device), the invention may be readily implemented using field programmable gate array (FPGA) or application-specific integrated circuit (ASIC) chip sets. In terms of a practical hardware implementation of such chip sets, digital ASICs are preferred.

[0014]Consequently, the configuration of such subsystems and components and the manner in which they may be interfaced with a telecommunic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More