Data latch with structural hold

a data latch and structure technology, applied in the field of electromechanical circuits, can solve the problems of increased system complexity, b and c clocks are both high-speed clocks which toggle, and serial scan register chains are susceptible to hold violations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

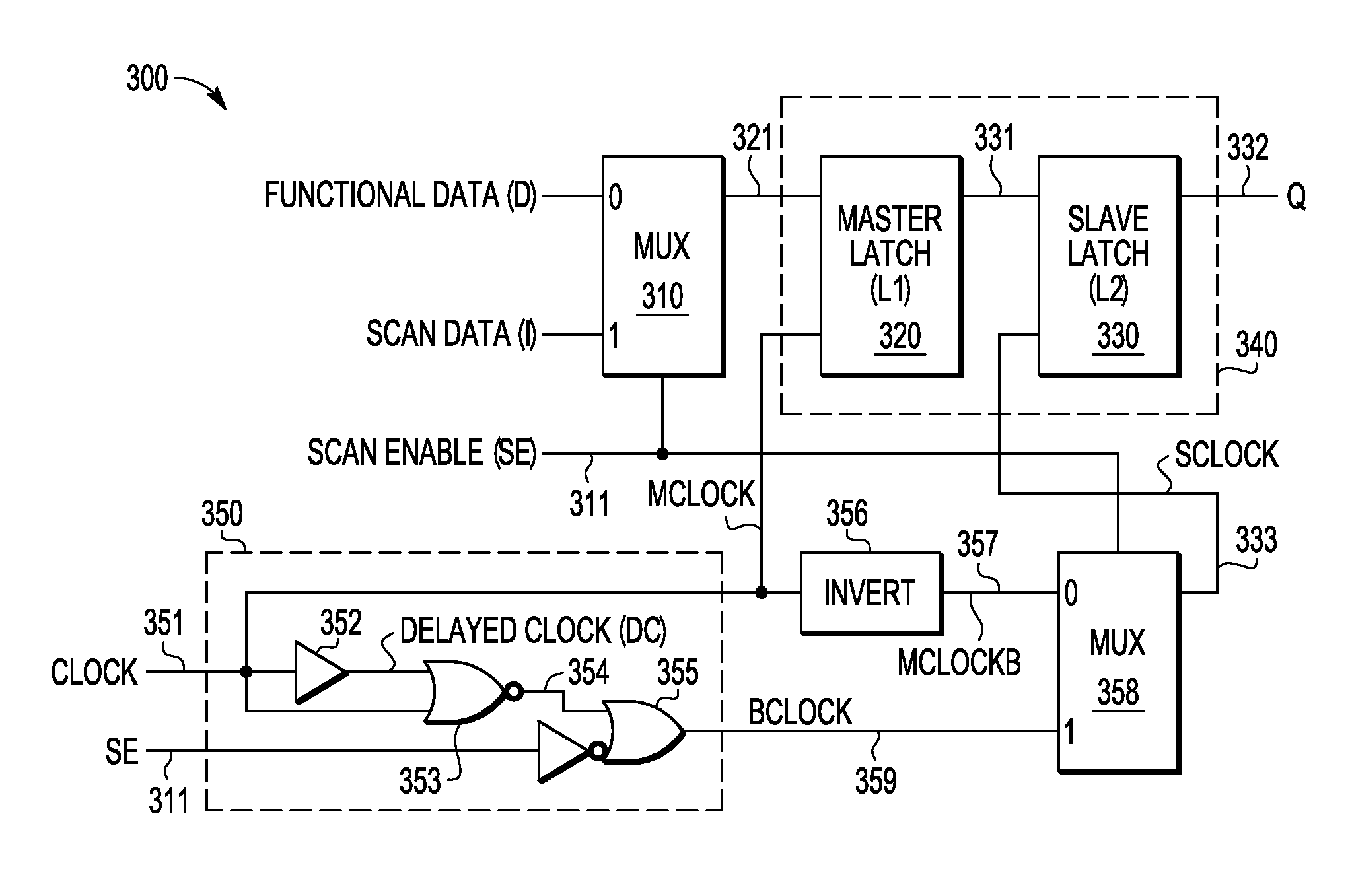

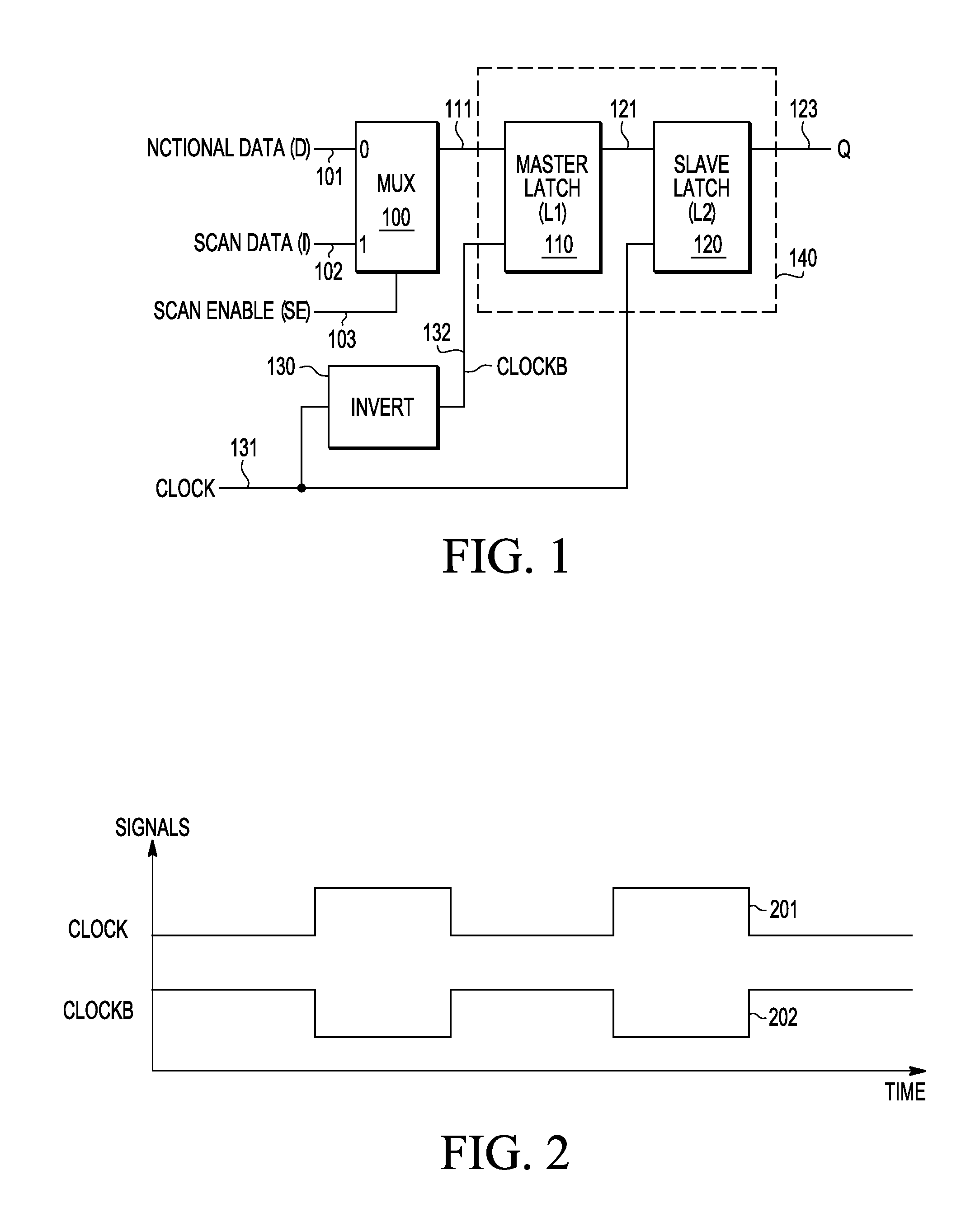

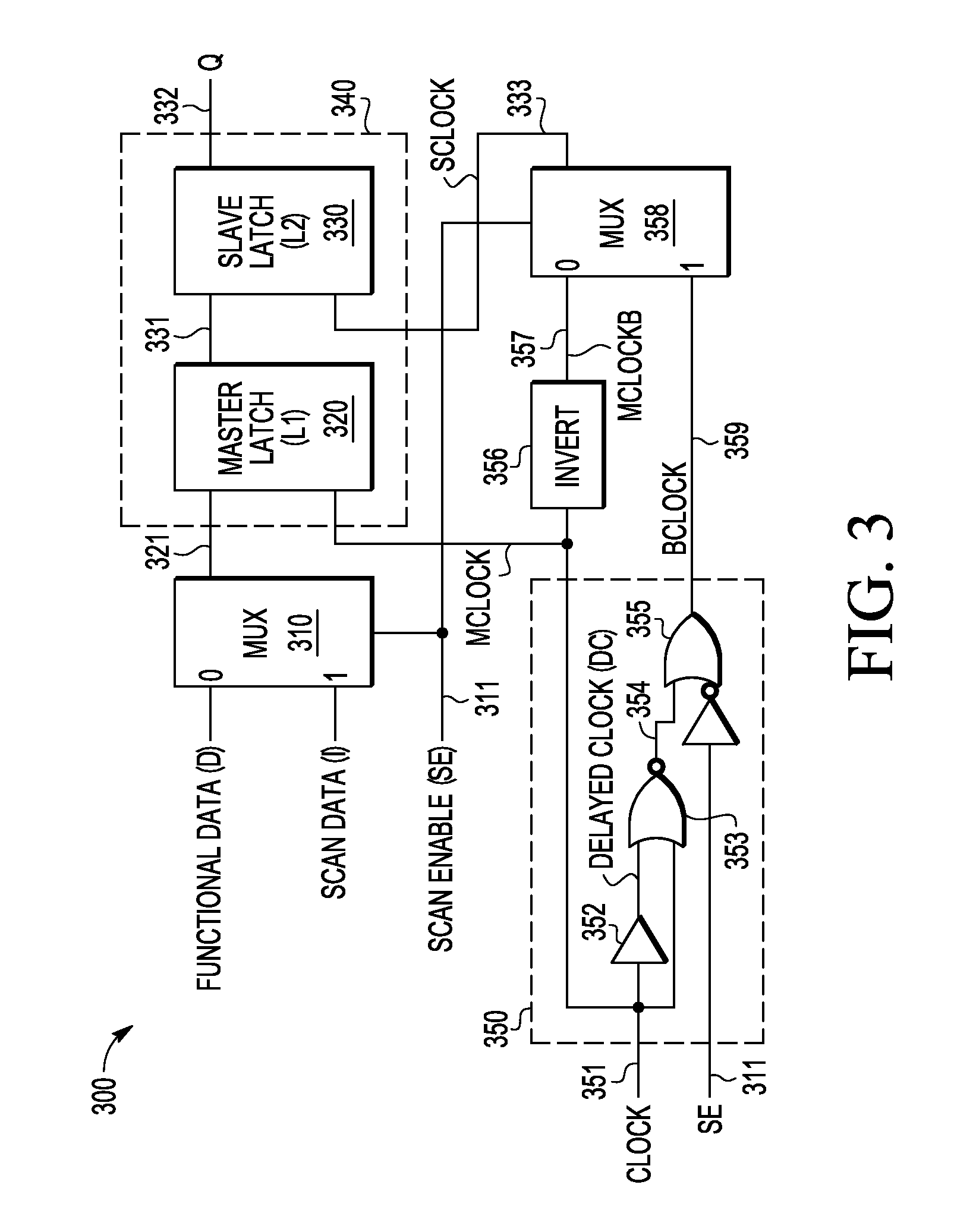

[0021]A multiplexed flip-flop with built-in structural hold and associated methodology of operation are described in connection with a separately clocked multiplexed data flip-flop which provides a Mux-D flip-flop behaviour during the functional mode and LSSD behaviour during the scan mode. To this end, an input clock signal that used for both functional and scan modes is used to generate a second clock that is a DC state during the functional mode and that switches during the scan mode. In the described embodiments, such an approach eliminates the need for hold buffers to fix hold violations in the scan path. In selected embodiments, the input clock signal and its inverse are applied to clock the master and slave latches during functional mode, but during scan mode, the input clock signal is used to generate a separate slave clock such that launch of the slave latch is substantially delayed with respect to the data capture by the master latch. In other embodiments, the input clock ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More