Thermally enhanced semiconductor package

a technology of semiconductors and packaging, applied in the direction of semiconductor devices, semiconductor/solid-state device details, semiconductor devices, etc., can solve the problems of increasing the thermal stress on the chip, reducing the reliability reducing the thermal performance of the integrated circuit, so as to improve the thermal package structure and methods.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

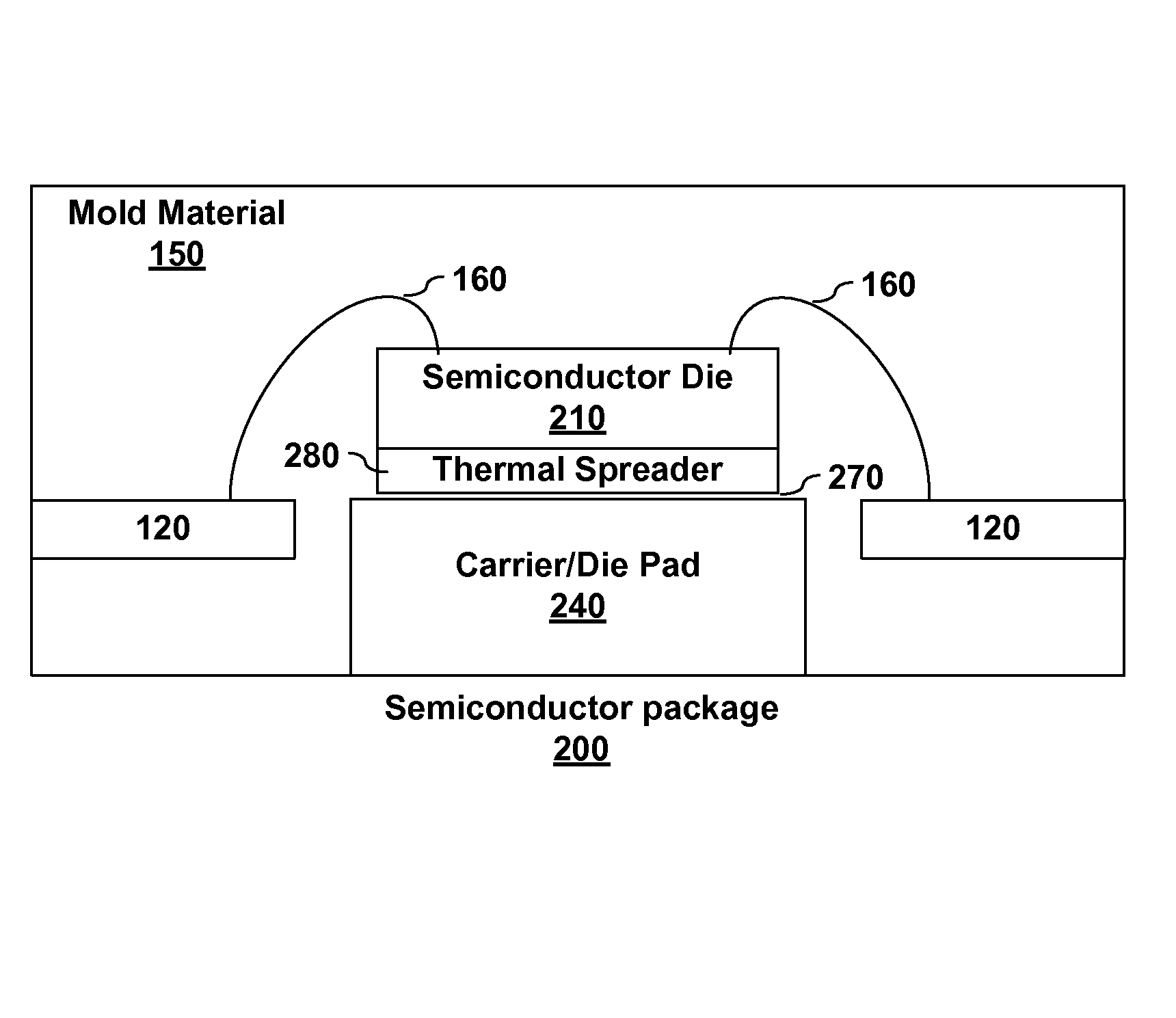

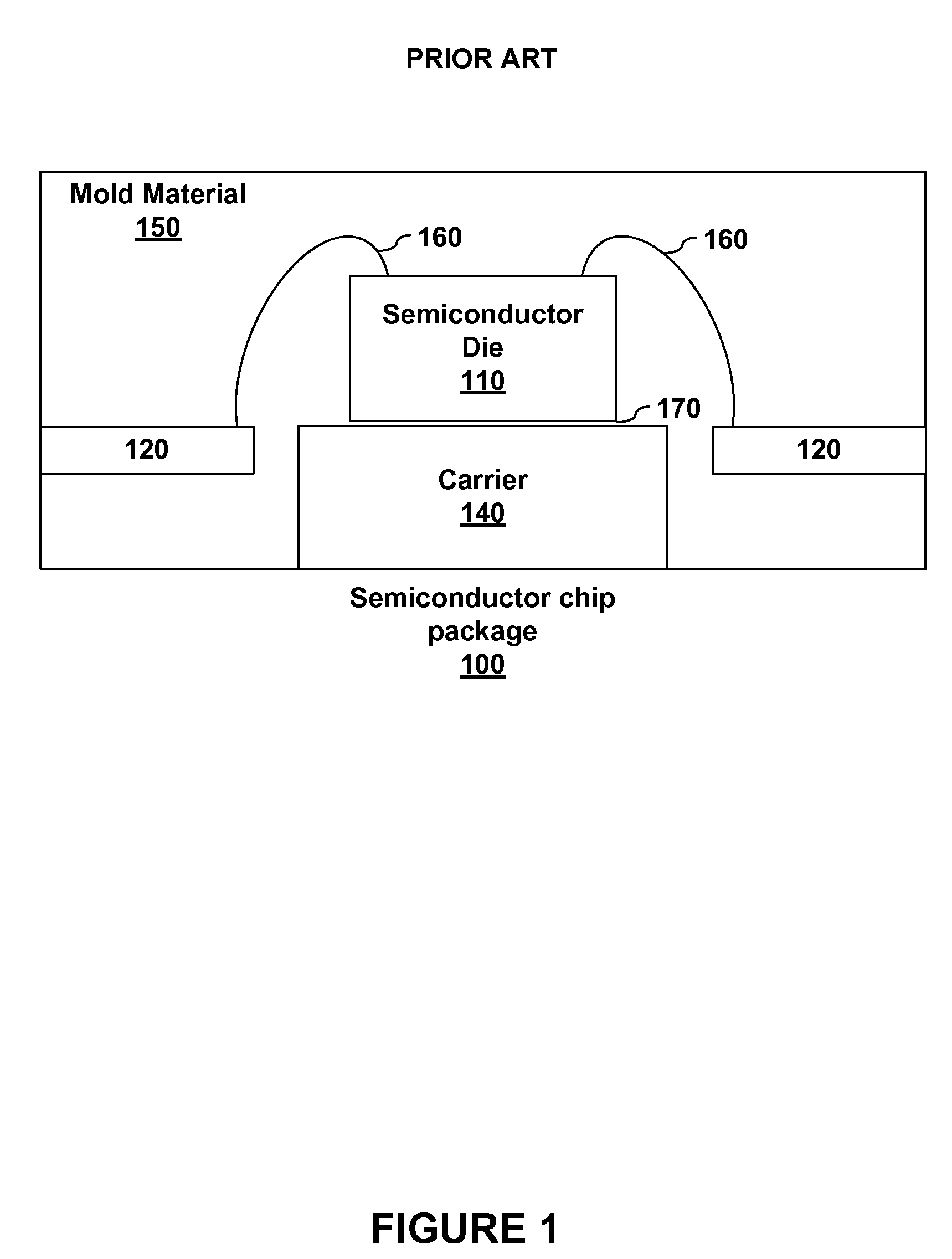

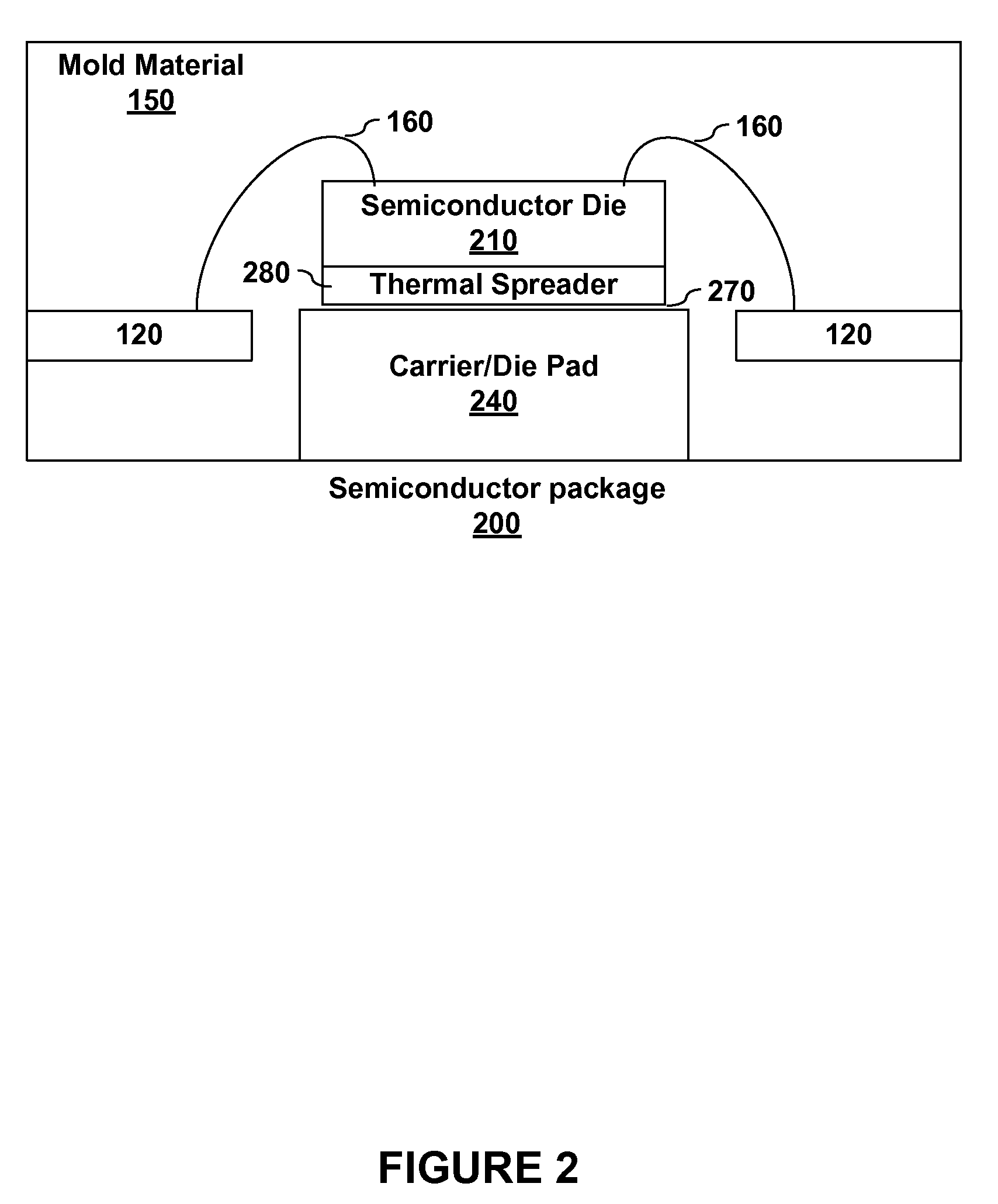

Embodiment Construction

[0028]In the following description, for purpose of explanation, specific details are set forth in order to provide an understanding of the invention. It will be apparent, however, to one skilled in the art that the invention may be practiced without these details. One skilled in the art will recognize that embodiments of the present invention, some of which are described below, may be incorporated into a number of different systems and devices.

[0029]Components shown in block diagrams are illustrative of exemplary embodiments of the invention and are meant to avoid obscuring the invention. It shall also be understood that throughout this discussion that components may be described as separate units, which may comprise sub-units, but those skilled in the art will recognize that, in embodiments, the various components, or portions thereof, may be divided into separate components or may be integrated together.

[0030]Furthermore, connections between components within the figures are not i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More