High-speed, low power, medium resolution analog-to-digital converter and method of stabilization

a technology of analog-to-digital converter and medium resolution, applied in the field of analog-to-digital converter, can solve the problems of large integrated circuit area, high power consumption, and increase of all such requirements, and achieve the effect of cancelling out input offset voltages

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

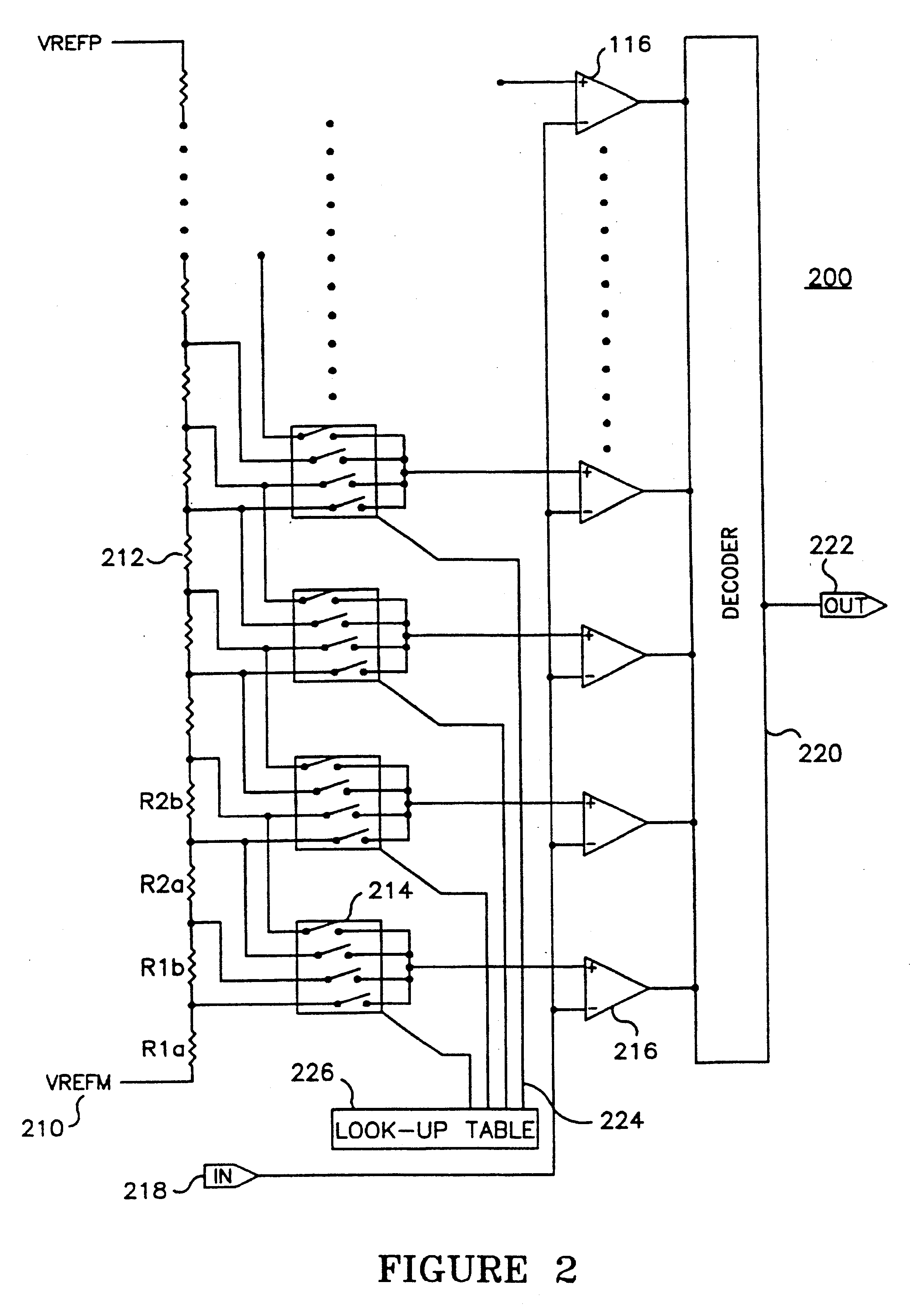

FIG. 2 is a block diagram of a calibrated analog-to-digital converter ("ADC") 200 having four choices of reference voltage per comparator derived from a reference voltage input 210. A number of resistors, of which resistor 212 is exemplary, are coupled in series to the reference voltage 210. A number of switching circuits, of which switching circuit 214 is exemplary, are coupled to junctions of resistors 212 to apply selected ones of four different voltages to a reference input of each comparator 216. The output of each switching circuit 214 is coupled to an associated comparator, of which comparator 216 is exemplary. In addition, each comparator 216 receives an input voltage appearing on input 218. A conventional decoder 220 receives the outputs of the comparators 216 and produces a digital output 222 representation of the voltage appearing on input 218.

The embodiment of a full flash ADC 200 illustrated in FIG. 2 includes an array of comparator 216 arranged to receive associated re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More