Production method of high voltage MOS transistor

A technology of a MOS transistor and a manufacturing method is applied in the manufacture of high-voltage MOS transistors, the manufacture of high-voltage MOS transistors, and the field of preventing double-peak effects, which can solve the problems of reduced gate oxide threshold voltage, poor device stability, and high device power consumption. Effect of device power consumption, increased stability, and avoidance of double peaks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

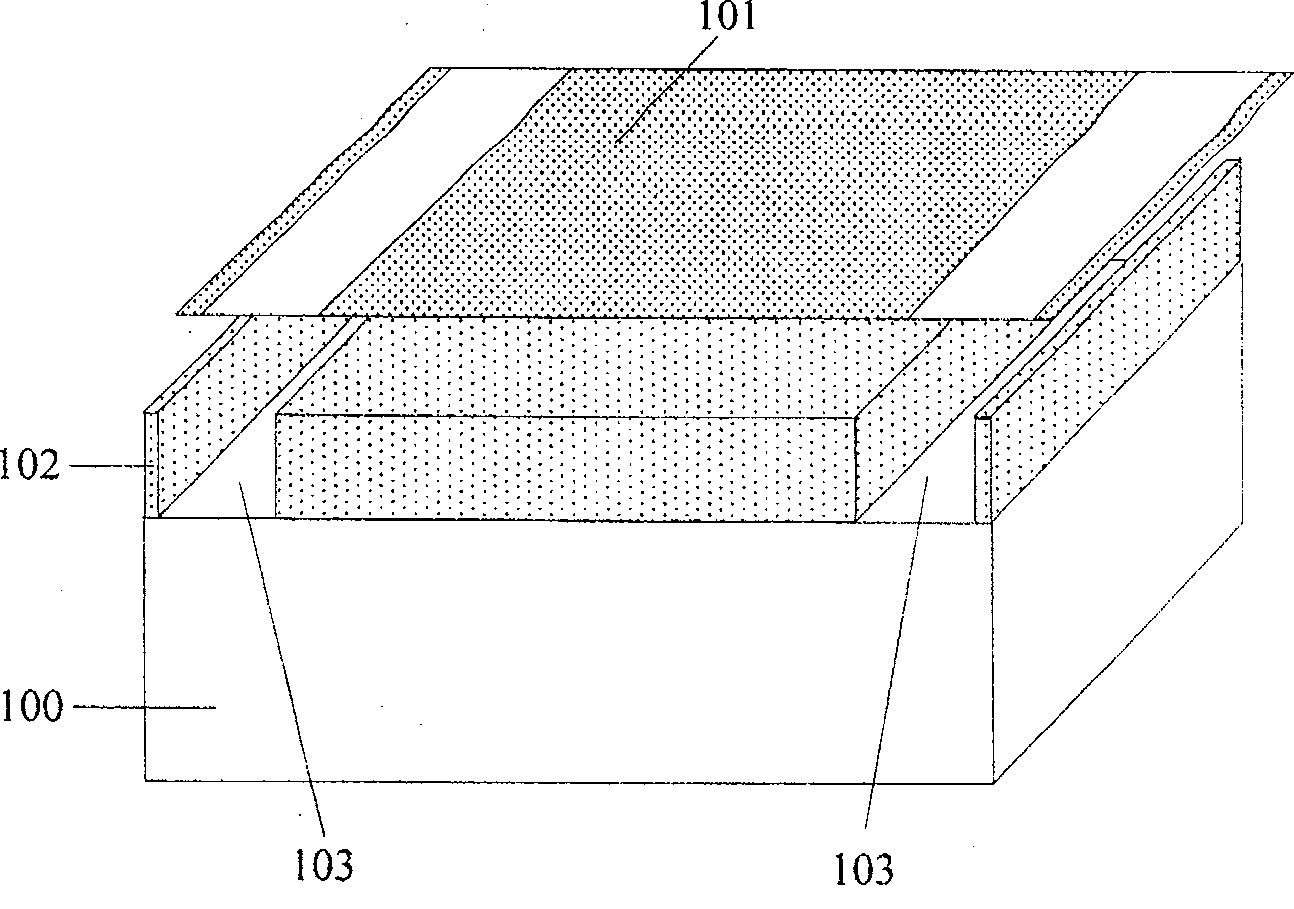

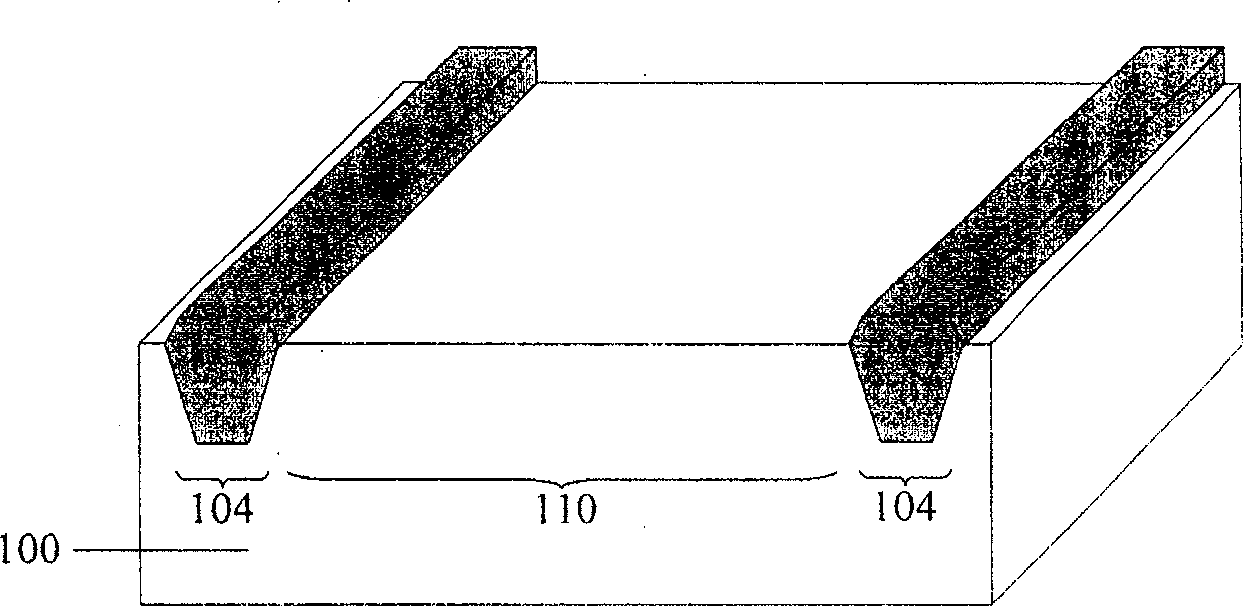

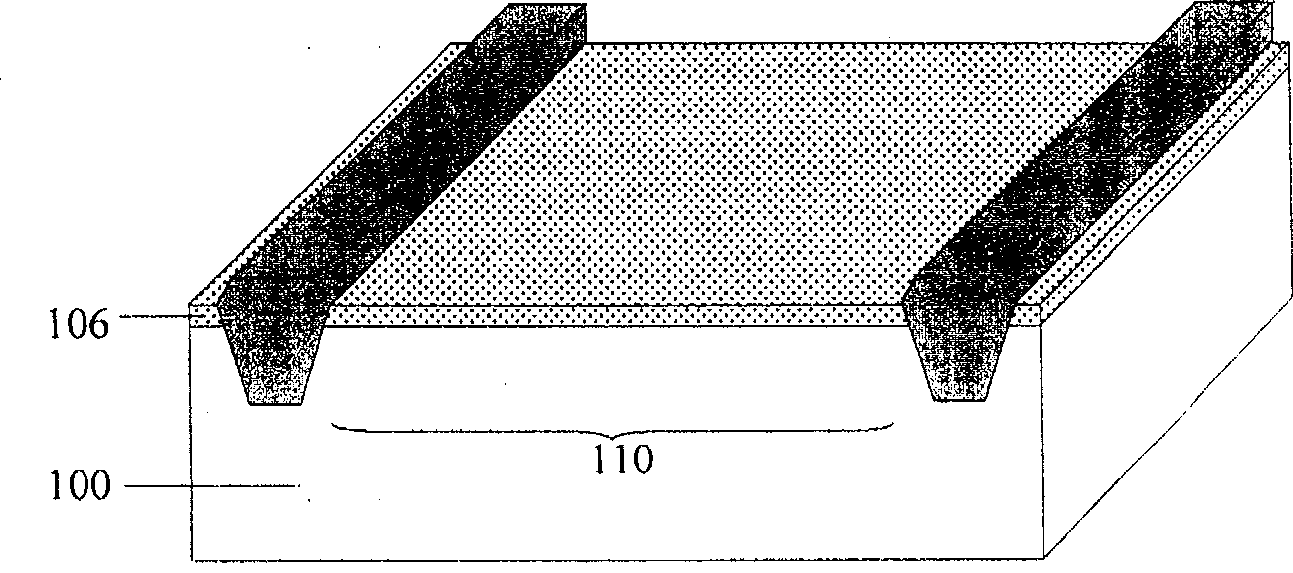

[0030] In the existing process of manufacturing the gate oxide layer of the MOS transistor, since the gate oxide layer of the high-voltage MOS transistor is relatively thick and is affected by the chamfering of the shallow trench isolation region, and is affected by the chamfering of the shallow trench isolation region, the formation of the gate oxide layer During the process, it is easy to cause the edge part of the gate oxide layer to be thinner than the middle part, resulting in a decrease in the threshold voltage at the edge of the gate oxide layer, resulting in a double peak phenomenon, resulting in high power consumption of the device and poor stability of the device operation. In the present invention, in the graphic layout software, an auxiliary active area graphic to be exposed is formed at the junction of the active area graphic to be exposed and the isolated area graphic to be exposed, which is connected with the active area graphic to be exposed and protrudes toward ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More