Method for manufacturing three-dimensional nerve microelectrode

A manufacturing method and micro-electrode technology, which are applied in the directions of micro-structure technology, micro-structure device, manufacturing micro-structure device, etc., can solve the problems of large influence of insulating layer process, unfavorable long-term implantation, easy generation of pinholes, etc., and achieve the production cost. reduction, good electrical uniformity, pinhole elimination effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0025] In this embodiment, the cylindrical hole 8 made of SU-8 glue has a height of 100 micrometers and is used for sticking on the surface of the dura mater of the optic nerve or cerebral cortex to stimulate the optic nerve or cerebral cortex to restore nerve function.

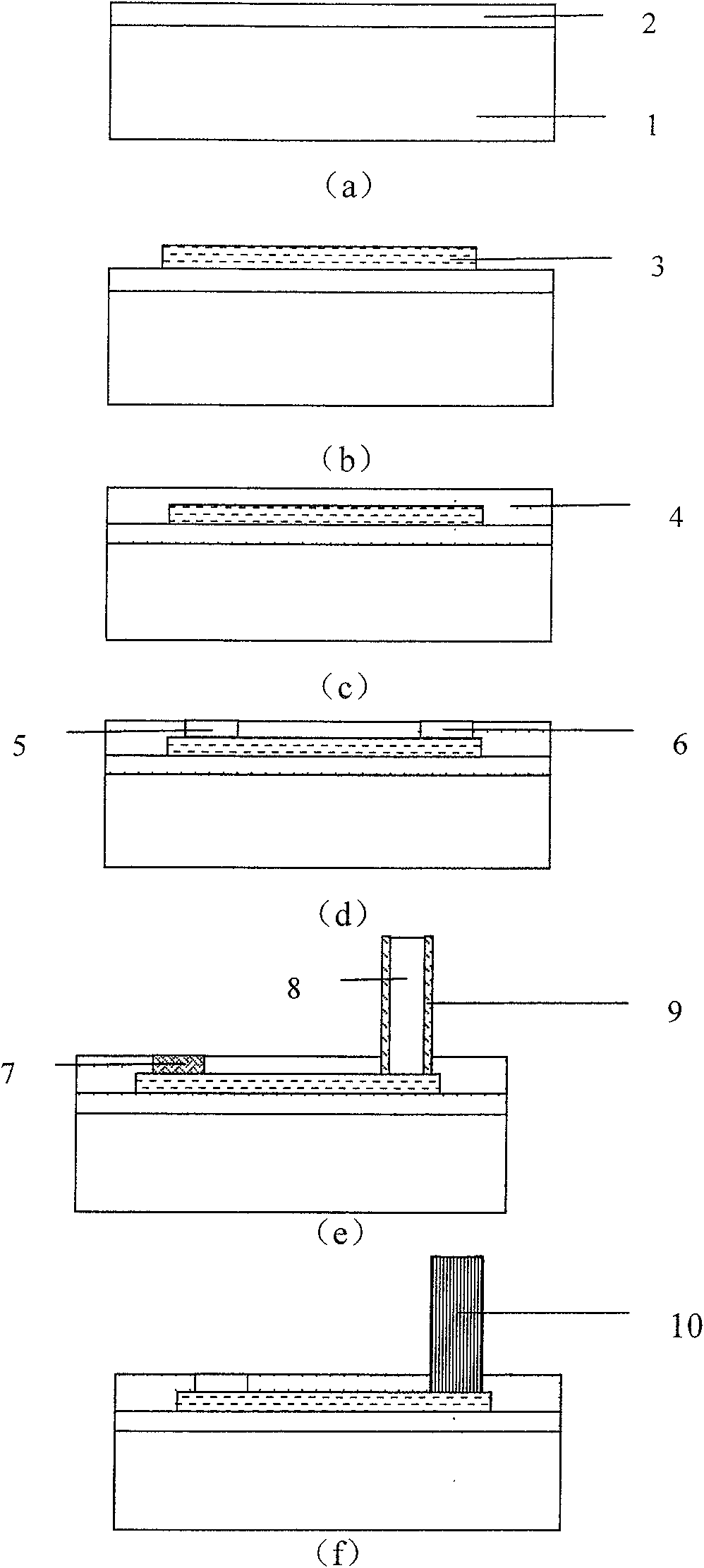

[0026] Such as figure 1 As shown, this embodiment includes the following steps:

[0027] Step 1, clean the silicon wafer 1, use the silicon wafer 1 as the substrate, and use PECVD (plasma chemical vapor deposition) method to grow the bottom SiO on the polished surface of the silicon wafer 1 2 2. Bottom SiO2 2 2 for electrically isolating the metal alloy layer from the silicon substrate, such as figure 1 (a) shown.

[0028] The silicon wafer 1 is N-type single crystal silicon.

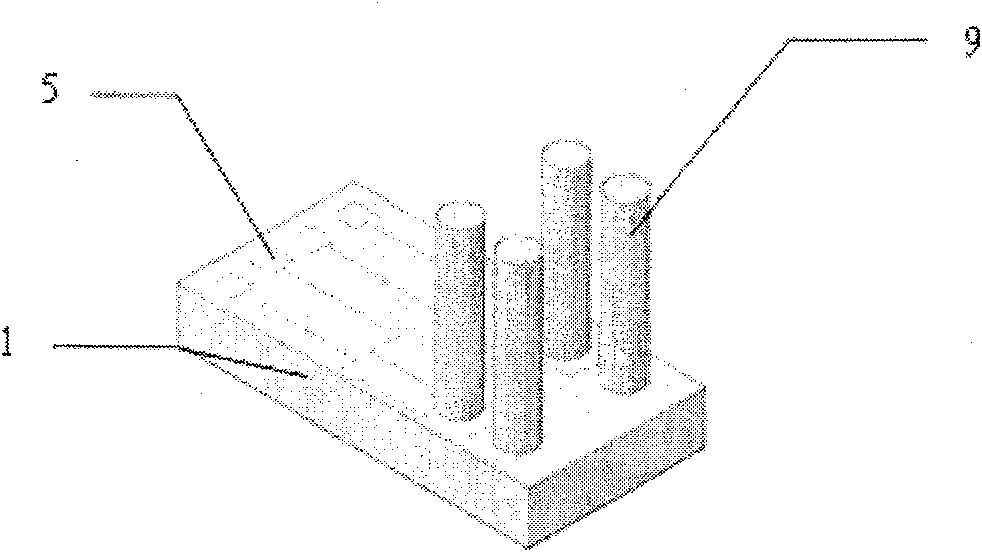

[0029] Step 2, on the bottom SiO 2 Metal titanium and gold are sequentially sputtered on 2 to form a metal alloy layer, and metal interconnection lines 3, pads 5 and contact dots 6 are etched out. Dot 6 is used for electroplatin...

Embodiment 2

[0036] In this embodiment, the cylindrical hole 8 made of SU-8 glue has a height of 500 micrometers and is used to penetrate the dura mater and stick on the surface of the pia mater to stimulate the optic nerve or cerebral cortex to restore nerve function.

[0037] Such as figure 1 As shown, this embodiment includes the following steps:

[0038] Step 1, clean the silicon wafer 1, use the silicon wafer 1 as the substrate, and use PECVD (plasma chemical vapor deposition) method to grow the bottom SiO on the polished surface of the silicon wafer 1 2 2. Bottom SiO2 2 2 for electrically isolating the metal alloy layer from the silicon substrate, such as figure 1 (a) shown.

[0039] The silicon wafer 1 is P-type single crystal silicon.

[0040] Step 2, on the bottom SiO 2Metal titanium and gold are sequentially sputtered on 2 to form a metal alloy layer, and metal interconnection lines 3, pads 5 and contact dots 6 are etched out. Dot 6 is used for electroplating to grow cylind...

Embodiment 3

[0047] The height of the cylindrical hole 8 that adopts SU-8 glue to form among the present embodiment is 1 millimeter, is used for penetrating dura mater and pia mater, punctures in optic nerve or cerebral cortex, is used for stimulating optic nerve or cerebral cortex, carries out neural Functional fixes.

[0048] Such as figure 1 As shown, this embodiment includes the following steps:

[0049] Step 1, clean the silicon wafer 1, use the silicon wafer 1 as the substrate, and use PECVD (plasma chemical vapor deposition) method to grow the bottom SiO on the polished surface of the silicon wafer 1 2 2. Bottom SiO2 2 2 for electrically isolating the metal alloy layer from the silicon substrate, such as figure 1 (a) shown.

[0050] The silicon wafer 1 is N-type single crystal silicon.

[0051] Step 2, on the bottom SiO 2 Metal titanium and gold are sequentially sputtered on 2 to form a metal alloy layer, and metal interconnection lines 3, pads 5 and contact dots 6 are etched ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More