Chip data output signal protection method and its circuit

A technology for outputting signals and chips, used in electrical digital data processing, protection of internal/peripheral computer components, instruments, etc., can solve problems such as production difficulties, increased chip costs, and inability to protect codes, achieving no special process requirements and low cost. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

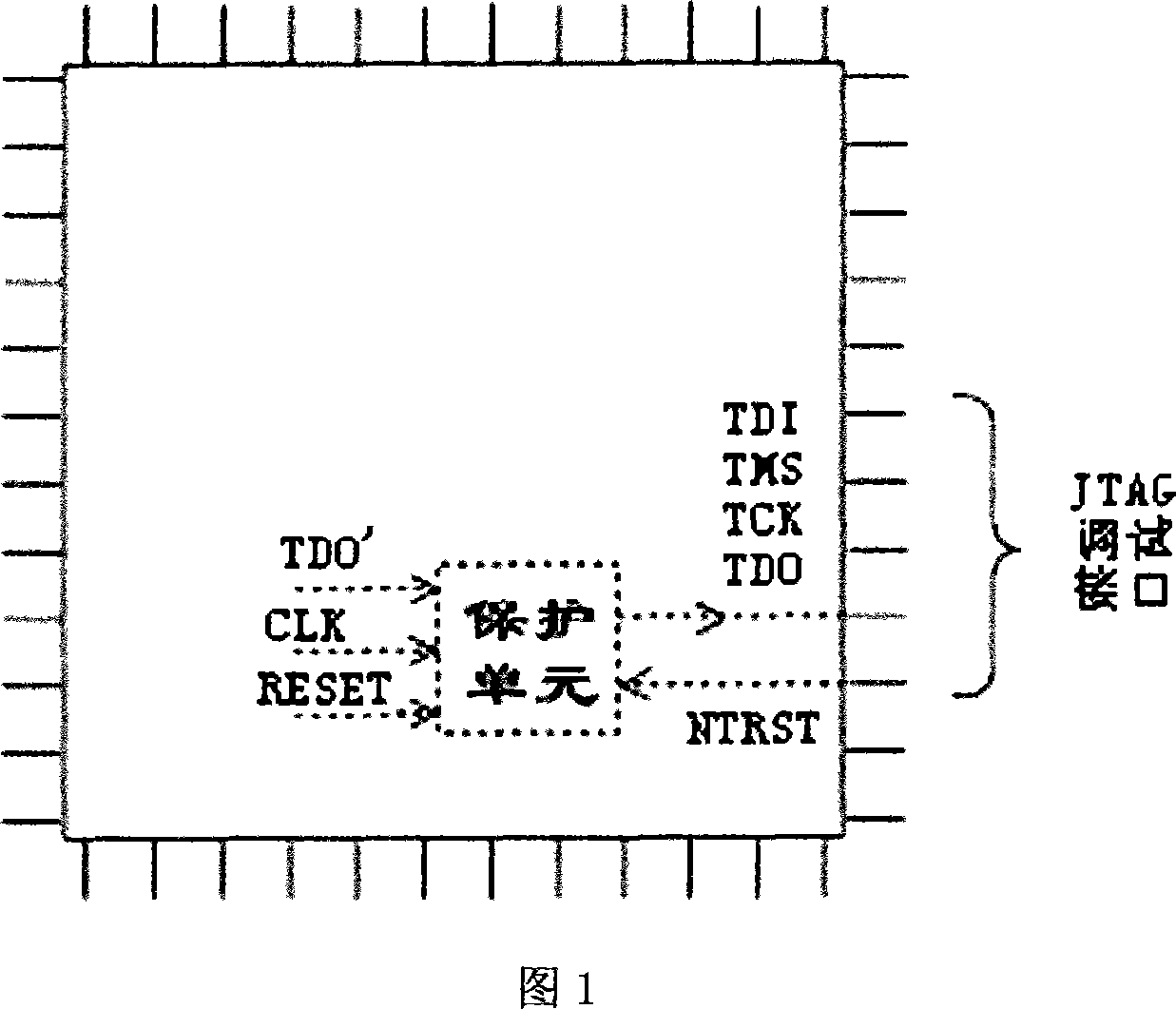

[0014] The present invention will be further described in detail below by taking the JTAG interface as an example in conjunction with the accompanying drawings and specific implementation methods.

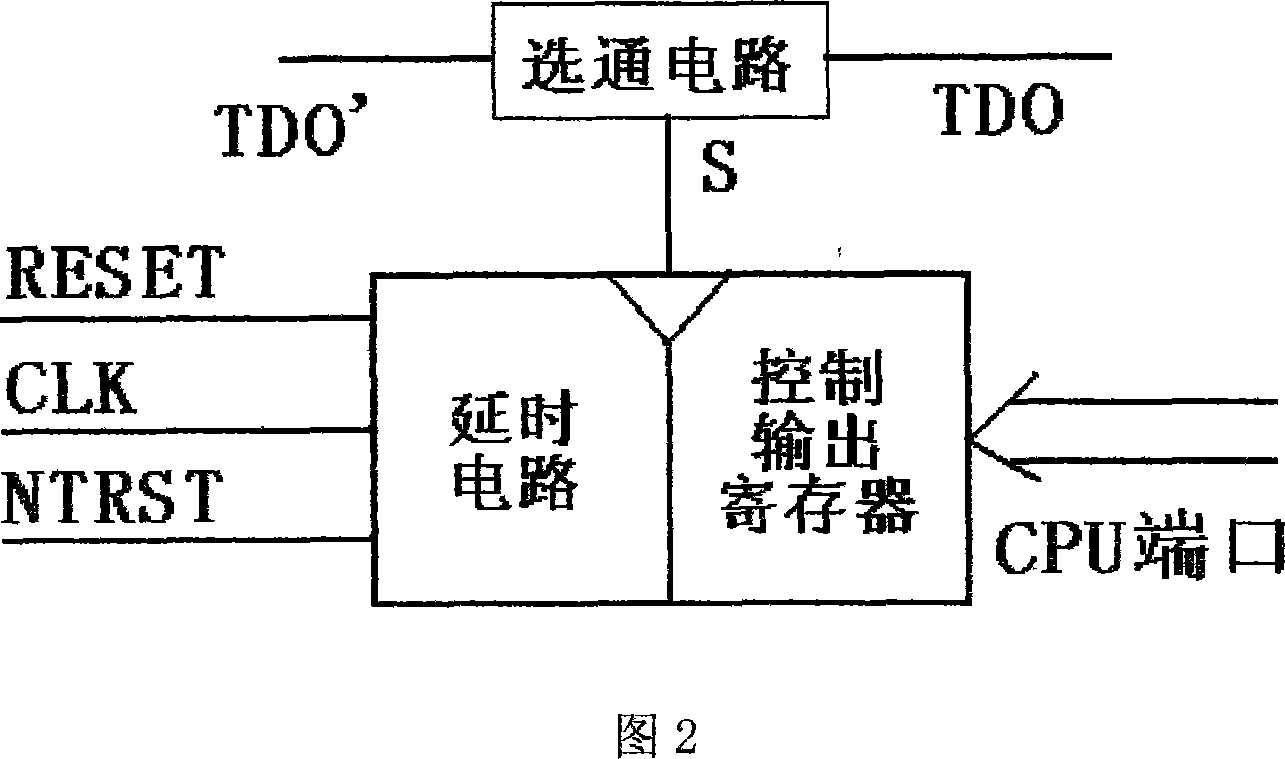

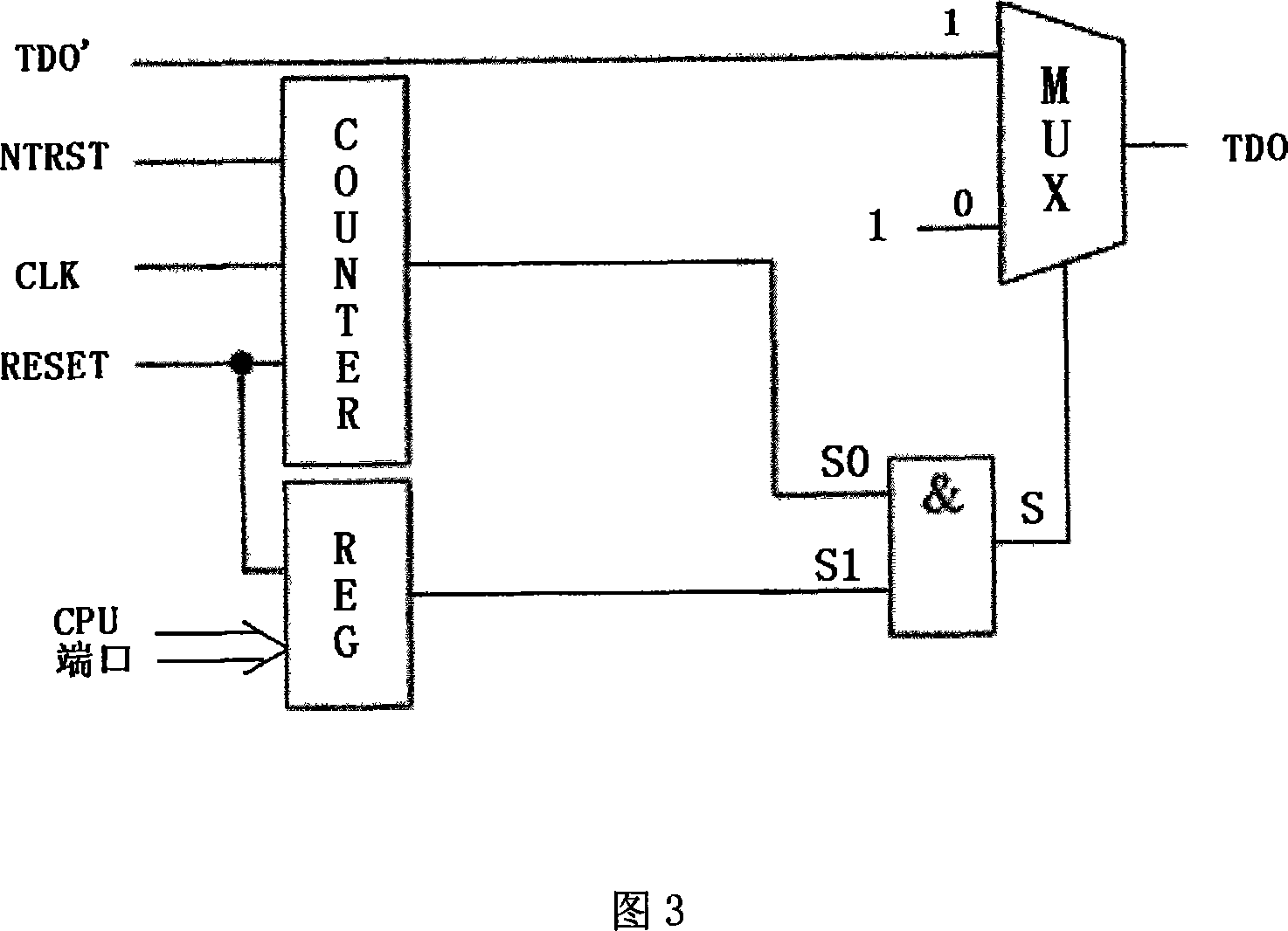

[0015] FIG. 2 is a circuit of the protection unit in FIG. 1 , and FIG. 3 is a specific embodiment of FIG. 2 .

[0016] The JTAG interface mainly has 5 signal lines, which are: test clock input TCK, test data input TDI, test data output TDO, test mode selection TMS, test reset TRST. Among them, TDO is the data output signal of the chip. As long as the signal is controlled, the internal information of the chip can be prevented from being read out. After the chip in the final product is started, the first instruction is to modify the control output register REG to invalidate the test data output TDO output of the JTAG interface, thereby achieving the purpose of protecting the chip code.

[0017] The specific implementation method is:

[0018] Find an empty address in the chip, desig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More