Stack type chip packaging structure, chip packaging structure and manufacture process

A chip packaging structure, packaging structure technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., to achieve the effect of improving integration and saving available space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

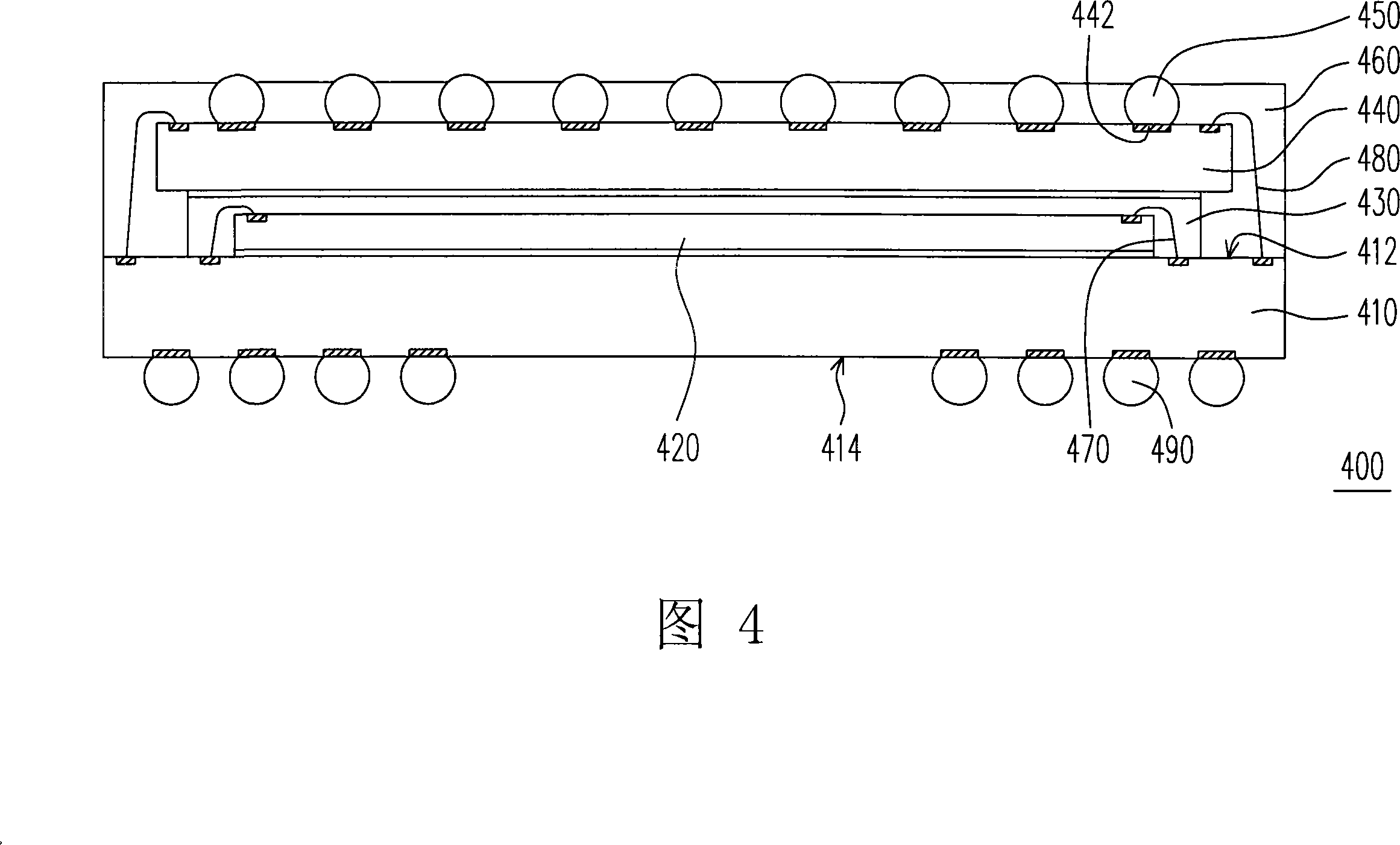

[0031] FIG. 4 is a schematic cross-sectional view of a chip packaging structure according to an embodiment of the present invention. Referring to FIG. 4 , the chip packaging structure 400 of this embodiment includes a carrier 410 , a chip 420 , a first encapsulant 430 , a wiring element 440 , a plurality of conductive elements 450 , and a second encapsulant 460 . The carrier 410 has a carrying surface 412 and an opposite back surface 414 . The chip 420 is disposed on the carrying surface 412 and electrically connected to the carrier 410 . The first encapsulant 430 is disposed on the carrying surface 412 and covers the chip 420 . The wiring element 440 is disposed on the first encapsulant 430 and electrically connected to the carrier 410 , and the wiring element 440 provides a plurality of pads 442 above the surface of the first encapsulant 430 . The conductive elements 450 are respectively disposed on the pads 442 . The second encapsulant 460 covers the carrying surface 412...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More