System and method for testing NVM chip

A chip testing and chip technology, applied in electronic circuit testing, electrical measurement, measuring devices, etc., can solve the problems of inability to test chips at the same time, waste of testing resources, affecting the efficiency of testing, etc., so as to shorten the testing time and speed up the output. , the effect of expanding the ability of co-testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

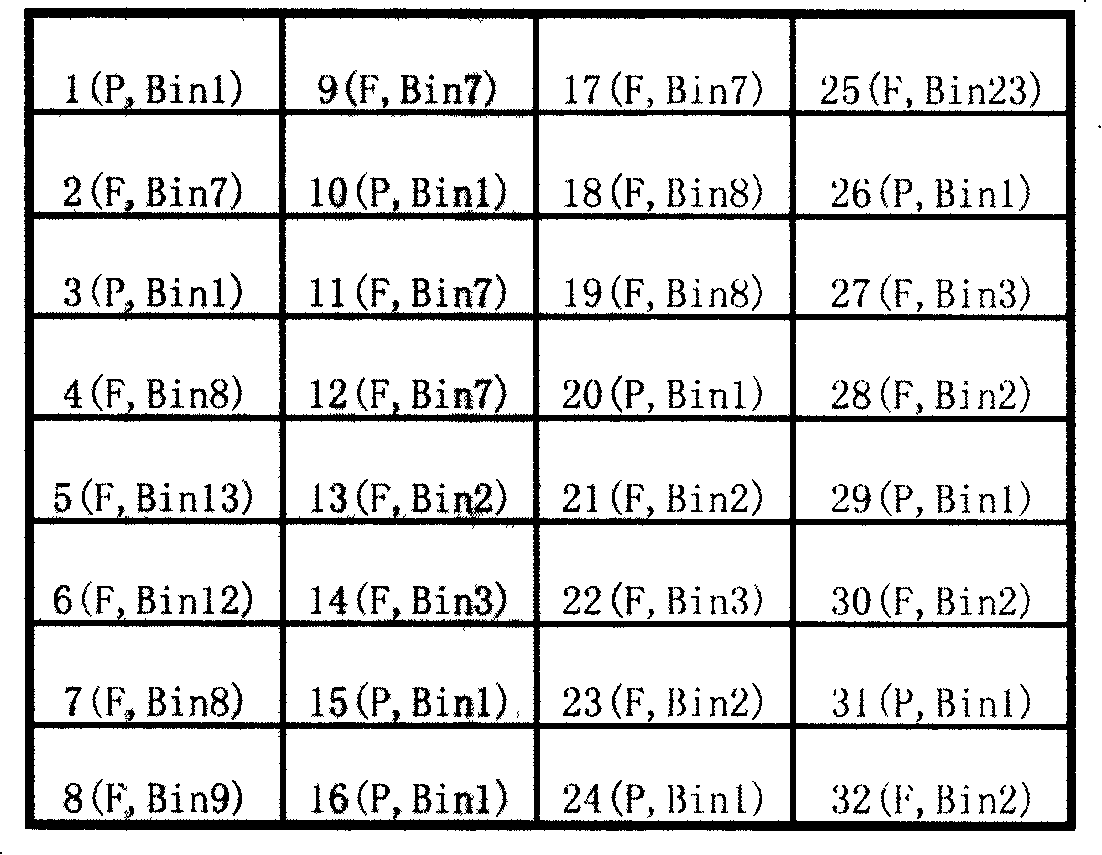

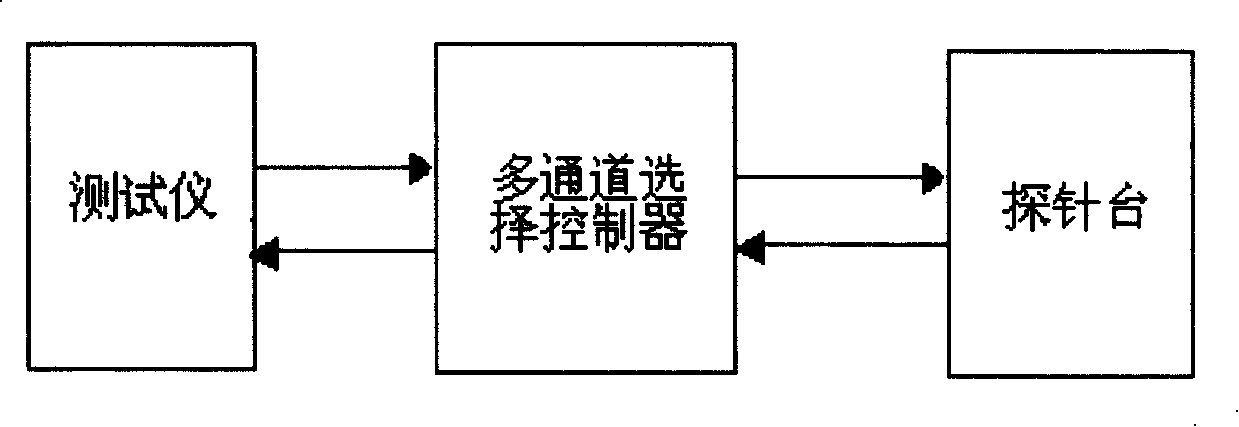

[0017] Such as image 3 As shown, the NVM chip test system of the present invention includes a tester that is connected in sequence and performs signal transmission, a multi-channel selection controller that selects test channels, and a probe station. The tester is connected to the probe station through a multi-channel selection controller that selects the test channel to test the chip. And the multi-channel selection controller of the gating test channel is composed of multiple relays. Such as Figure 4 As shown, before the test channel of the tester is connected to the probe of the probe station, a multi-channel selection controller composed of relays is used, and the multi-channel selection controller selects the test channel during testing.

[0018] Such as Figure 5 As shown, the NVM chip testing method of the present invention includes the following steps: using the NVM chip testing system of the present invention, before the test channel is connected to the probe of the prob...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More