Distributed type testing on-chip network router

A router and distributed technology, applied in data exchange networks, instruments, electrical digital data processing, etc., can solve problems such as limited hardware resources, and achieve the effect of simple hardware structure and high scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

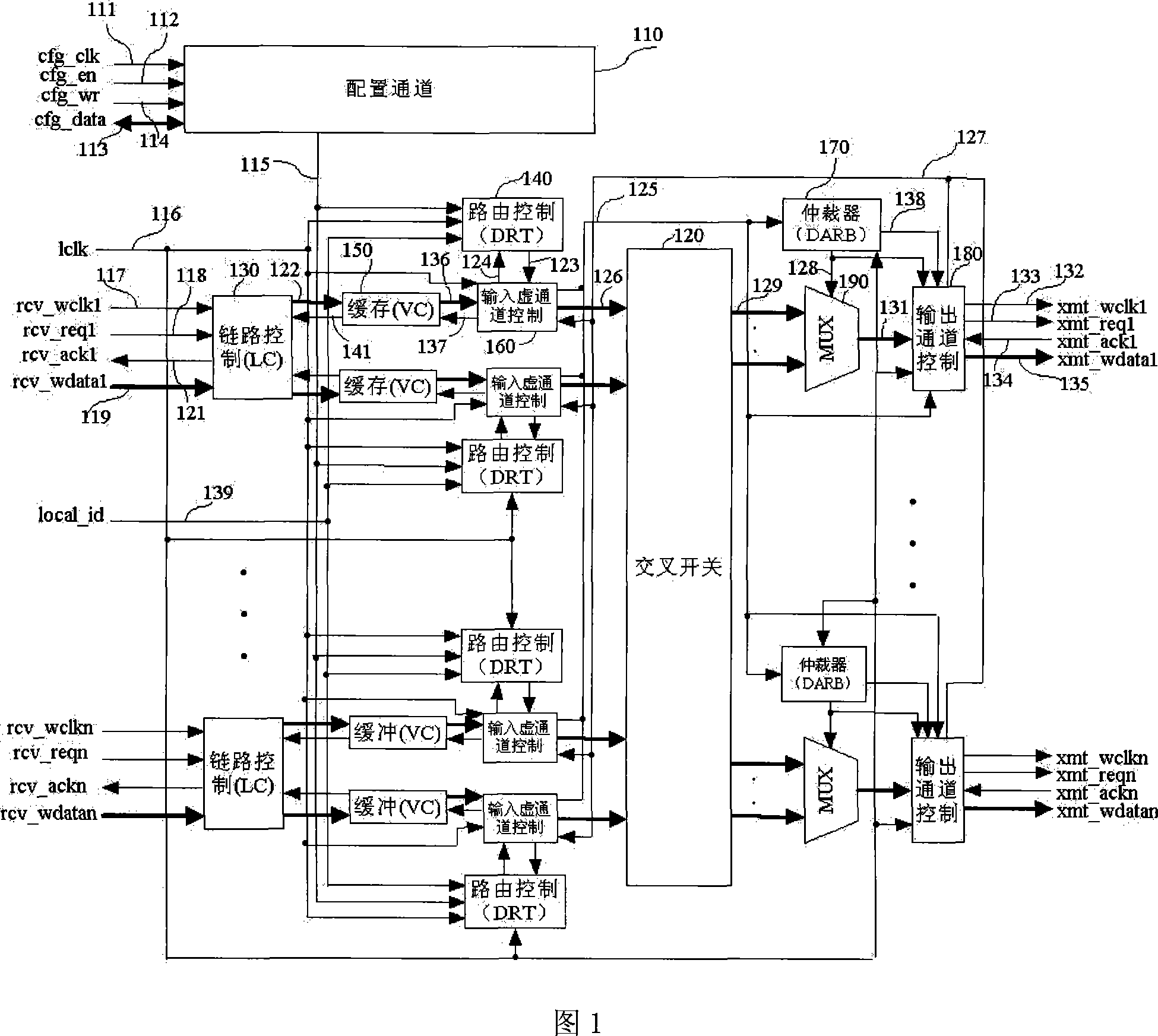

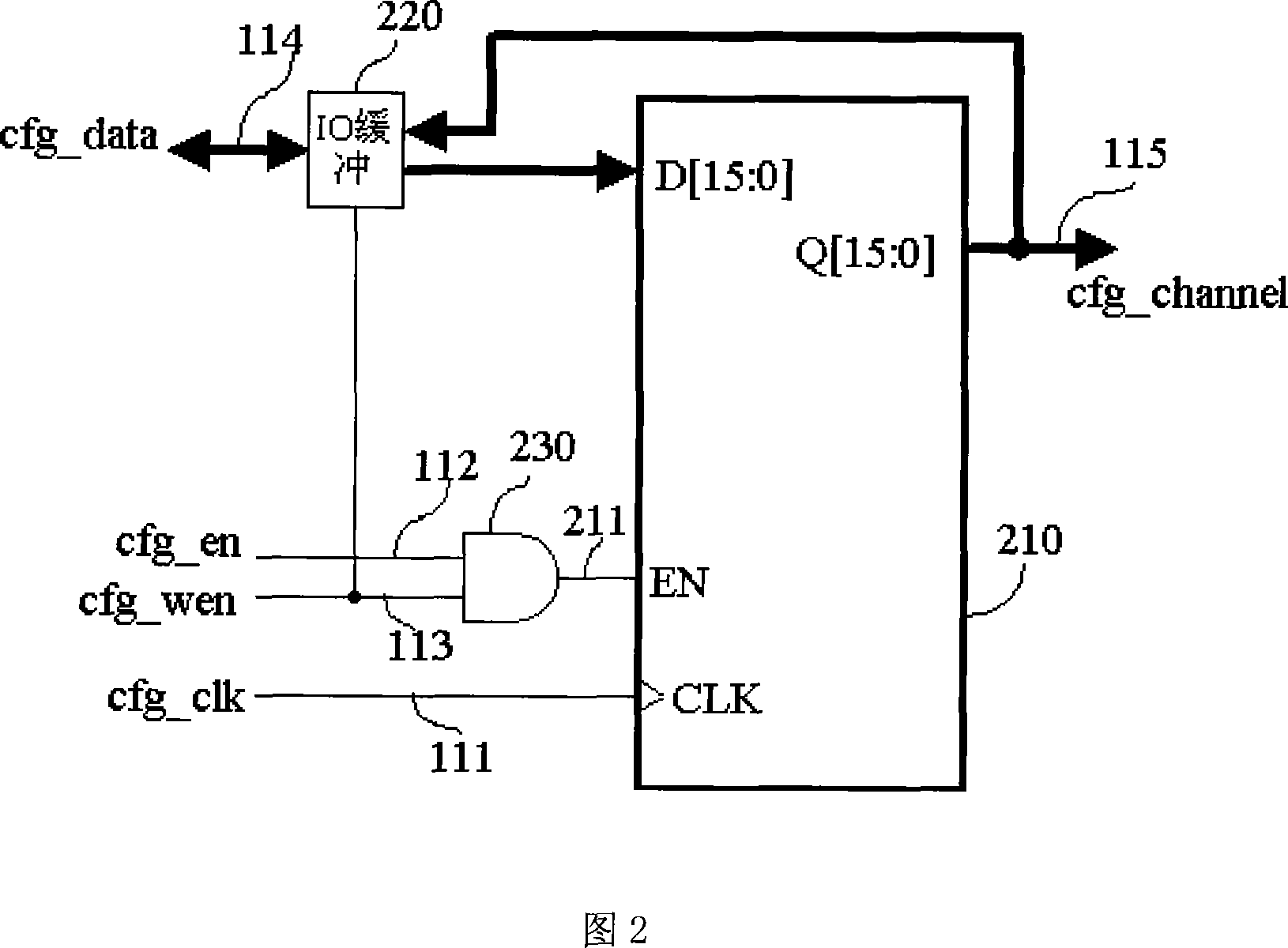

Method used

Image

Examples

Embodiment Construction

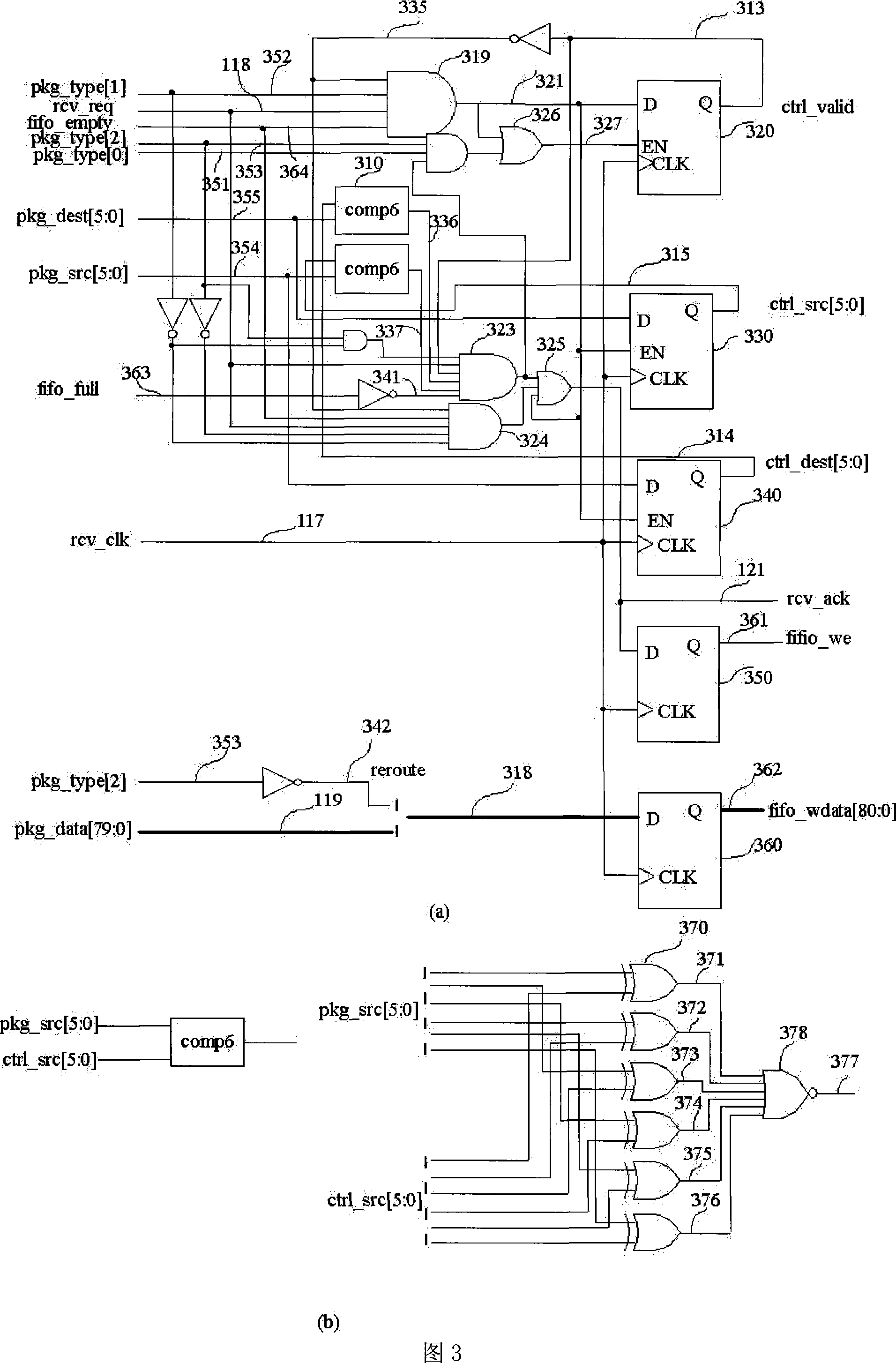

[0033]The smallest unit transmitted by the router of the present invention is a flit (Flit), and the flit is composed of header information (Header) and payload (Payload). After receiving the microchip, the router will analyze and process the header information, and perform routing and forwarding according to the corresponding content, while directly forwarding the payload without extracting information. The length of the header information is 16 bits, and its content is shown in Table 1. It currently uses 6-bit space encoding addresses to support 64-node on-chip networks, and it can be extended to support networks with more nodes (128, 256, or 512). Table 2 lists the encoding of the microchip type. The payload length can be configured as required, usually 64 or 128 bits.

[0034] Table 1

[0035] 15-12

11-6

5-0

microchip type

Chip Destination Address

microchip source address

[0036] Tabl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More